集成电路有机基板倒装焊失效分析与改善

2024-03-11朱国灵韩星徐小明季振凯

朱国灵,韩星,徐小明,季振凯

(无锡中微亿芯有限公司,江苏无锡 214072)

0 引言

随着物联网、人工智能等新兴技术的快速发展,电子产品对便携性、多功能性的需求日益迫切,芯片设计朝着多功能和大规模集成的方向发展,并且塑封集成电路具有成本低、重量轻和易制造等优点,因此,大尺寸、高密度的塑封倒装焊技术被广泛应用于各类电子产品中[1]。然而,在封装、组装和使用过程中,集成电路往往需要经历多次温度变化和热冲击,不同材料的热膨胀系数(CTE)不同会引发热失配,导致电路在温度循环试验、回流焊时易发生互联凸点开路失效,进而影响封装可靠性[2]。行业技术人员对倒装焊凸点结构的可靠性和失效模式进行了研究。田野采用有限元分析法,发现热冲击会影响凸点的应力应变分布和互连可靠性[3]。高娜燕等人通过优化倒装塑封体结构中的芯片厚度、基板厚度和CTE 等参数,有效控制了封装翘曲度[4]。ZHU 等人通过试验方法研究了凸点在电流应力作用下的失效机制[5]。黄春跃等人通过对凸点形态进行热循环应力应变分析,研究了凸点与疲劳寿命之间的关系[6]。现阶段针对封装制程改善措施的相关研究比较缺乏。

本文针对某款间距为1.00 mm 的FC-PBGA900型FPGA 封装电路,利用Ansys Workbench 软件依照实体封装结构进行1∶1 建模,模拟其在温度循环和回流焊过程中的应力应变状态,分析失效原因并提出针对封装制程的改善措施,为大尺寸、高密度的塑封倒装焊提供重要的理论支撑和制程改善方案。

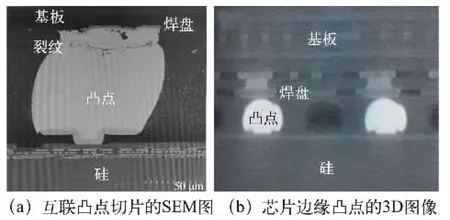

1 失效案例分析

FC-PBGA900 型FPGA 封装电路是一款集成了高速解串器、存储器和普通信号接口的大规模集成电路,其裸芯片尺寸为11.20 mm×16.70 mm×0.75 mm,封装尺寸为31.00 mm×31.00 mm×3.20 mm,散热片尺寸为30.60 mm×30.60 mm×1.35 mm。封装200 颗电路,其中良品为154 颗,封装良率为77%,抽取80 颗电路进行温度循环试验,试验温度为-65~150 ℃,循环500 次后,19 颗电路发生开路失效,失效率为23.75%。对失效电路进行分析,结果表明,发生失效的封装电路的凸点与基板间存在明显的贯穿式裂纹,图1(a)为失效封装电路互联凸点切片的SEM 图,失效封装电路的芯片边缘凸点与焊盘无接触,图1(b)为失效封装电路的芯片边缘凸点的3D 图像。裂纹产生的原因为温度循环时凸点受到的应力大于其材料可承受的蠕变或材料剪切强度。这些裂纹可能会导致凸点和基板出现明显的位置偏移。在温度循环试验中有机基板的形变最明显,较大的形变会影响芯片边缘凸点与焊盘的互联,从而导致虚焊或漏焊的情况。在进行封装制程和可靠性试验时,温度循环和回流焊过程中的高低温变化容易导致基板翘曲和凸点内应力的加剧以及材料蠕变,进而导致电路失效。为了提高该款封装电路的可靠性和稳定性,应当采取措施控制基板翘曲并降低凸点所受应力。

图1 失效封装电路互联凸点切片SEM 图和芯片边缘凸点3D 图像

2 有限元仿真分析

2.1 温度循环试验建模与仿真分析

温度循环试验的目的是考察封装电路在长时间冷热温度交变作用下的性能表现,特别是热应力对其产生的影响。

2.1.1 温度循环试验建模

模型参数如表1 所示,使用Ansys Workbench 软件按照电路结构进行1∶1 建模,采用四面体和六面体相结合的方式进行网格划分,温度循环试验的仿真模型如图2 所示。在仿真参数设置时,需要限制凸点底端自由度,将温度设置为-65~150 ℃,零应力温度点为25 ℃,循环次数为500 次,温度转换时间不超过1 min,停留时间不少于10 min。

表1 模型参数

图2 温度循环试验的仿真模型

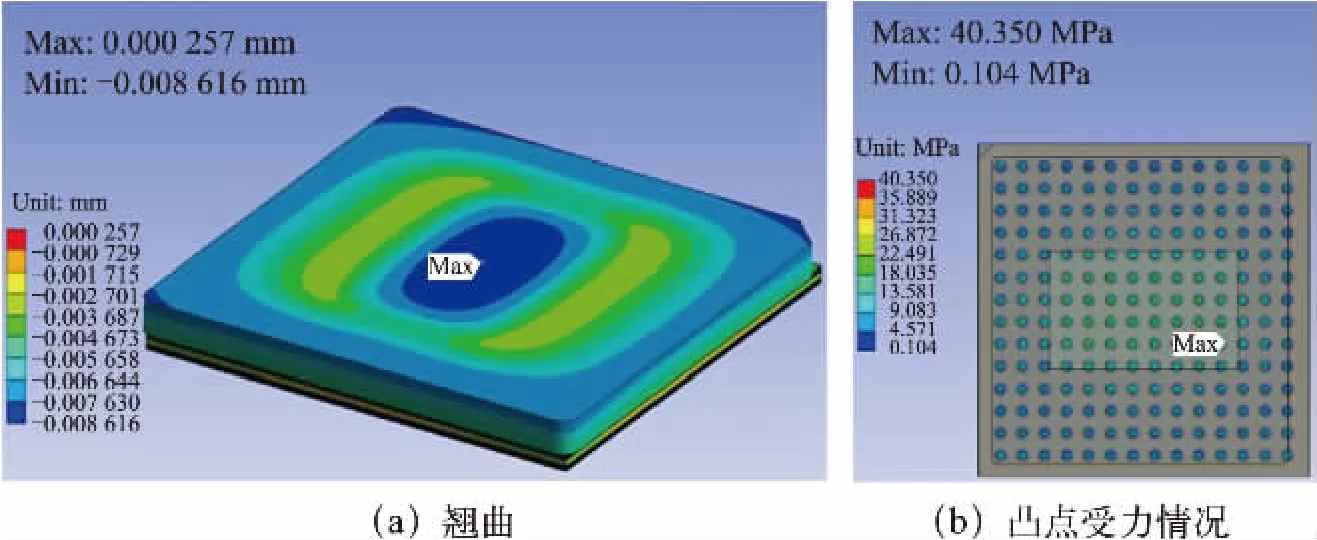

2.1.2 温度循环试验仿真结果与分析

降温阶段的温度为25~-65 ℃,降温阶段基板翘曲和凸点受力情况如图3 所示。由图3(a)可知,基板发生了正向翘曲,相较于中心位置,边缘位置的形变量较大,整体呈现出“笑脸”形状,翘曲最大值约为0.009 mm。图3(b)中箭头指向位置为凸点受应力影响最显著位置,降温阶段芯片边缘位置的凸点受力最大,应力最大值为40.350 MPa。随着循环次数的增多,残余应力不断累加,凸点易因疲劳产生失效。

图3 降温阶段基板翘曲和凸点受力情况

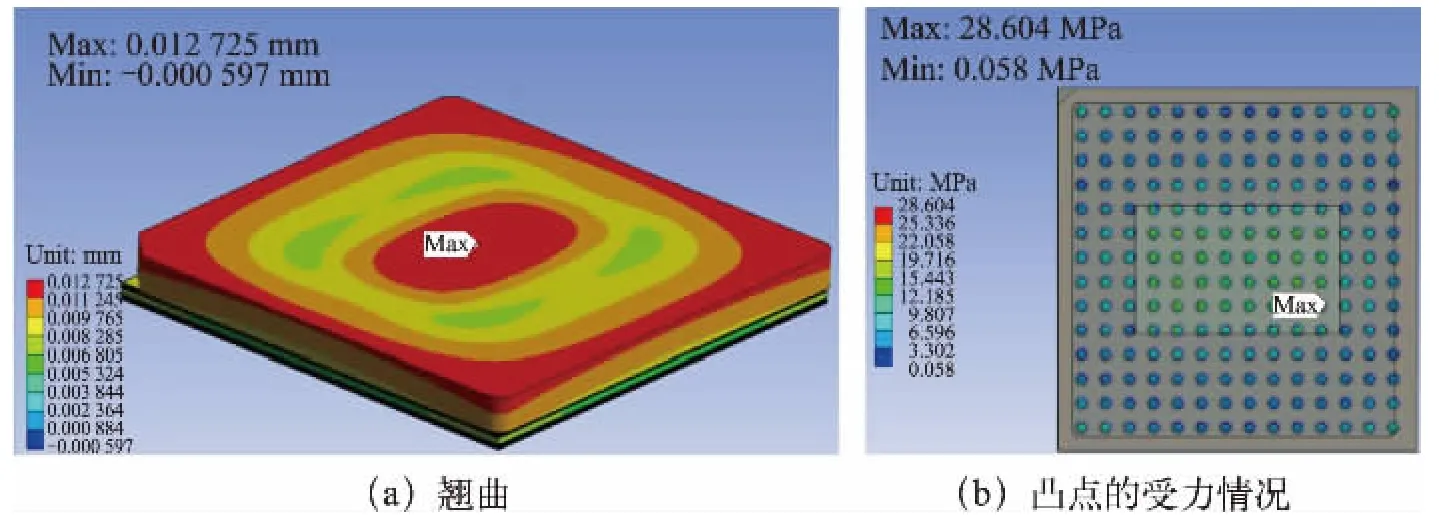

升温阶段的温度为25~150 ℃,升温阶段基板翘曲和凸点受力情况如图4 所示。由图4(a)可知,基板发生了负向翘曲,相较于中心位置,边缘位置的形变量较大,整体呈现出“哭脸”形状,翘曲最大值约为0.013 mm。图4(b)中箭头指向位置为凸点受应力影响最显著位置,升温阶段的凸点受力最大的位置也在芯片边缘,应力最大值为28.604 MPa。

图4 升温阶段基板翘曲和凸点受力情况

仿真结果显示,升温和降温阶段的翘曲现象呈现出相似的趋势,形变量从基板的中心位置向边缘位置逐渐增大,且凸点的最大受力位置均在芯片边缘,但降温阶段的等效应力约为升温阶段的1.4 倍,在降温阶段凸点更容易因为疲劳发生断裂失效,芯片边缘位置是最容易发生失效的区域。因此,通过控制基板翘曲、减少凸点损伤和降低残余热应力等方式增强凸点焊接强度才是解决凸点失效的根本途径。

2.2 回流焊建模与仿真分析

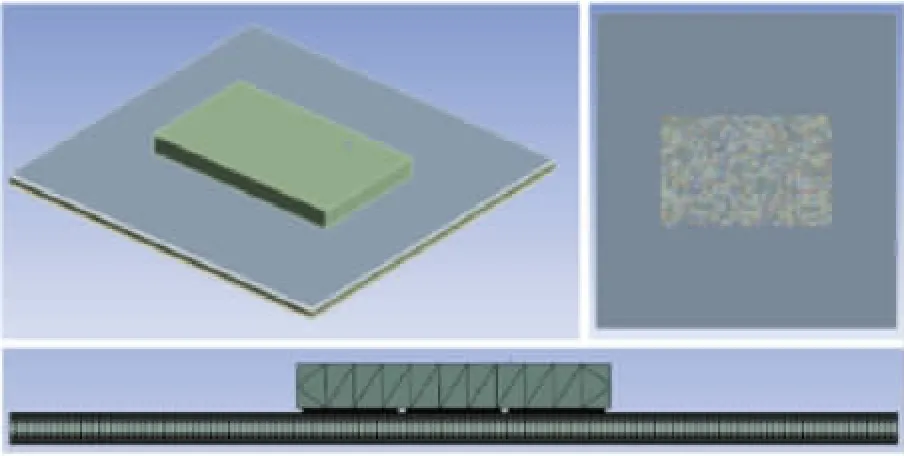

2.2.1 回流焊建模

在封装制程中最易造成凸点失效的工序为回流焊,高低温变化容易导致凸点蠕变和内应力产生,进而引发失效。回流焊过程与温度循环试验类似,分为升温阶段和降温阶段,温度循环仿真结果显示,在降温阶段凸点更易发生失效,因此在回流焊过程中主要针对降温阶段进行仿真。采用与温度循环试验相同的模型,建模和网格划分方式均与温度循环建模时的方式保持一致,回流焊过程的仿真模型如图5 所示。在仿真参数设置时,需要限制基板自由度,凸点材料为SnAg1.8,其熔点为221 ℃,因此将温度设置为220~25 ℃,零应力温度点为25 ℃,降温速率为0.8 ℃/min。

图5 回流焊过程的仿真模型

2.2.2 回流焊仿真结果与分析

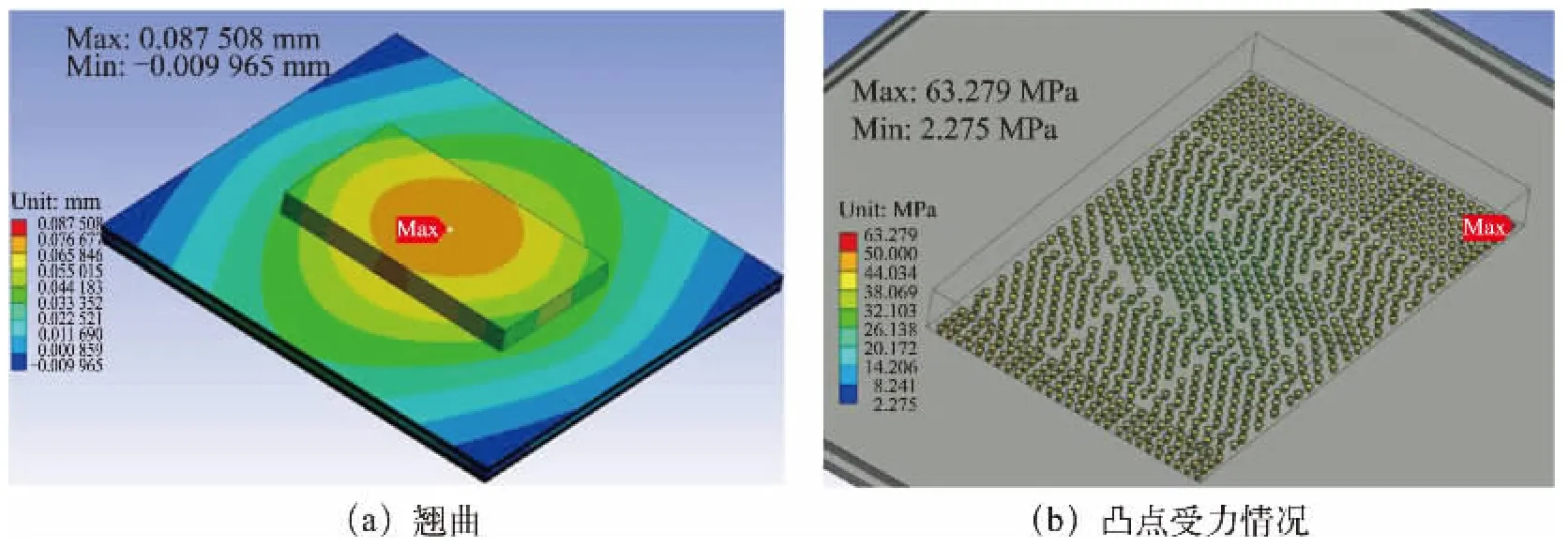

回流焊降温阶段基板翘曲和凸点受力情况如图6所示,由图6(a)可知,基板发生了负向翘曲,形变量由中心位置向边缘位置逐渐增大,整体呈现出“哭脸”形状,翘曲最大值约为0.097 mm。图6(b)中箭头指示的位置为凸点最易发生失效的位置,芯片边缘位置的凸点受力最大,应力最大值约为63.28 MPa。上述结果表明,在回流焊降温阶段,基板翘曲导致凸点向外倾斜,且边缘位置的凸点倾斜度最大,芯片边缘位置的凸点所受应力最大,该位置凸点受到的应力接近凸点强度极限,易造成凸点断裂失效。

图6 回流焊降温阶段基板翘曲和凸点受力情况

3 改善措施

结合温度循环试验和回流焊仿真结果可以看出,基板边缘位置的翘曲最大,芯片边缘位置的凸点受力最大,芯片边缘位置为最易发生凸点失效的位置。温度循环试验作为一种检验封装结构稳定性的方法,其主要目的是剔除失效样品。控制回流焊阶段的基板翘曲并提高凸点与焊盘结合强度可以有效降低焊接风险。

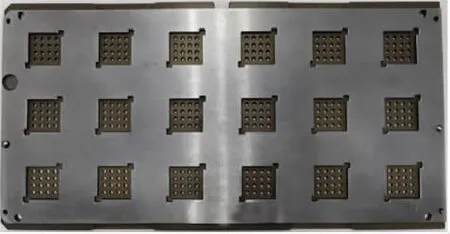

3.1 磁性载具

利用物理压合技术施加外部压力可以有效控制基板在回流焊过程中的翘曲。本文采用的磁性载具如图7 所示,载具为钢制框架结构,分为上模和下模2 个部分,总厚度约为4.2 mm。将基板置于凹槽内并固定,可有效降低装片后的基板在回流焊时的翘曲,确保凸点与焊盘充分焊接,避免虚焊和漏焊发生。

图7 磁性载具

3.2 预制焊料

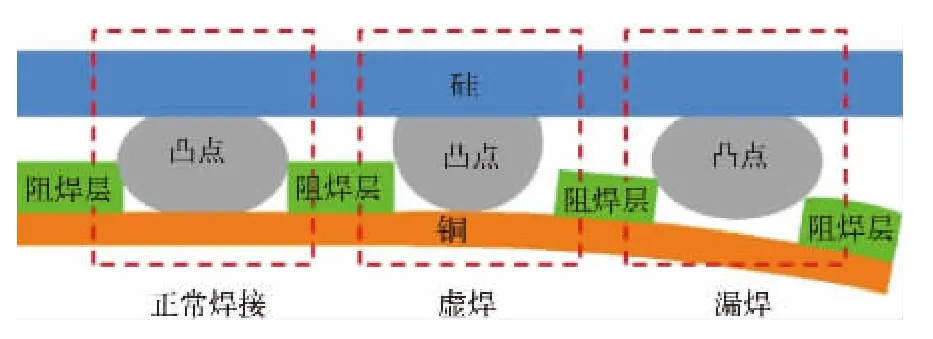

针对同一款封装电路,在其他条件相同的前提下,凸点的焊接强度主要取决于其与焊盘的有效焊接面积,有效焊接面积越大,焊接强度越高。采用在焊盘上预制焊料的方法可显著提高凸点与焊盘的有效焊接面积,从而提高焊接强度,增强凸点在回流焊阶段的焊接稳定性,没有预制焊料和在焊盘上预制焊料的倒装焊流程如图8 所示。采用该方法可有效避免虚焊和漏焊,在实际加工时凸点直径存在±10%的公差,阻焊层开窗尺寸存在±15 μm 的公差,当绿油开窗偏公差下限或凸点直径偏公差上限时,基板翘曲可能会导致凸点与焊盘无法接触或接触面积过小,凸点出现虚焊或漏焊的情况,正常焊接的凸点与虚焊、漏焊的凸点对比如图9 所示。

图8 倒装焊流程

图9 正常焊接的凸点与虚焊、漏焊的凸点对比

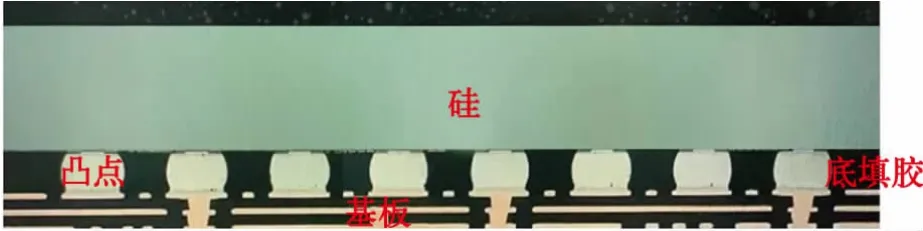

采用磁性载具和预制焊料的方法对封装制程进行优化,重新封装200 颗FC-PBGA900 型FPGA 电路,良品为197 颗,封装良率由77%提升至98.5%。在-65~150 ℃下,电路经过500 次温度循环后没有出现电性能异常和开路失效,优化后封装电路的凸点切片如图10 所示。由图10 可知,凸点焊接完整、形状标准,凸点与基板的相对位置稳定,没有发生明显的偏移,基板无明显翘曲。

图10 优化后封装电路的凸点切片

4 结论

采用Ansys Workbench 软件模拟FC-PBGA900 电路在温度循环和回流焊阶段的应力应变分布和翘曲情况,结果表明,温度循环是一种有效的检验封装电路质量的方法,每次循环产生的应力应变相对固定,改善异常的根本措施是通过优化封装制程,降低基板翘曲并提高凸点与基板的结合强度。可采取以下具体措施。

1)使用磁性载具以降低回流焊阶段的基板翘曲。

2)采用在芯片倒装区域预制焊料的方法,增强凸点与焊盘的结合力,避免凸点出现虚焊或漏焊情况。

集成电路的封装质量和可靠性不仅与有机基板有关,还与封装制程的工艺方法、工艺控制等因素密切相关,因此需要从全过程的角度来审视有机基板封装的集成电路的质量和可靠性。