万兆网卡设计中PCIE 4.0接口信号完整性仿真分析

2023-01-02李开杰林凡淼郁文君

李开杰,林凡淼,郁文君,张 恒

(中科芯集成电路有限公司,江苏 无锡 214072)

1 引言

集成电路的迅猛发展导致信号上升时间减少,时钟频率增加,进而出现信号不完整的现象,此现象带来的严重后果是电路不能正常工作[1]。为了消除此现象,国内外相关领域的专家纷纷致力于研究信号完整性问题[2-7]。

从PCIE 1.0到现在的PCIE 5.0,总线频率和传输速率在成倍增加,因此信号在传输的过程中会出现信号不完整的现象[8]。为了解决此问题,国内外学者进行了一系列的研究。文献[9]利用仿真软件Allegro Sigrity对PCIE 2.0差分信号进行时域分析,得到其眼图,根据输入眼图与输出眼图的差异来判断PCIE 2.0差分信号的质量,此仿真分析方法的缺点是只单纯地对PCIE差分信号进行时域分析,而且输入、输出眼图之间的差异容限范围也没有评判标准,因此得到的仿真结果可靠性较低。文献[10]利用仿真软件Hyperlynx对PCIE 2.0信号进行时域与频域分析,得到回波损耗、插入损耗和眼图,通过与协议规范的对比来评判PCIE的信号质量,此仿真分析方法能较好地评判出PCIE的信号质量,但是没有考虑到PCIE信号更长链路时的传输情况,因此得到的结果可靠性并不高。针对以上问题,本文提出了一种新的PCIE 4.0信号完整性仿真分析方法,建立了万兆网卡PCB×4 PCIE 4.0信号通道链路模型,考虑到PCIE信号更长链路时的传输情况,在原有的时、频域分析的基础上又添加了回环分析,提高了仿真结果的可靠性。

2 万兆网卡的设计方案

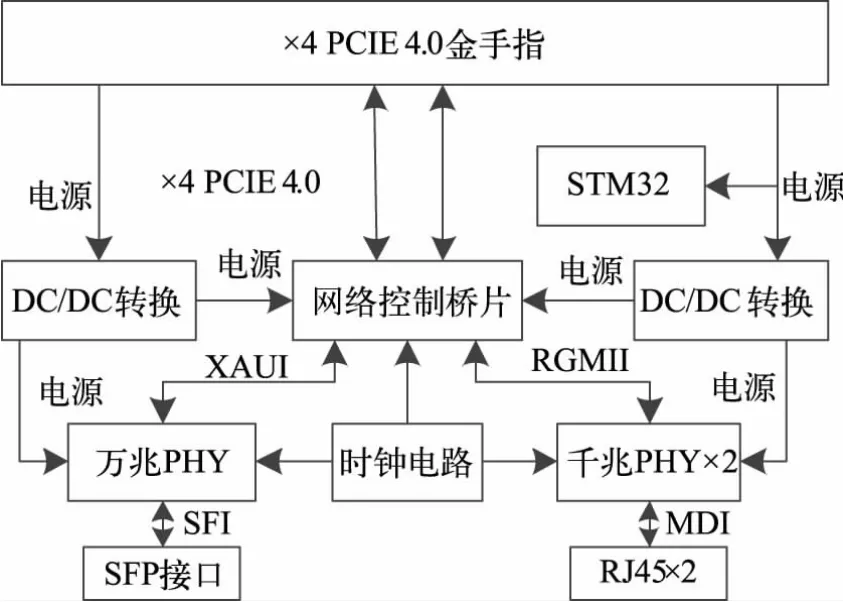

本文提出的万兆网卡硬件整体架构如图1所示,它主要由网络控制桥片、电源模块、时钟电路、万兆PHY模块、千兆PHY模块组成。其中,网络控制桥片采用Intel公司的E810XXVDA,万兆PHY采用Microsemi公司的VSC8486,千兆PHY采用Marvell公司的88E1111。该网卡通过PCIE接口实现网口的扩展功能。

图1 万兆网卡硬件整体架构

3 接收端和信道的设计要求

从PCIE 4.0协议规范[11]可知,其接收端和信道需符合一定的设计要求。

3.1 接收端的设计要求

PCIE高速串行信号从发送端发送,经过信道到达接收端,在此过程中信号会有一定的衰减,进而会发生失真现象。对于接收端信号质量的鉴定方法有2种。第一种是传统时域瞬态仿真法,该方法的缺点是仿真速度慢、精度低和可靠性差;第二种方法是统计眼图法[12],该方法的优点是仿真速度快、精度高和可靠性高。经综合考虑,本文采用第二种方法来鉴定接收端的信号质量。眼图有2个参数,分别为眼宽和眼高,只有满足最低的眼宽和眼高,该信号才可通过,否则不可通过。PCIE 4.0协议规范规定接收端信号眼图的眼宽至少为0.3 UI,眼高至少为15 mV,当满足以上2个条件时,接收端的PCIE信号质量才合格,反之则不合格。时域仿真中得到的信号眼图都以这2个参数为评判标准,判断接收端PCIE信号质量是否合格。

3.2 信道的设计要求

高速信号在信道中传输因受反射、衰减等的影响,会有一定损耗[13]。由反射所导致的损耗称为回波损耗,由衰减所导致的损耗称为插入损耗[14]。在信号的传输中,由于阻抗不连续,导致反射现象出现,反射会导致信号失真,表现方式为振铃、上冲和下冲等。衰减现象的出现会导致信号质量退化,表现方式为信号上升沿退化和幅度降低等。回波损耗一般用S11表示,插入损耗用S21表示,S11越小,说明信号在阻抗不连续点反射得越少,即有用的信号反射越少,S21越大,说明有用的信号在接收端保留得越多,即有用的信号衰减越少。PCIE 4.0协议规范对回波损耗和插入损耗的要求如表1所示。频域仿真中得到的回波损耗和插入损耗都以表1中的值为评判标准,来判断信道中PCIE信号质量是否合格。

表1 PCIE 4.0协议规范对2种损耗的要求

4 PCIE 4.0接口信号完整性仿真分析

PCIE 4.0信号传输速率为16 Gbit/s,基本频率为8 GHz,因此对于该信号的布线不能再像低速信号布线那么随意,需进行信号完整性仿真分析。本文主要对万兆网卡PCB的PCIE 4.0信号走线进行信号完整性仿真分析。

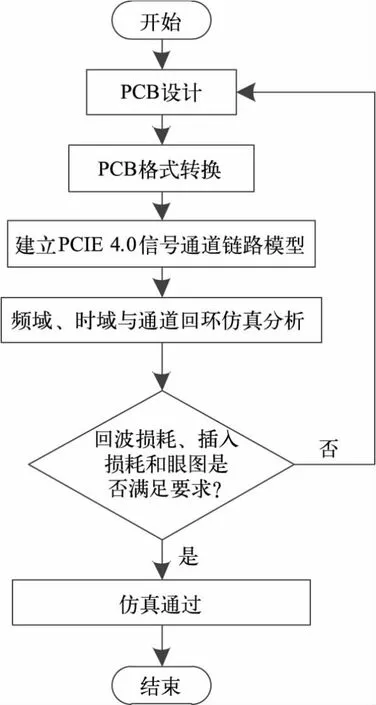

4.1 仿真分析流程设计

设计的PCIE 4.0接口信号完整性仿真分析流程如图2所示。首先,将初步设计的PCB用Allegro Sigrity中的SPDLinks转换程序转换成SPD文件;然后,将转换后的SPD文件导入到仿真软件POWERSI中,建立×4 PCIE 4.0信号通道链路模型,通过仿真得到该模型的S参数;接着将得到的S参数导入到ADS软件中进行频域、时域与通道回环仿真分析,得到回波损耗、插入损耗和眼图;最后,根据PCIE 4.0协议规范来判断其是否满足要求,若满足要求则仿真通过,否则仿真不通过。

图2 仿真分析流程设计

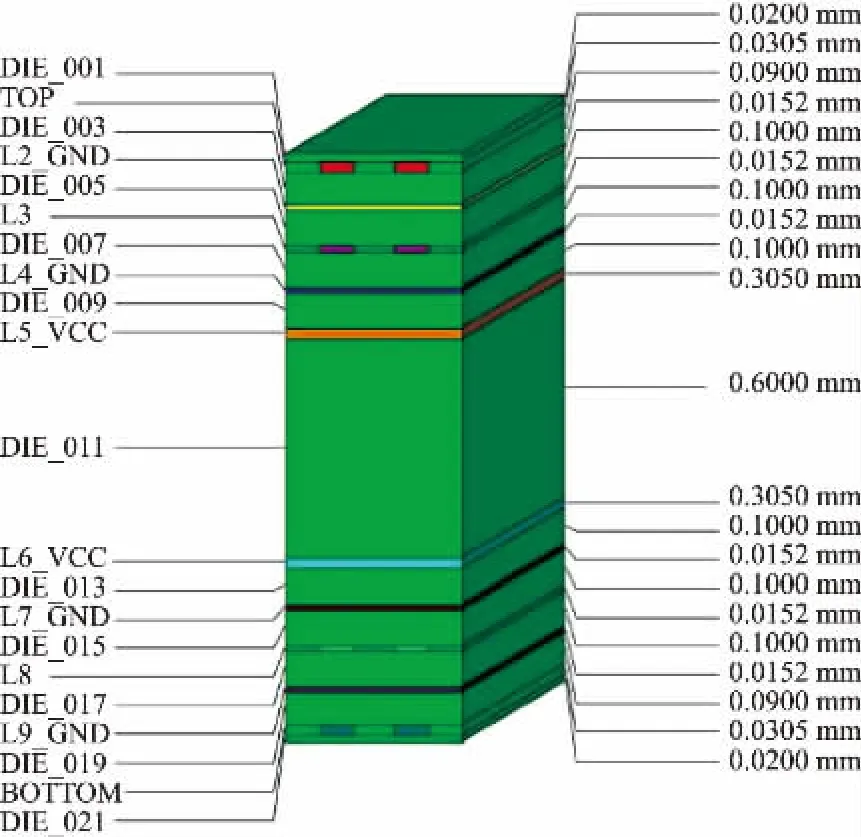

4.2 PCB叠层结构

万兆网卡PCB的叠层结构如图3所示,其总层数有10层。其中,信号层有4层,分别为TOP、L3、L8和BOTTOM。地层层数有4层,分别为L2、L4、L7和L9。电源层为2层,分别为L5和L6。线宽为0.127 mm,线间距为0.254 mm,总厚度为1.63 mm。PCB叠层结构主要是根据PCB工程师丰富的工作经验进行设计。

对于环境要素(见图1),事件e2的发生地点同时也是事件e3和事件e4的发生地点,这时就要在事件e2的环境要素属性lid中进行标注.

图3 万兆网卡PCB的叠层结构

信号层TOP和BOTTOM的参考平面层分别为L2和L9,信号层L3和L8上、下都有2个地层作为其参考平面层,这样设计的目的是为了让信号层有很好的抗电磁干扰能力,减少串扰的影响,而且由于其拥有完整的参考平面,也可以减少反射的发生。由于万兆网卡的高速信号较多,这样的叠层结构是很有必要的。

4.3 PCIE 4.0信号通道链路模型的建立

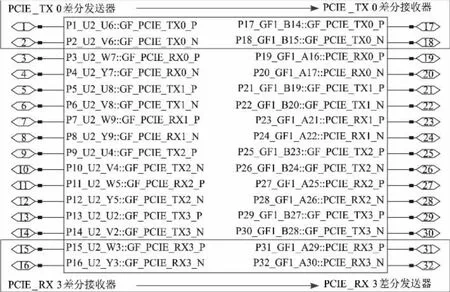

将格式转换后的万兆网卡PCB导入到Allegro Sigrity的POWERSI中,并定义其×4 PCIE 4.0信号通道(见图4)。PCIE 4.0差分信号共有8对,分别为TX0、TX1、TX2、TX3、RX0、RX1、RX2和RX3,它们从桥片直接引到金手指上。

图4 ×4 PCIE 4.0信号通道

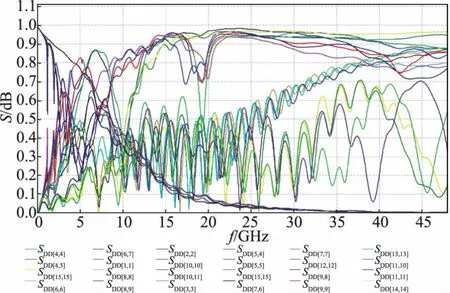

信号通道定义完成后,通过设置扫频参数(扫频范围一般为信号速率的3倍,因为PCIE 4.0信号传输速率为16 Gbit/s,所以扫频范围为0~48 GHz),可得到模型的S参数,×4 PCIE 4.0信号通道S参数如图5所示(限于篇幅,只示出了部分S参数)。该S参数描述了8对PCIE差分信号在其通道中的行为,以便后续进行时、频域仿真。将得到的S参数导入到ADS中,显示其通道链路模型,×4 PCIE 4.0信号通道链路模型如图6所示。图6中模型左侧是连接网络控制桥片的端口,右侧是连接金手指的端口。为了保证仿真的有效性,本文的仿真设定均参照相关专业书籍[15]。

图5 ×4 PCIE 4.0信号通道S参数

图6 ×4 PCIE 4.0信号通道链路模型

4.4 频域仿真分析

×4 PCIE 4.0信号通道链路模型建立完成后,就可以进行时、频域仿真分析。在ADS软件中搭建频域仿真模型,如图7所示。因为PCIE 4.0差分信号阻抗为85Ω,单端阻抗为42.5Ω,所以在通道模型每个端口连接一个42.5Ω的阻抗。设置仿真参数:起始频率为0 GHz,截止频率为48 GHz,频率步进为1 GHz(频率范围和扫频范围一致)。

图7 频域仿真模型

由于需要得到8对PCIE差分信号的回波损耗和插入损耗,还需要知道其计算公式,回波损耗和插入损耗的计算公式[16]如式(1)~(4)所示(以PCIE_TX0为例进行说明,另外7对PCIE差分信号的回波损耗和插入损耗计算方法相同)。

在式(1)~(4)中,A表示PCIE_TX0的左端口,B表示PCIE_TX0的右端口,SDD-AA和SDD-BB表示差分信号PCIE_TX0左、右端口的回波损耗。SDD-AB和SDD-BA表示差分信号PCIE_TX0左、右端口的插入损耗,一般来说它们相等。

频域仿真的回波损耗和插入损耗结果如图8、9所示。图8为8对PCIE 4.0差分信号左右端口的回波损耗,从图8中可知,在频率为50 MHz~1.25 GHz时,其回波损耗低于-10 dB,在频率为1.25~2.5 GHz时,其回波损耗低于-8 dB,在频率为2.5~8 GHz时,其回波损耗低于-6 dB,满足PCIE 4.0协议规范对回波损耗的设计要求。

图8 8对PCIE 4.0差分信号两端口回波损耗

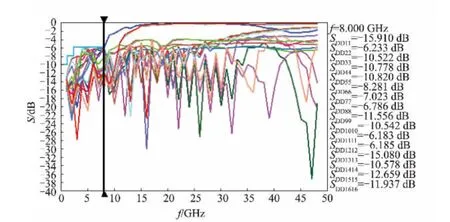

图9为8对PCIE 4.0差分信号左、右端口的插入损耗,从图9可知,在频率为8 GHz时,其插入损耗高于-28 dB,满足PCIE 4.0协议规范对插入损耗的设计要求。

图9 8对PCIE 4.0差分信号两端口插入损耗

由以上分析可知,8对PCIE 4.0差分信号在其通道中的信号质量是合格的。

4.5 时域仿真分析

在ADS中搭建时域仿真模型,如图10所示。在仿真模型中会运用到IBIS-AMI模型,该模型是由美国国家标准协会制定的,专门应用在信号完整性仿真中[17]。

图10 时域仿真模型

在搭建的时域仿真模型中,有应用到网络控制桥片的IBIS-AMI模型,该模型里包含很多子模型,选择PCIE 4.0发送与接收子模型导入到TX AMI和RX AMI中,为了能把通道之间的串扰考虑进去,在其他通道的发送和接受端增加了Xtlk AMI模型,最后,设置其传输速率为16 Gbit/s。

PCIE_TX0的眼图如图11所示(限于篇幅只显示PCIE_TX0的仿真结果),从图11可知,眼图的眼高为112 mV,眼宽为0.59 UI,眼的睁开度较大,抖动较小,根据PCIE 4.0协议规范要求可知,眼图的眼高需大于15 mV,眼宽需大于0.3 UI,因此,从金手指端接收到的PCIE_TX0信号质量是合格的。其他7对PCIE 4.0信号时域的仿真结果如表2所示。

图11 PCIE_TX0的眼图

表2 PCIE 4.0信号时域仿真结果

从表2可知,其余7对PCIE 4.0信号眼图的眼高和眼宽均满足PCIE 4.0协议规范对接收端信号眼图的设计要求,即从接收端接收到的其余7对PCIE信号质量是合格的。

4.6 通道回环仿真分析

为了进一步模拟PCIE 4.0信号更长链路时的传输情况,本文对其进行了通道回环仿真分析,即将PCIE 4.0信号中对应的TX信号和RX信号做环路仿真。通道回环仿真又分为频域回环仿真和时域回环仿真。

4.6.1 频域回环仿真分析

在ADS中搭建频域回环仿真模型,如图12所示。由于TX信号和RX信号进行了环路传输,因此PCIE 4.0信号由原先的8个通道变成了4个通道。仿真参数与频域仿真参数相同,回波损耗和插入损耗的仿真结果分别如图13、14所示。

图12 频域回环仿真模型

从图13可知,SDD11和SDD22、SDD33和SDD44、SDD55和SDD66、SDD77和SDD88分别是TX0和RX0、TX1和RX1、TX2和RX2、TX3和RX3回环传输通道的两端回波损耗,它们在频率为50 MHz~1.25 GHz时,回波损耗低于-10 dB,在频率为1.25~2.5 GHz时,回波损耗低于-8 dB,在频率为2.5~8 GHz时,回波损耗低于-6 dB,满足PCIE 4.0协议规范对回波损耗的设计要求。从图13还可以发现,随着频率的升高,端口阻抗会越来越不匹配,导致回波损耗在高频处出现恶化。从图14中可知,SDD12和SDD21、SDD34和SDD43、SDD56和SDD65、SDD78和SDD87分别是TX0和RX0、TX1和RX1、TX2和RX2、TX3和RX3回环传输通道的两端插入损耗,在频率为8 GHz时,插入损耗高于-28 dB,满足PCIE 4.0协议规范对插入损耗的设计要求。从图14还可以发现,随着频率的升高,插入损耗越来越大,传输的有用信号越来越小。综上可知,4个回环通道中的PCIE差分信号质量是合格的。

图13 回波损耗仿真结果

图14 插入损耗仿真结果

4.6.2 时域回环仿真分析

在ADS中搭建时域回环仿真模型,如图15所示。限于篇幅,本文只显示TX0和RX0的时域回环仿真模型。仿真参数与时域仿真参数相同,仿真结果如图16~19所示。

图15 时域回环仿真模型

图16 信号TX0和RX0通道回环眼图

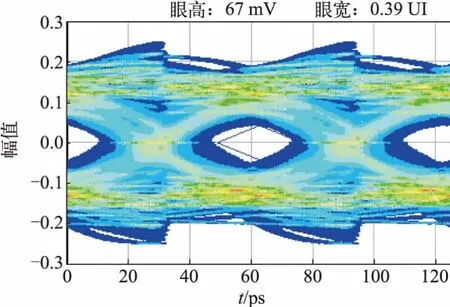

图17 信号TX1和RX1通道回环眼图

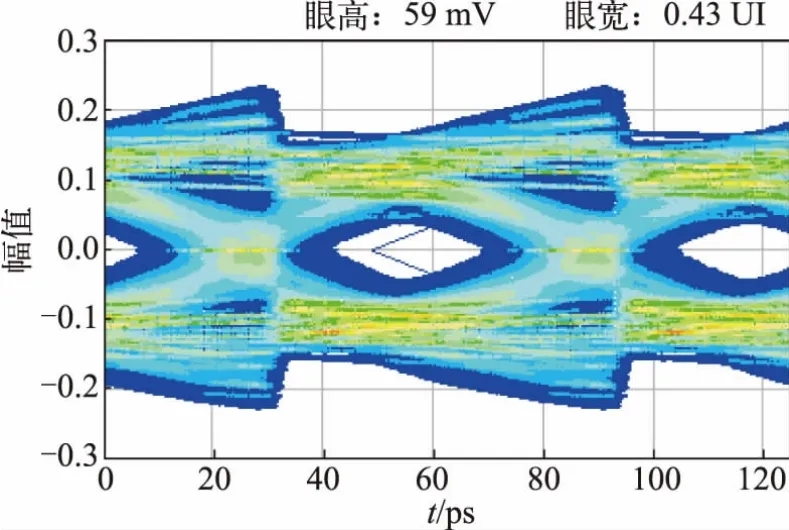

图18 信号TX2和RX2通道回环眼图

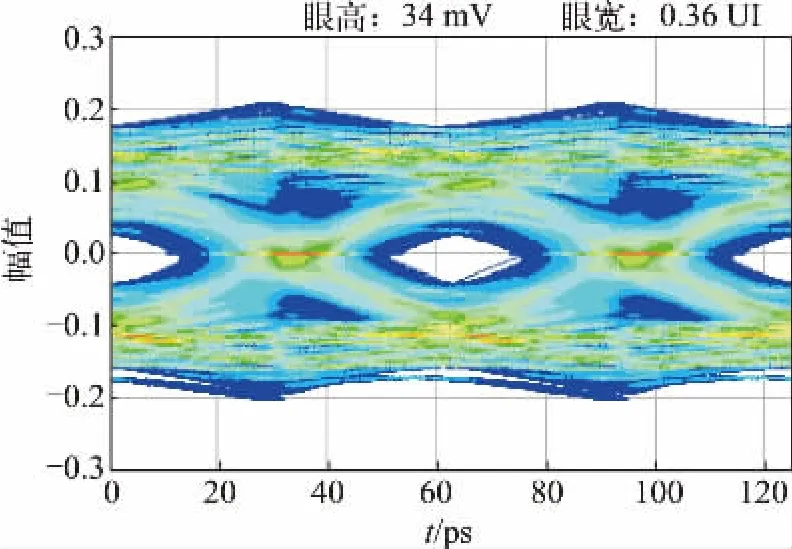

图19 信号TX3和RX3通道回环眼图

从图16~19可知,4个回环通道的眼图参数分别为眼高92 mV、眼宽0.61 UI,眼高67 mV、眼宽0.39 UI,眼高59 mV、眼宽0.43 UI,眼高34 mV、眼宽0.36 UI,从PCIE 4.0协议规范中可知,眼高需大于15 mV,眼宽需大于0.3 UI,因此4个回环通道的眼图均满足要求。进一步分析TX0和RX0回环通道的眼图,其眼宽和眼高均较大,抖动不明显,信号质量较好。其他3个回环通道的眼图,眼宽和眼高均较小,抖动较明显,可能是由于信号周围接地过孔过少,但是基本满足要求。由以上分析可知,4个回环通道的接收端PCIE信号质量是合格的。

5 结论

本文利用Allegro Sigrity和ADS仿真软件对万兆网卡中的PCIE 4.0信号进行信号完整性仿真分析。由时域、频域和回环仿真分析可知,万兆网卡PCB中的×4 PCIE 4.0信号走线满足设计要求。由此可见,本文提出的仿真分析方法可验证所设计的PCB是否符合设计要求,进而能缩短研发周期、减少成本并提高产品设计的成功率。