17~21 GHz 6 bit高精度数字移相器的设计

2023-01-02周宏健周睿涛李光超

蒋 乐,王 坤,周宏健,周睿涛,李光超

(中科芯集成电路有限公司,江苏 无锡 214072)

1 引言

单片微波集成电路(MMIC)作为微波/毫米波电路的主要发展方向,凭借低损耗、大功率、宽频带等优点,被广泛应用于军事和民用电子领域。其中,以GaAs衬底作为载体的MMIC,具有高阻尼系数和高电子迁移率等优点。移相器主要对微波信号的相位、传输路径等进行调整和控制,是相控阵雷达T/R收发组件的关键组成部分,其性能直接影响着整个系统的参数指标。因此,研究基于MMIC技术的数字移相器并使其性能不断朝着小型化、高精度、超宽带及低损耗的方向优化具有重要的意义[1-5]。

目前,市场上已存在一些相似频段的数字移相器,但是移相精度均方根相位误差(RMS)较高,均在2°以上,且芯片尺寸较大。本文基于0.15μm GaAs赝配高电子迁移率晶体管(PHEMT)工艺,研制了一款覆盖17~21 GHz的高精度6 bit MMIC数字移相器。其中,低位移相单元采用嵌入式LC及全通网络型拓扑结构,高位移相单元采用多阶高、低通网络拓扑结构,在保证移相度数的前提下充分提高了移相精度且缩小了芯片面积。实物测试结果显示,在工作频段内移相器的移相精度RMS均在2°以下,且其余性能指标优异。

2 数字移相器的设计

移相器网络为2端口,通过改变信号的传输相位实现移相。本文设计的6 bit数字移相器以5.625°为步进,6 bit独立移相单元由6个驱动单元分别控制,在0~360°之间实现64(26)种移相态。

2.1 开关器件建模

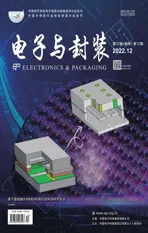

开关采用0.15μm GaAs工艺的PHEMT,PHEMT开关为3端口器件,通过控制栅极偏置电压实现源极和漏极之间的导通和截止,电性能优异。图1为开关器件等效电路模型图,为了减少泄露到栅极的射频信号,此处栅极到地电阻RG为3 kΩ。当开关导通时,等效电路可简化为小电阻;当开关截止时,等效电路可简化为电容。开关尺寸的大小会直接影响移相器的插入损耗及相移量,因此选取时需要综合考虑。

图1 开关器件等效模型

2.2 移相单元设计

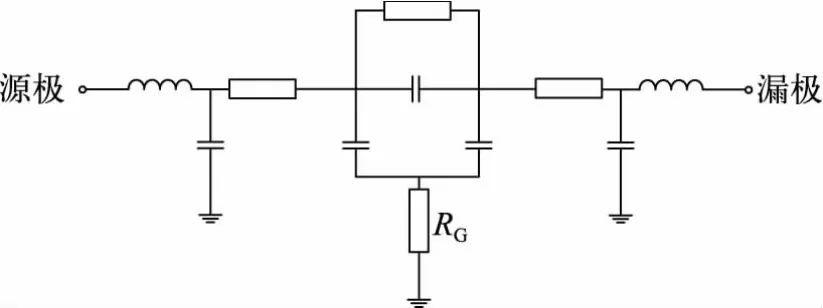

5.625 °移相单元采用了嵌入式LC结构,其电路拓扑结构如图2(a)所示,其中,Vc与Vc为开关互补控制电压(0/-5 V)。当开关M1导通、M2截止时,移相器处于参考态。此时,开关管M1的导通阻抗和微带Mlin1的阻抗相比非常小,开关管M2截止电容对应的阻抗相较于C1的阻抗可等效为开路,因此,参考态等效电路图可简化为图2(b)。当开关M1截止、M2导通时,移相器处于移相态,简化后移相态拓扑结构如图2(c)所示。该拓扑结构通过串联电容、电感产生插入相位,不仅可以实现较小的相移量,而且减少了电路的器件数量,缩小了芯片面积[6-7]。

图2 嵌入式LC拓扑结构

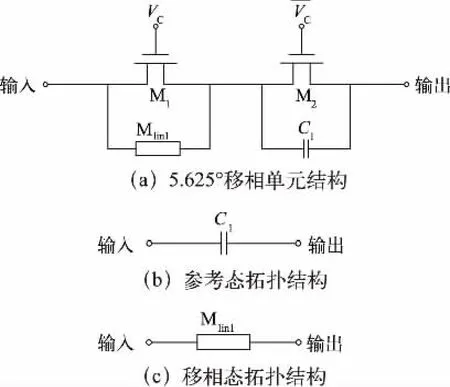

11.25°、22.5°移相单元采用了嵌入式全通网络拓扑结构,11.25°和22.5°移相单元结构如图3(a)所示。当开关M1、M2导通,M3截止时,电路处于带通参考态,参考态拓扑结构如图3(b)所示。其中,开关M3的截止电容C3和电感L2并联谐振,有利于电路的匹配。当开关M1、M2截止,M3导通时,电路处于全通移相态,移相拓扑结构如图3(c)所示。其中,开关M1的截止电容C1和电感L1构成全通滤波网络,不仅拓宽了带宽,而且具有低插入损耗;同时开关M2的截止电容C2和电阻R1并联,具有减小移相器寄生调幅、提高移相态隔离度的作用;最后,对电感、电容等变量进行优化,分别产生11.25°、22.5°的相移量。经过仿真及版图设计发现,该电路结构不仅减小了移相器寄生调幅、提高了移相精度,而且占用面积较小,适用于低位移相单元的设计[8-9]。

图3 嵌入式全通网络拓扑结构

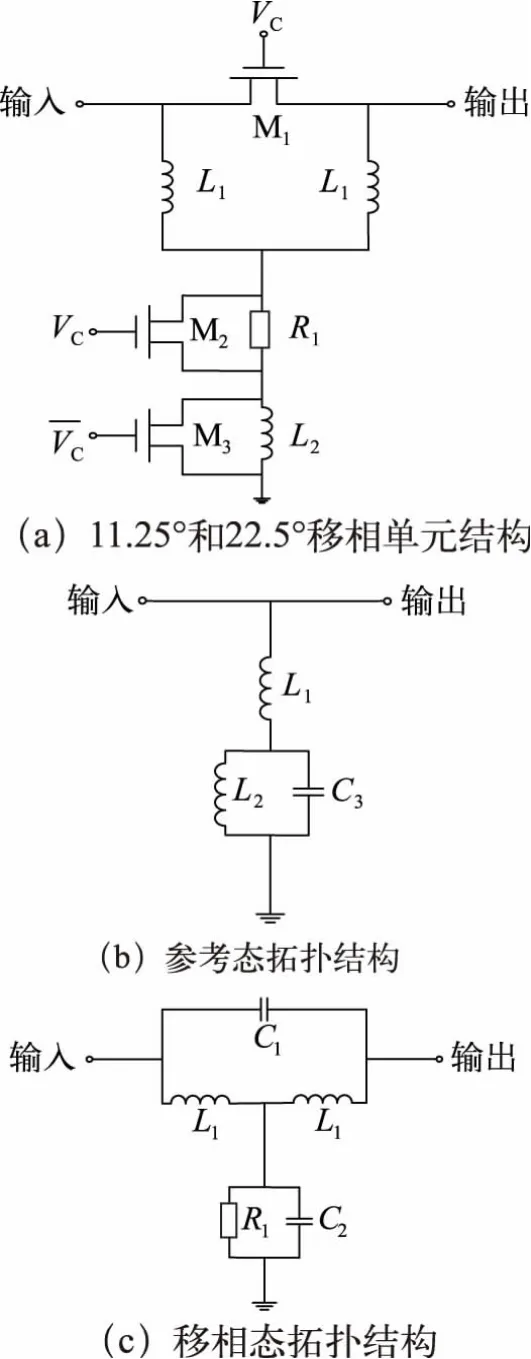

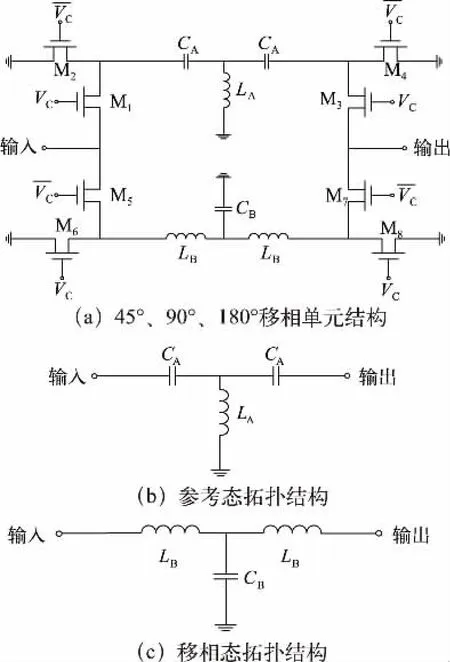

45°、90°、180°移相单元采用了开关选择型高、低通网络拓扑结构,45°、90°、180°移相单元结构如图4(a)所示。为了提高不同通路的隔离度,开关采用了多个开关串、并联结构。当开关M1、M6导通时,开关M2、M5截止,保证了微波信号从参考态通路传输,泄露到移相态的信号经过开关M6释放到地。该结构在实现移相器工作状态切换的前提下提高了开关的隔离度,同时具有较宽的工作带宽。

图4 开关选择型高、低通网络拓扑结构

当开关M1、M3、M6、M8导通,开关M2、M4、M5、M7截止时,移相器处于高通参考态,参考态拓扑结构如图4(b)所示。微波信号通过高通网络产生相位超前,且超前量随频率的升高而减少。当开关M2、M4、M5、M7导通,开关M1、M3、M6、M8截止时,移相器处于低通移相态,移相态拓扑结构如图4(c)所示。微波信号通过低通网络产生相位滞后,且滞后量随频率的升高而增加。通过优化滤波器阶数以及电感、电容数值大小得到所需要的相移量,同时不同通路相位随频率的变化状态互相补偿,保证了通频带内相位量的平坦度[10-14]。

设高、低通滤波网络传输相位分别为φA、φB,则T型高、低通滤波拓扑结构电感LA与LB、电容CA与CB设计初值分别为[15]:

式中,Z0为特性阻抗,ω为角频率。开关选择型高、低通网络结构产生的相移Δφ=φB-φA。

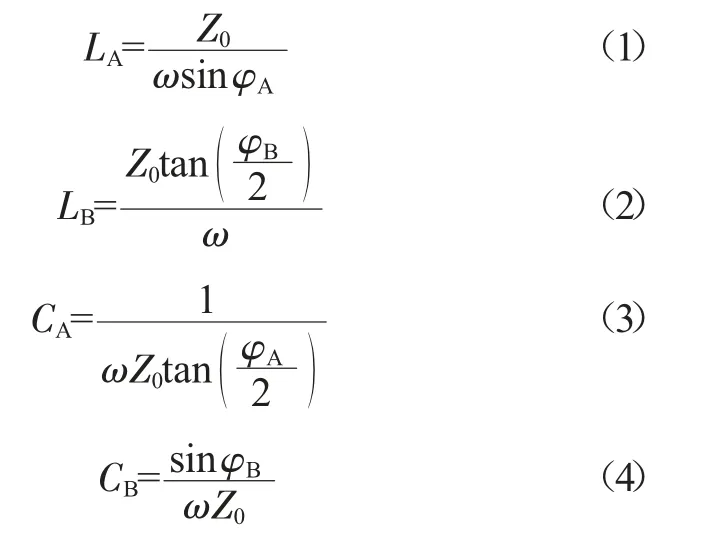

2.3 驱动电路设计

驱动电路主要将外部单路0 V/+5 V控制信号转换为内部0 V和-5 V 2路互补控制信号。本文设计的驱动电路基于直接耦合场效应晶体管逻辑(DCFL)结构,DCFL基本倒相单元如图5(a)所示。其中T1为耗尽型晶体管,作为负载管控制负载电流;T2为增强型晶体管[16],作为驱动管控制输入开关,控制电压VD为-5 V。

驱动电路结构由5级DCFL单元组成,5级驱动电路结构如图5(b)所示。当单路输入电平VI为高电平时,2路输出电平VO一路经过4级DCFL倒相器输出高电平VO1,一路经过3级DCFL倒相器输出低电平VO2。

图5 驱动电路结构

2.4 级联设计

完成每位移相单元的独立设计后,需要将6位移相单元进行级联仿真。将端口驻波较好的移相单元放在整体电路两侧,并综合考虑芯片布局、阻抗匹配等因素,6位数字移相器最优级联顺序依次为180°、22.5°、5.625°、11.25°、45°、90°。在此顺序下,移相器输入、输出驻波最优。移相器级联顺序如图6所示,其中,P0~P5对应移相器的6个主要移相态。

图6 移相器级联顺序

3 数字移相器的测试与结果分析

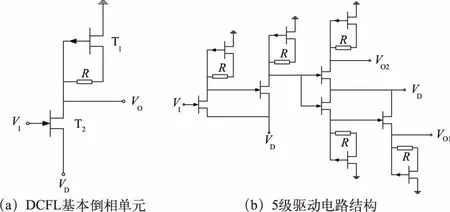

17~21 GHz 6 bit数字移相器实物如图7所示。芯片左侧为微波信号的输入端,右侧为微波信号的输出端,驱动控制电路位于上方。芯片尺寸为2.65 mm×1.2 mm×0.1 mm。

图7 移相器实物照片

微波测试环境如图8所示。在对测试线以及微波探针进行校准后,使用矢量网络分析仪、探针台等仪器对该数字移相器进行微波参数测试,得到移相器插入损耗、移相态RMS、输入/输出电压驻波比(VSWR)、64态相移及寄生调幅测试结果,如图9所示。

图8 移相器测试环境

图9 6 bit数字移相器测试结果

由测试结果可得,在17~21 GHz工作频段内,6 bit数字移相器插入损耗的绝对值小于8.5 dB,移相精度均方根小于2°,64态下输入VSWR小于1.4,输出VSWR小于1.5,64态相移曲线均匀分布,64态寄生调幅在-0.8~0.6 dB之间,满足移相器高精度设计的指标要求。

通过对比仿真和测试结果可知,移相器插入损耗实测值的绝对值比仿真值的绝对值大1 dB;移相态RMS在17~20.5 GHz频率范围内,实测值比仿真值大,20.5~21 GHz处实测值小于仿真值;其64态参数实测值与仿真值相差较小。经过初步分析,原因是寄生电阻的存在以及开关等器件模型与实际器件存在偏差,后续可以通过加宽仿真频率范围以及提高模型的提取精确度进行改善。

4 结论

基于0.15μm GaAs PHEMT工艺研制了一款17~21 GHz 6 bit高精度数字移相器。其中,5.625°移相单元采用嵌入式LC拓扑结构,11.25°、22.5°移相单元采用嵌入式全通网络拓扑结构,45°、90°、180°移相单元采用多阶高、低通网络拓扑结构。通过选择合适的低位移相单元结构及对高、低通滤波器阶数进行合理优化,最终实物测试时,移相器在工作频段内移相精度均方根均在2°以下且尺寸紧凑。测试结果显示,在17~21 GHz工作频率范围内,移相器的插入损耗的绝对值小于8.5 dB,输入VSWR小于1.4,输出VSWR小于1.5,移相精度均方根小于2°,寄生调幅在-0.8~0.6 dB之间,芯片尺寸为2.65 mm×1.2 mm×0.1 mm。该移相器的移相精度均方根及芯片尺寸均优于市面上同类型相似频段的数字移相器,且其余性能指标优良。