纳米器件单粒子瞬态仿真研究*

2022-08-01殷亚楠王玧真邱一武周昕杰

殷亚楠,王玧真,邱一武,周昕杰,郭 刚

(1.中国电子科技集团公司第五十八研究所,江苏无锡 214072;2.中国原子能科学研究院,北京 102413)

1 引言

在空间辐射环境中电子元器件会受到各种宇宙射线和粒子辐射的影响,其中单粒子效应(SEE)作为破坏性最为显著的一种辐射效应,已经成为学者们关注的重点。而随着航空航天电子元器件工作频率不断增加、工作电压不断降低、器件尺寸不断缩小,SEE 的影响也越来越大。尤其是到纳米特征尺寸以后,SEE已经成为影响电路可靠性的最关键因素之一[1-2]。

单粒子瞬态(SET)效应是SEE 最重要的子类之一,是入射粒子引起电流和电压的瞬时波动,主要发生在逻辑电路部分[3]。与时序逻辑电路中的单粒子翻转效应相比,组合逻辑电路中的软错误研究相对滞后,这是因为SET 效应在实验上难以观测,到20 世纪80 年代,针对组合逻辑电路中的SET 效应才逐渐引起人们的关注[4]。随着集成电路的不断发展,器件的工艺特征尺寸不断缩减,时钟频率在不断上升,使得由SET 导致的电路软错误数量逐渐呈现上升趋势。当特征尺寸达到纳米级别后,组合逻辑电路中SET 导致的软错误已经成为集成电路中软错误的主要来源[5-6]。而组合逻辑电路中的SET 效应随工艺尺寸的缩减将会越来越严重,在这方面开展相应的研究也愈发紧迫和重要,集成电路中SET 相关方面的研究已经成为当前SEE 研究中的热点和难点[7-10]。

本文利用Silvaco 公司的计算机辅助设计(TCAD)仿真软件,结合28 nm 体硅器件的工艺参数,建立了相应的器件模型,对不同参数下的器件SET 效应进行模拟仿真,分析不同条件下器件的电荷收集机制和影响范围,为利用电荷共享效应进行加固技术研究提供技术指导。

2 器件结构描述

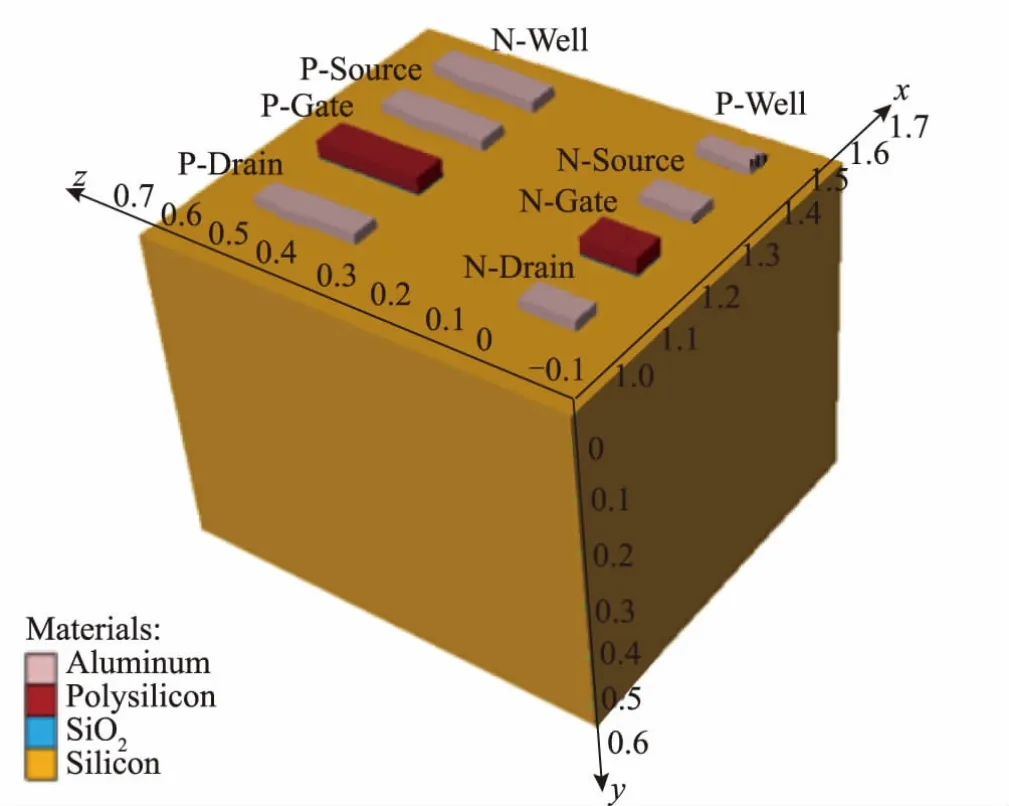

基于TCAD 仿真软件对28 nm 体硅器件进行建模,根据相应的器件参数构建了N 型金属-氧化物-半导体(NMOS)晶体管和P 型金属-氧化物-半导体(PMOS)晶体管模型,通过调整各项掺杂浓度,对器件进行校准,使其电特性与SPICE 模型基本一致。以此为基础,构建了反相器结构,TCAD 反相器模型如图1所示。其中NMOS 晶体管的W/L为100 nm/28 nm,PMOS 晶体管的W/L为200 nm/28 nm。

图1 TCAD 反相器模型

在仿真过程中,初始状态反相器的输入为0 V、输出为0.9 V,NMOS 晶体管PN 结反偏,处于关态,此时它的漏极是SEE 的敏感节点。仿真时重离子的轰击区域为NMOS 晶体管的漏极区域,重离子模型具有高斯分布特性,半径为50 nm,半衰时间指数为0.2 ps。

3 仿真结果与分析

3.1 不同间距的影响

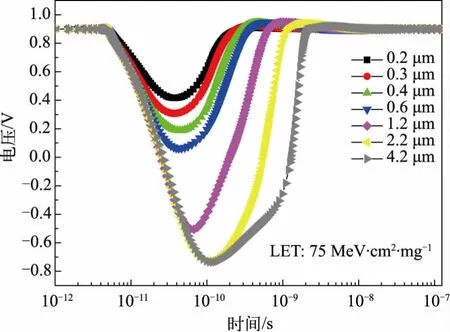

首先研究了不同器件间距下粒子在反相器中产生的SET。图2 是NMOS 漏极和PMOS 漏极之间的间距在0.2~4.2 μm 之间变化时,线状能量传递值(LET)为75 MeV·cm2·mg-1、入射方向为垂直入射的粒子对反相器输出电压的影响。从图2 中可以看出,入射粒子使反相器的输出电压产生了向下的SET 脉冲。而随着NMOS 漏极和PMOS 漏极之间间距的减小,SET 脉冲的幅度和宽度也随之减小,使得反相器的单粒子敏感性降低。

图2 NMOS 漏极和PMOS 漏极间距对反相器SET 脉冲的影响

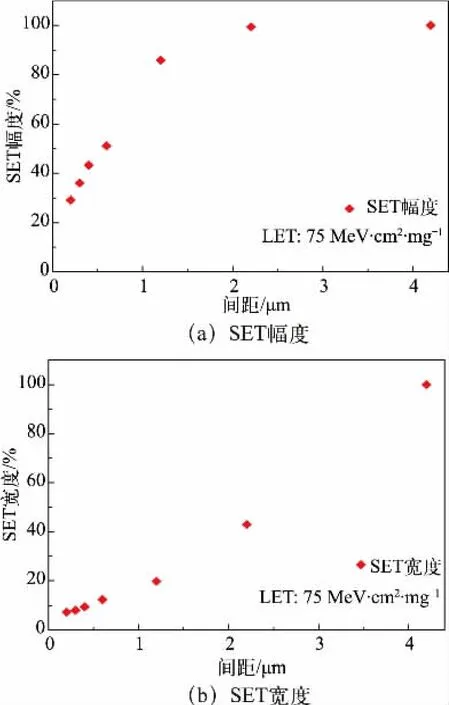

SET 脉冲的幅度和宽度随NMOS 漏极与PMOS漏极之间间距的变化关系如图3 所示(以NMOS 漏极和PMOS 漏极之间的间距为4.2 μm 时SET 脉冲作归一化处理)。从图3 中可以看出,随着NMOS 漏极和PMOS 漏极之间间距的减小,SET 幅度的减小程度急剧增加,SET 宽度呈现出线性减小的趋势。与NMOS漏极和PMOS 漏极之间的间距为4.2 μm 时的情况相比,当NMOS 漏极和PMOS 漏极之间的间距为0.2 μm 时,SET 脉冲的幅度大约降低了71%,SET 脉冲宽度大约减少了93%。

图3 粒子的LET 值为75 MeV·cm2·mg-1 时,SET脉冲随NMOS 漏极和PMOS 漏极之间间距的变化关系

当粒子的LET 值分别为37 MeV·cm2·mg-1和15 MeV·cm2·mg-1时,NMOS 漏极和PMOS 漏极间距对反相器SET 脉冲的影响如图4 所示,SET 脉冲的幅度和宽度随NMOS 漏极和PMOS 漏极之间间距的变化关系如图5、6 所示(以NMOS 漏极和PMOS 漏极之间的间距为4.2 μm 时SET 脉冲作归一化处理)。

图4 粒子LET 值不同时NMOS 漏极和PMOS 漏极间距对反相器SET 脉冲的影响

图5 粒子LET 值为37 MeV·cm2·mg-1 时,SET 脉冲随NMOS 漏极和PMOS 漏极之间间距的变化关系

从图5 可以看出,粒子LET 值为37 MeV·cm2·mg-1时与粒子LET 值为75 MeV·cm2·mg-1时的情况类似,随着NMOS 漏极和PMOS 漏极之间间距的减小,SET幅度的减小程度急剧增加,SET 宽度呈现出线性减小的趋势。当粒子的LET 值为37 MeV·cm2·mg-1时,与NMOS 漏极和PMOS 漏极之间间距为4.2 μm 时的情况相比,当NMOS 漏极和PMOS 漏极之间间距为0.2 μm 时,SET 脉冲的幅度大约降低了85%,SET 脉冲宽度大约减少了95%,此时重离子在反相器中产生的SET 脉冲基本可以忽略。

图6中当粒子的LET 值为15 MeV·cm2·mg-1时,与NMOS 漏极和PMOS 漏极之间间距为4.2 μm 时的情况相比,当NMOS 漏极和PMOS 漏极之间间距为0.2 μm 时,SET 脉冲的幅度大约降低了90%,SET 脉冲宽度大约减少了97%,此时重离子在反相器中产生的SET 脉冲基本可以忽略。

图6 粒子LET 值为15 MeV·cm2·mg-1 时,SET 脉冲随NMOS 漏极和PMOS 漏极之间间距的变化关系

当重离子入射到MOS 管后将产生大量电子空穴对,经过漂移、扩散、双极放大效应,被MOS 管收集。当MOS 管处于反向偏置时,其漏端最为敏感。NMOS漏极接高电平,有大量的电子向漏极漂移和扩散,当积累到一定程度会将漏极电位由“1”拉到“0”;PMOS漏极接低电平,有大量的空穴向漏极漂移和扩散,当积累到一定程度会将漏极电位由“0”拉到“1”。当MOS管处于正向偏置时,其对于SEE 不敏感。NMOS 漏极接低电平,有少量的电子被NMOS 收集;PMOS 漏极接高电平,有少量的空穴被PMOS 收集。

对于本文仿真的情况,重离子会影响反相器中处于反向偏置的NMOS 管和处于正向偏置的PMOS管。当重离子入射到处于反向偏置的NMOS 晶体管漏极区域,重离子所产生的负电荷会被漏极所收集,在反相器的输出电压中引起一个较大的从“1”到“0”的“负向”瞬态脉冲,如图7(a)所示;当重离子入射到正向偏置的PMOS 晶体管漏极区域,重离子所产生的正电荷会被漏极区域收集,引起小的从“1”到正“1”的“正向”瞬态脉冲,反相器输出的逻辑状态不会改变,如图7(b)所示。而当反相器中的NMOS 漏极和PMOS 漏极间距小于一定程度时,粒子所产生的电荷就能够被反偏的NMOS 漏极和正偏的PMOS 漏极收集到,这样一个入射粒子就能同时影响两个区域。由于在电路上NMOS 的漏极和PMOS 的漏极是同一逻辑节点,粒子在“OFF”状态NMOS 漏极所产生较大的从“1”到“0”的“负向”瞬态脉冲就会被粒子在“ON”状态PMOS漏极所产生的从“1”到正“1”的“正向”瞬态脉冲抵消掉一部分,即入射粒子同一时间影响到了NMOS 晶体管漏极区域和PMOS 晶体管漏极区域,在PMOS 晶体管漏极区域由于收集正电荷所引起的正向电压波动会补偿NMOS 晶体管漏极区域由于收集负电荷所引起的负向电压波动,使入射粒子引起的瞬态脉冲减弱,从而使反相器中的输出电压SET 脉冲的幅度和宽度减小,见图7(c)。而SET 脉冲的幅度和宽度减小量取决于PMOS 漏极和NMOS 漏极所收集到的电荷量。由粒子在硅中所产生的电荷分布特性可知,离粒子入射位置越远,所收集到的电荷量也越少。所以当入射粒子的位置与NMOS 的距离固定时,PMOS 漏极所收集到的电荷量就随着NMOS 和PMOS 的间距减小而增加,从而使得反相器中的输出电压SET 脉冲的幅度和宽度随着NMOS 和PMOS 的间距减小而减小。

图7 入射粒子位置对反相器输出电压的影响

3.2 角度的影响

除了垂直入射的情况,本文还研究了在不同的入射角度下,28 nm 体硅CMOS 反相器中的电荷共享效应。在本文所有的斜入射情况仿真中,仿真粒子入射方向为从NMOS 管朝向PMOS 管。

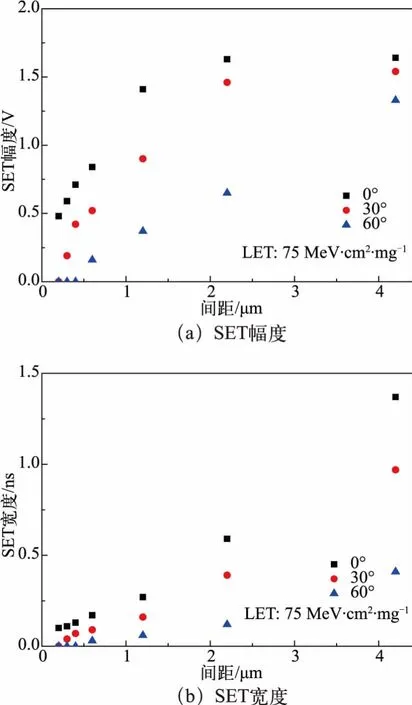

当粒子的LET 值为75 MeV·cm2·mg-1、入射角度为30°和60°时,重离子在反相器中产生的SET 脉冲幅度和宽度随NMOS 漏极和PMOS 漏极之间间距的变化关系如图8 所示。从图中可以看出,与垂直入射的情况类似,随着NMOS 漏极和PMOS 漏极之间间距的减小,反相器的SET 脉冲幅度和宽度有明显的减小。与垂直入射的情况相比,在器件间距相同的情况下,倾角入射下反相器的SET 脉冲幅度和宽度有明显的减小,入射角度越大,SET 脉冲幅度和宽度越小。当器件间距为4.2 μm、入射角度为30°时,重离子在反相器中瞬态脉冲幅度和宽度分别为垂直入射情况下的93.9%和70.8%;入射角度为60°时,重离子在反相器中瞬态脉冲幅度和宽度分别为垂直入射情况下的81.1%和29.9%。器件间距越小,倾角入射下瞬态脉冲的减小程度就越大。

图8 粒子LET 值为75 MeV·cm2·mg-1 时,不同入射角度下SET 脉冲幅度和宽度随NMOS 漏极和PMOS 漏极之间间距的变化关系

当粒子的LET 值分别为37 MeV·cm2·mg-1和15 MeV·cm2·mg-1时,不同入射角度下,重离子在反相器中产生的SET 脉冲幅度和宽度随NMOS 漏极和PMOS 漏极之间间距的变化关系如图9 和10 所示。

与粒子的LET 值为75 MeV·cm2·mg-1时的情况类似,在器件间距相同的情况下,倾角入射下反相器的SET 脉冲幅度和宽度有明显的减小,在入射角度为60°时,体硅CMOS 反相器漏极之间的电荷共享效应比入射角度为30°时更加显著。当入射粒子LET 为37 MeV·cm2·mg-1、器件间距为4.2 μm 时,入射角度为30°时重离子在反相器中瞬态脉冲幅度和宽度分别为垂直入射情况下的81.3%和71.2%(见图9);入射角度为60°时,重离子在反相器中瞬态脉冲幅度和宽度分别为垂直入射情况下的52.7%和29.7%(见图9)。器件间距越小,倾角入射下瞬态脉冲的减小程度就越大。当入射粒子LET 为15 MeV·cm2·mg-1、器件间距为4.2 μm、入射角度为30°时,重离子在反相器中瞬态脉冲幅度和宽度分别为垂直入射情况下的80.6%和86.4%(见图10);入射角度为60°时,重离子在反相器中瞬态脉冲幅度和宽度分别为垂直入射情况下的58.1%和38.9%(见图10)。同样的,器件间距越小,倾角入射下瞬态脉冲的减小程度就越大。

图9 粒子LET 值为37 MeV·cm2·mg-1 时,不同入射角度下SET 脉冲幅度和宽度随NMOS 漏极和PMOS 漏极之间间距的变化关系

图10 粒子LET 值为15 MeV·cm2·mg-1 时,不同入射角度下SET 脉冲幅度和宽度随NMOS 漏极和PMOS 漏极之间间距的变化关系

当粒子倾角入射时,NMOS 的漏极和PMOS 的漏极之间的电荷共享效应会被进一步加剧,并且入射角越大,电荷共享效应就越显著,在仿真结果中,入射角为60°时NMOS 的漏极和PMOS 的漏极之间的电荷共享效应最为明显。在LET 为15 MeV·cm2·mg-1、NMOS 漏极和PMOS 漏极之间的间距小于0.6 μm时,重离子几乎不会影响体硅CMOS 反相器的输出信号。这是因为随着粒子入射角的不断增加,粒子轨迹越靠近从器件的漏端,重离子在其轨迹上产生的电子空穴对更容易被从器件收集,而主器件所收集的电荷会减弱,角度对PMOS 管的影响要远远大于对NMOS管的影响,大量的电荷直接在PMOS 管下产生。由于PMOS 的电荷共享收集主要依靠电荷的扩散,入射角的增加使得粒子入射轨迹上产生的电荷直接位于PMOS 漏极下,极大地减小了电荷向PMOS 管的扩散距离,使得PMOS 管收集电荷更加容易。NMOS 的漏极和PMOS 的漏极之间的电荷共享效应会被进一步加剧,从而使得反相器中的输出电压SET 脉冲的幅度和宽度进一步减小。

4 结论

本文采用TCAD 软件建立了28 nm 体硅工艺的三维器件模型,研究了在不同粒子LET 值、器件间距和粒子入射角度等参数下重离子在28 nm 反相器中产生的SET 脉冲的变化规律。研究发现可以利用反相器中正向偏置晶体管和反相偏置晶体管的电荷共享效应来减弱重离子产生的瞬态脉冲。仿真结果表明:随着NMOS 的漏极和PMOS 的漏极之间间距的减小,电荷共享效应会使重离子在反相器中产生的SET脉冲的幅度和宽度也随之减小。随着粒子入射角度的增大,这种电荷共享效应就更加明显。当粒子入射角为60°、LET 为15 MeV·cm2·mg-1、NMOS 漏 极 和PMOS 漏极之间的间距小于0.6 μm 时,重离子几乎不会影响体硅CMOS 反相器的输出信号。在未来的抗辐射加固设计中,可以利用这种电荷共享效应,通过合理调节处于同一逻辑节点的NMOS 漏极和PMOS 漏极之间的间距来减小重离子所产生的SET 脉冲,从而提高电路的抗SEE 性能。