可变高应力氮化硅薄膜的内应力研究

2022-08-01孙建洁张可可陈全胜

孙建洁,张可可,陈全胜

(无锡中微晶园电子有限公司,江苏无锡 214035)

1 引言

在半导体制造业的快速发展期,尤其是近三十年以来,随着芯片尺寸的不断缩小,芯片的运行速度也在不断提升,而硅材料一直起着至关重要的促进作用。但是,随着芯片工艺技术的持续发展,人们对芯片的功能要求越来越高,硅材料物理性能方面的不足之处对芯片运行速度的进一步提升产生了一定的阻碍。为此,从20 世纪90 年代初开始,逐渐涌现出可以改善这种状况的一系列新技术,如应变硅技术、硅晶绝缘体(SOI)技术等。

应变硅技术的工艺原理是将在金属氧化物半导体(MOS)管的栅极下沟道处硅原子的间距进一步拉大,降低电子通行所受到的阻力,等同于把导通电阻降低。当MOS 管工作的时候,源极和漏极之间的载流子就会顺利地沿着横向拉伸方向自由通过,从而降低半导体器件的功耗及发热量,对其运行速度的提升也有一定的推动作用。所以,实现该技术的关键点是找到一种成本较低、制备工艺简单且可工业化生产的方法来扩大硅原子之间的相对间距。

2004 年IBM 和AMD 在IEDM 会议上报道了在金属氧化物半导体场效应晶体管(MOSFET)表面淀积SiN 薄膜形成应变硅的双应力衬底(DSL)的新技术[1]。采用该技术研制的N 型和P 型MOSFET 的驱动电流均会得到一定程度的提升。

虽然SiN 致应变技术已经提出很久,但是实际工艺中在Si 表面实现高应力(大于2 GPa)SiN 薄膜非常困难。本文以低频等离子体增强化学气象沉积(PECVD)SiN 薄膜为基础,在一定工艺下实现了张应力和压应力的切换,且可以实现2 GPa 以上的高应力效果。

2 实验

目前半导体SiN 工艺制程主要分为低压化学气象沉积(LPCVD)淀积SiN 和PECVD 淀积SiN。从长期在线统计数据来看,LPCVD SiN 应力主要以张应力为主[2],低频PECVD SiN 应力主要以压应力为主(如图1 所示)。

图1 薄膜中张应力与压应力的示意图

SiN 膜覆盖层的应力主要包括本征应力和热应力[3]。本征应力与SiN 膜的淀积条件有关[4],如温度、气体配比、射频功率、气压等均会影响应力的大小[5]。而热应力与SiN 和Si 之间的热膨胀系数有关,通常条件下温度越高应力越大。实际上常规LPCVD SiN 产生的张应力随着淀积温度的升高反而降低[6],很难达到1 GPa以上(如图2 所示)。要在LPCVD SiN 实现高张应力无论是从本征应力还是热应力着手都很困难,因此需要寻找一种新的可以实现高张应力的方案。

图2 LPCVD SiN 膜应力与淀积温度的对应关系

本文采用低频PECVD 设备(美国应用材料公司生产,型号为P5000)制备压应力SiN 膜。选用未进行过任何工艺的裸硅材料光片进行预应力测试,然后在低频PECVD 机台进行淀积条件分片后测试应力。该过程主要是在温度和淀积时间固定的条件下探索SiN膜厚、射频功率对SiN 膜应力的影响。基于PECVD 设备的限制,制备的SiN 硬件的射频功率范围在350~500 W,具体分片条件见表1。

表1 低频PECVD 生成的SiN 膜应力实验数据

厚度测试是利用膜厚仪(美国THERMA-WAVE公司生产,型号为OP2600,其测试误差在±0.1 nm)选取直径为125 mm 的5 寸圆片上的上、中、下、左、右5个点,计算其平均值作为参考;应力测试选取淀积SiN薄膜的5 寸圆片,采用应力仪(美国KLA Tencor公司生产,型号为FLX5400,其测试误差在±0.05×10-9dyn)测试整片圆片上的应力值大小,应力测试是针对整片圆片。

热应力与SiN 和Si 的热膨胀系数有关,通常条件下温度越高,应力越大。由于LPCVD 生成的SiN 膜热应力未达到预期要求,因此本文使用低频PECVD 生成的SiN 膜进行热应力实验。使用低频PECVD 生成的SiN 膜由于受低频PECVD 机台限制,淀积温度无法超过500 ℃,且低频PECVD 的SiN 膜压应力随着淀积温度的升高会先增大后减小[7-8],因此本文利用氧化炉(型号THERMCO 4500)进行高温退火工艺,最终进行应力测试,具体条件见表2。

表2 低频PECVD 生成的SiN 膜热应力实验数据

3 实验结果与分析

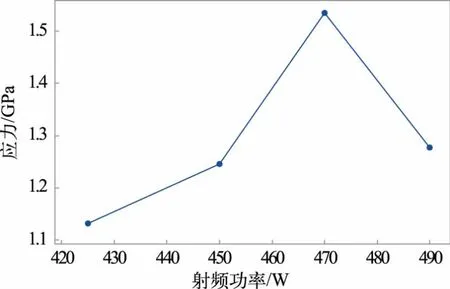

射频功率对SiN 膜应力的影响如图3 所示,当射频功率在350~425 W 之间变化时,其应力波动趋势不明显,且表现为压应力模式,应力绝对值均小于0.1 GPa,当射频功率大于425 W 后,其应力变化很大,可达到2 GPa 以上。射频功率为400 W 时,SiN 膜厚对应力的影响如图4 所示,从图中可以看出SiN 的厚度对应力的影响微乎其微,因为当射频功率一定时,PECVD 淀积的SiN 速率及膜层内缺陷密度不会变化,所以内应力变化也较小[9]。

图3 射频功率对应力大小的影响

图4 SiN 膜厚对应力大小的影响

氧化炉850 ℃退火30 min 后SiN 膜应力的变化趋势如图5 所示,当射频功率为470 W 时,应力由退火前的负应力转变正应力,且应力值接近1.6 GPa,主要是因为SiN 膜层本身的内部结构中除了有Si-N 键,还有大量的游离态H,而这些H 主要以N-H 键和Si-H 键的形式存在[10],经过高温退火后,SiN 膜层内的部分H 会形成一种悬挂键和微孔而溢出,而这些悬挂键之间相互交联,微孔会产生一定收缩,最终会使薄膜的体积收缩变小从而形成一种张应力结构[11]。

图5 氧化炉850 ℃退火30 min 后SiN 膜应力变化趋势

图6为低频PECVD 生成的SiN 膜在不同温度退火下的应力变化图,通过低频PECVD 生成的SiN 膜,在加大射频功率后压应力可以直接达到2 GPa,不断提高炉管的高温退火温度到1050 ℃,退火时间由30 min 延长至120 min,其应力变化不明显。这主要是因为随着退火温度和时间的加长,H 的溢出量会有变化,在经历一定时间的退火后,SiN 薄膜内的应力会达到饱和点。因此,通过实验过程可以发现,在射频功率为470 W 时,PECVD 工艺淀积的薄膜应力表现为压应力,当该膜层在850 ℃以上退火后,压应力会转变为张应力,且在1050 ℃退火90 min 后,应力达到最大值,约2.1 GPa。

图6 低频PECVD 生成的SiN 膜在不同温度退火下的应力转变

4 总结

本文利用低频PECVD 生成的SiN 膜和高温退火实现了压应力与张应力两种可变应力,并且研究了应力随退火温度及时间的变化趋势,通过控制温度,最终可以实现2 GPa 的高应力。这种高应力SiN 膜的制备方法有3 个优点:(1)工艺简单,仅利用单种PECVD设备和退火炉即可实现两种应力转变,成本较低;(2)应力的可选择范围较大;(3)可以将该种方法直接嵌入到整个IC 工艺制造流程中,实现应力转变。当然,这种SiN 膜应变方法在实际IC 制造过程中电路性能的提高程度,还需在后续的实际制造过程中不断探索。