一种超宽带频率综合器电路的设计与实现

2022-08-01赵建欣廖春连

赵建欣,廖春连

(中国电子科技集团公司第五十四研究所,石家庄 050081)

1 引言

随着无线电通信技术的广泛应用,射频微波器件的地位显得举足轻重,而频率综合器电路又是所有上变频、下变频电路的核心结构。射频微波行业一直致力于提供功能更强、性能更高、尺寸更小、成本更低的微波集成电路,特别是进入到纳米、亚纳米的工艺量级,CMOS[1]技术在射频领域得到广泛的应用。

频率综合器电路是变频芯片的心脏,变频芯片实现功能的关键是频率综合器电路的正常工作。频率综合器所产生的本振信号相位噪声会影响信号变频后的信噪比,目前业内对于频率综合器电路的设计和实现已经有一些相关研究。曲明[2]等对频率综合器电路中的噪声抑制提出了行之有效的解决方法,通过调整鉴相器延迟、消除电荷泵泄露以及降低环路滤波器的电阻热噪声等方法实现了频率综合器的低噪声设计,可行性高、效果好。该研究是基于S 波段2~4 GHz 的电路设计,对于实现更高频率、更大带宽的频率综合器电路中的低噪声设计,则需要更多方式来进一步抑制环路中噪声的产生。

无线电通信系统的收发机通信速度与工作带宽以及高精度频率源的频率稳定度是正相关的,带宽越大则通信速度越快。代传堂[3]对于超宽带频率综合器的设计提出了一种低噪声方案,可以覆盖10~20 GHz的超宽频段,且相位噪声更是达到了-109 dBm/Hz@1 kHz,但是该方案主要是基于芯片产品的模块级设计,尺寸较大、不利于小型化设计与应用,而且选用的HMC733 压控振荡器(VCO)和UXD20P 分频器等器件均为进口芯片,无法实现自主可控。在当下日趋紧张的国际环境中,芯片供应问题已经成为遏制大多数产业发展的关键因素,一款完全自主可控的芯片就显得尤为重要。

本文设计了一种低噪声、超宽带、全集成可重构的高性能频率综合器电路,覆盖了25 MHz~12 GHz 的超宽带频率,更有利于超宽带射频收发电路的实现和应用,满足了诸多无线电通信电路结构的应用需求。

2 整体结构

该正交输出、全集成可重构的频率综合器电路主要包括两部分:频率综合器部分锁相环(PLL)和本振产生电路(LO)。PLL 电路包含鉴频鉴相器(PFD)[4]、电荷泵(CP)、环路滤波器(LPF)、分频器(DIV)、自动频率控制(AFC)、VCO 和Delta-Sigma 调制器(DSM)[5]。本振信号产生电路主要由多个分频器和多个多路选择器(MUX)组成,能够给后级混频器提供25 MHz~12 GHz 的正交信号[6]。

为了满足覆盖25 MHz~12 GHz 的正交输出,适合做到片上全集成以及得到尽可能优的相位噪声,本电路采用电荷泵频率综合器架构的设计,使用双核VCO来覆盖足够宽的频率范围,多级级联的本振信号生成技术实现本振的IQ 正交信号输出,整体功能框图如图1 所示。

图1 频率综合器系统结构

其中AFC 提供了自动锁频环路,帮助PLL 实现快速的自动锁定;环路滤波器则需要大幅减小传统的电路设计面积以便实现片上集成;VCO 电路模块需要满足12~24 GHz 的频率调谐范围[7];LO 使用分频器级联链产生25 MHz~12 GHz 的正交输出;Feed-Back 使用预分频和十级多模级联分频器(MMD)实现了128~2047 的宽范围分频比,以满足参考频率fREF在10~40 MHz 的范围内变化时,VCO 覆盖12~24 GHz 的频率要求[8]。

一个高性能的频率综合器主要体现在低杂散和低噪声两个方面。在低杂散方面,本设计采用了高阶多级噪声整形(MASH)结构的DSM,利用其调制技术的高频传输特性将量化过程中产生的小数杂散能量搬移到高频部分,再利用PLL 本身固有的低通滤波功能滤除小数杂散。这个方法有效地消除了由累加器量化误差产生的小数分频杂散,从而提高了小数分频器的频谱纯度。而且可以根据PFD 的死区延迟时间、前置分频器的分频模式进行数字调整,有效地减少了PFD、电荷泵线性度不好带来的带内杂散。此外,20 bit的DSM 与分频器配合实现了频率步进低至39 Hz 的小数分频[9]。

在低噪声方面,本设计的各个模块电路都做了进一步优化,使得各部分的附加相位噪声做到最小。与此同时,更大的电荷泵电流、更高的环路带宽以及更小的环路分频比都能极大地降低环路噪声,从而大大优化了频率综合器电路的噪声性能。

3 主要电路的分析与设计

3.1 宽带高频VCO 的设计

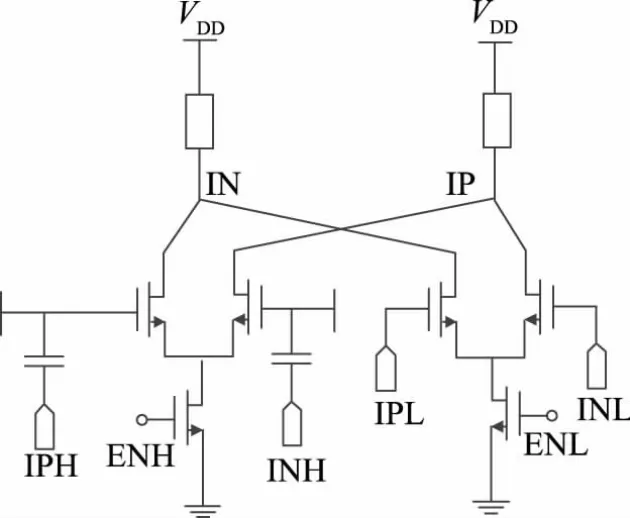

为了覆盖25 MHz~12 GHz 的超宽带正交PLL 输出,VCO 需要能够覆盖12~24 GHz 的频率范围[10]。为了实现大于60%的频率调谐范围,本设计采用了双核VCO 的结构(如图2 所示),从而保证了连续的频率调谐范围。其中低频和高频VCO 分别覆盖12~18 GHz和18~24 GHz 的频率范围,并在两者之间设置适当的频率交叠区间,以避免流片后因工艺影响导致的调谐频率空挡区[11]。

图2 VCO 结构

VCO 架构采用了NMOS-Only Class-B 架构,调整摆幅最大化输出,在降低高频分频器设计难度的同时还能获得更为优异的相位噪声性能[12]。VCO 能够根据当前的谐振频率来调节变容管的接入数量、削弱Kvco的变化、降低调幅-调相(AM-PM)相位噪声的转化,保证环路特性的稳定。当使能VCO bias 电路以及VCO Buffer 电路时,可进行频段的切换,此时VCO Buffer中的电容值可自动调整,从而达到改变峰值频率、拓展带宽[13]的目的。

3.2 LO 信号产生器

LO 能够产生25 MHz~12 GHz 的正交信号,其整体结构如图3 所示。该LO 按工作频段划分为三部分电路:高频段(6~12 GHz)、中频段(750 MHz~16 GHz)和低频段(23.4375~750 MHz)。分频器主要由预分频器和MMD 构成。其中,前三级为电流模式逻辑(CML)结构,后七级为CMOS 结构。高频段由预分频器提供;中频段通过多模级联分频器的三级CML 结构分频器提供;低频段由多模级联分频器的CMOS 分频器提供。

图3 LO 信号产生器结构

在高频段,预分频器采用了高速、宽带、大摆幅输出的分频器结构,可以在满足高频率和大带宽工作的同时,输出更大的摆幅,并且可以在有效降低下一级设计难度的同时,大大降低Buffer 的功耗。

在中频段采用的三级CML 分频器结构中,取消了电流源的设计,因而减少了电流限制和压降损失。设计时,在输入管的栅端串联了隔直电容,不仅避免了前一级电路的直流工作点对该级分频器工作的影响,而且还可以使该分频器的直流(DC)偏置点变得可调,从而进一步增强稳健性。中频段通过一个CML 结构的多路MUX 进行选通合并,最终在MUX 输出端产生了750 MHz~6 GHz 的正交信号。在本频段电路设计中,每一级结构都包含前后两个CML 分频器,一个用于产生正交信号,另一个用于产生下一级的差分输入信号。通过将IQ 正交信号和差分信号分离的方式提高IQ 正交性能并能有效降低设计难度。而且由于这两个CML 分频器分别工作在不同频率范围,时分复用,从而降低了功耗。

低频段电路中采用了五级级联CMOS 分频器,包含了四级差分分频器和一级IQ 正交分频器,能产生23.4375~750 MHz 的IQ 正交信号。这种结构的优势在于仅处理一组IQ 正交信号即可,可有效降低MUX 的面积功耗及版图设计的复杂度。

中、低频段部分会通过一个多路MUX 进行合并,获得23.4375 MHz~6 GHz 的正交信号。高频段6~12 GHz 的正交信号和中低频段通过共用电阻负载的MUX 合并后,最终输出23.4375 MHz~6 GHz 的正交信号,输出MUX 电路结构如图4 所示。高频段电路通过隔直偏置的方式获得最佳的工作DC 点,低频部分则由于摆幅较大,通过直连的方式进行互联。

图4 输出MUX 电路结构

3.3 环路滤波器设计

通常情况下,环路滤波器是设计在PLL 片外的,为了减少片外的元器件数量,便于产品应用,在本设计中实现了环路滤波器的片上全集成。环路滤波器电路结构如图1 中Loop FILTER 框中所示。

优异的低噪声性能是一个高性能频率综合器电路性能的重要体现,优化环路噪声的一个重要方法就是通过增大环路滤波器中的电容值来增大电荷泵的电流,从而降低电荷泵的噪声以及滤波器电阻的噪声;此外,更大的环路带宽也能有效抑制带外VCO 的相位噪声。

而在此设计中,C2值可达到纳法(nF)级,并且为了实现全集成及提高电容密度,C2选用了MOM(Metal Oxide Metal)电容以及高压管堆叠设计制作,大大减小了整个滤波器的面积,使得片上集成成为可能。与此同时,环路滤波器中的所有阻容参数均可通过寄存器实现控制调节,可以根据实际的应用环境调节环路滤波器的带宽及阶数(其中C3、C4、R3和R4均能完全关断)。环路滤波器带宽的可调节范围大大提高,可以更好地抑制带外VCO 的相位噪声。此外滤波器参数的选取还保证了覆盖所有频率范围,进而实现了可重构的目的。

4 整体电路环路仿真结果

频率综合器电路的仿真条件设定为电荷泵电流为1 mA、环路带宽为200 kHz、分频比为150 的工作状态。在25 ℃时TT 工艺角的参数条件下进行的仿真结果表明,此时VCO 输出频率为6 GHz(12 GHz/2),Vtune的稳定电压为726 mV,稳定时间不超过5 μs。PLL的相位噪声拟合结果显示100 kHz 频偏处相位噪声低于96 dBc/Hz。图5 中实线为Vtune的稳定过程曲线,虚线为锁定频率稳定过程曲线。图6 为输出信号的相位噪声拟合结果。

图5 瞬态仿真结果@6 GHz

图6 相位噪声拟合结果@6 GHz

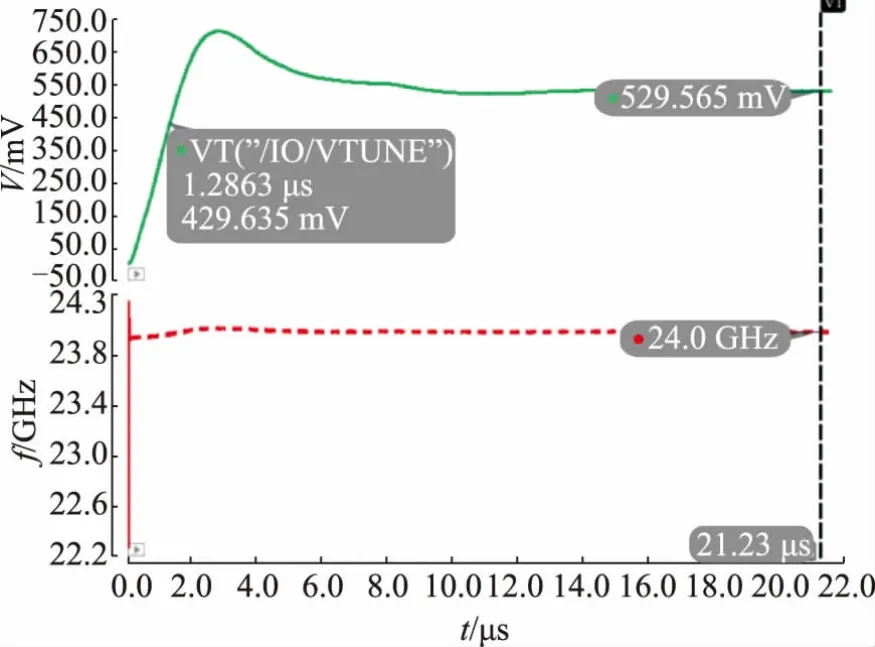

将仿真条件设为环路带宽为450 kHz、分频比为300 时,此条件下的仿真结果表明,此时VCO 输出频率为12 GHz(24 GHz/2),Vtune的稳定电压为529 mV,稳定时间不超过5 μs。PLL 的相位噪声拟合结果显示其100 kHz 频偏处相位噪声低于93 dBc/Hz。图7 中的实线为Vtune的稳定过程曲线,虚线为锁定频率稳定过程曲线。图8 为输出信号的相位噪声拟合结果。

图7 瞬态仿真结果@12 GHz

图8 相位噪声拟合结果@12 GHz

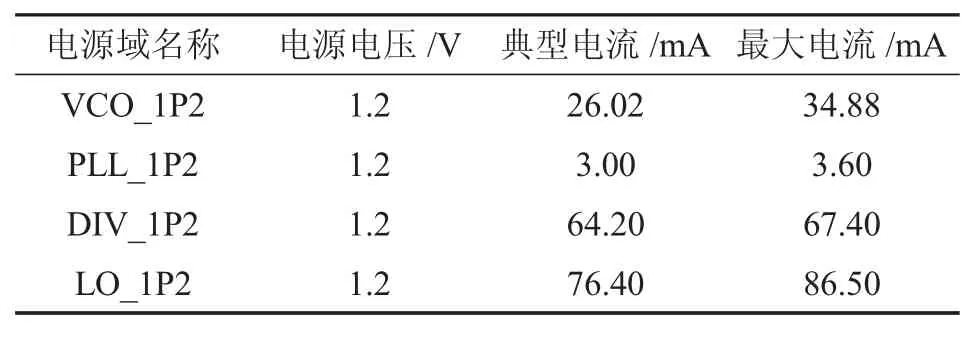

本设计中主要模块对应电源域的功耗如表1 所示,PLL 核心(表中前3 行)总共消耗电流93.22 mA,LO 产生模块消耗电流76.4mA,典型总功耗203mW。

表1 不同电源域功耗

5 测试结果与分析

本设计采用CMOS 工艺流片,芯片尺寸为0.658 mm×1.2 mm,DUT 测试评估板采用die 到印制电路板(PCB)的引线键合方式。整体电路工作状态由数字控制模块的串行接口(SPI)在上位机PC 端通过图形化软件操作控制,参考时钟以及数字控制模块SPI 的时钟信号均由外部频率为40 MHz 的温补石英晶体振荡器提供。

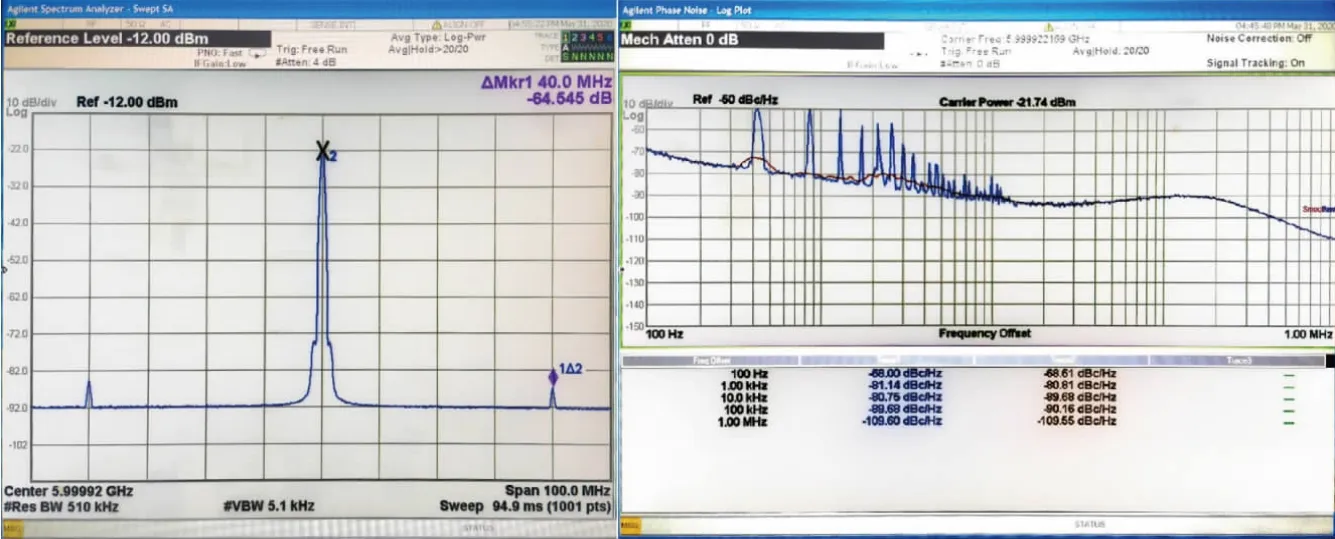

通过调整MMD 的配置,可实现最低23.4375 MHz(12 GHz/512)的频率输出,当MMD 设置为不分频时,最终频谱测试和相位噪声指标测试结果分别如图9 和图10 所示。从测试图形中可以看到:VCO 输出频率分别为6 GHz 和12 GHz 时,频率综合器输出相位噪声均不大于-85 dBc/Hz@100 kHz offset。

图9 6 GHz 频谱测试和相位噪声指标测试结果

图10 12 GHz 频谱测试和相位噪声指标测试结果

6 结论

本文设计了一款应用于超宽带射频收发电路的高性能频率综合器电路,集成了双核VCO、PFD、电荷泵、环路滤波器、自动频率控制分频器和DSM,可以给收发机中的后级混频器提供25 MHz~12 GHz 的差分IQ 信号,并且实测结果性能良好,适用性强,可以满足该频段收发机的上下变频处理,对于多频段一体化通信、雷达无线电跳频、软件无线电及相关领域具有一定的参考意义。