基于亿门级UltraScale+架构FPGA 的单粒子效应测试方法

2022-08-01谢文虎郑天池季振凯杨茂林

谢文虎,郑天池,季振凯,杨茂林

(无锡中微亿芯有限公司,江苏无锡 214072)

1 引言

现场可编程门阵列(FPGA)电路具有规模大、集成度高、处理速度快及编程灵活等优点,在航空航天领域得到广泛应用。由于空间辐照及高能粒子的存在,静态随机存储(SRAM)型FPGA 在进行空间作业时会出现单粒子效应(SEE),造成器件功能异常乃至烧毁[1-2]。辐照领域的学者针对SEE 已经建立起可靠的模型并提出辐照加固方法,然而新工艺技术的引入势必会引发新的难题,尤其是当工艺尺度逼近摩尔定律极限时。

空间作业电子系统在追求高性能、低工艺尺寸及低功耗的同时,需考虑晶体管单位分布密度增大引发翻转阈值下降及单粒子翻转(SEU)现象增多等瓶颈问题[3]。2021 年于庆奎等人对65 nm 的SRAM 型芯片进行单粒子试验,结果表明在重离子辐照下电路的翻转阈值为0.31 MeV·cm2·mg-1,低于0.15 μm、0.12 μm 工艺器件的翻转阈值[4]。这是由于低能质子及高能粒子在电离过程中会同时引发翻转,且随着先进纳米工艺的引入后者所占的比率在逐渐增大[5]。晶体管特征尺寸减小还会引发区域SRAM 单元之间共享电荷现象增多,进而增大多位翻转(MBU)的几率及影响范围[6]。2009 年DAVID 等人对45 nm SRAM 芯片进行SEU试验并研究MBU 的发生趋势,结果表明45 nm 和65 nm 的SRAM 芯片上SEU 截面中的单位翻转(SBU)大致相同,其MBU 从65 nm 的1.6%增加到45 nm 的6%[7]。这说明随着加工工艺的提升,MBU 几率逐渐显著,需要针对该现象建立新的甄别算法,且与SBU 不同,MBU 的出现无法通过误差校正码(ECC)技术消除,严重影响其在空间环境中的飞行可靠性。

本文以赛灵思公司推出的UltraScale+ 架构SRAM 型FPGA 为对象,搭建基于重离子辐照的SEE试验方案,以检测单粒子闩锁(SEL)及粒子翻转特性。针对FinFET 的3D 立体结构及16 nm 先进工艺,搭建甄别SBU 及MBU 的识别算法,以方便考量不同线性能量传输通量(LET)对MBU 几率的影响,为全面评估新工艺技术的飞行可靠性提供支持。

2 UltraScale+架构下的辐照试验原理

2.1 试验样品

本试验所采用UltraScale+器件为Xilinx 公司的XCVU5P,该试验器件(DUT)采用台积电(TSMC)的16 nm FinFET 加工工艺,其封装形式为倒装(Flip-Chip)。该系列DUT 提供多种配置组合,包括逻辑单元数量、BlockRAM、高速收发口、DSP 模块、速度等级、温度等级、封装类型及I/O 接口数量。其中,器件中的配置存储器由SRAM 组成,用来控制器件内部逻辑单元的运行。UltraScale+器件配置说明如表1 所示。

表1 UltraScale+器件配置说明

如表1 所示,DUT 内部的存储类型包括DRAM、BRAM 及UltraRAM (URAM), 共 计186.5 Mb。UltraScale+器件引入新存储结构URAM,显著提高了FPGA 的存储性能及扩展性能。URAM 模块支持多重级联,其单元存储体积为288 kb,最大可构成360 Mb的存储阵列。与BRAM 不同的是,URAM 无法改变初始存储值,因此在SBU 试验中,需使用配置芯片对DUT 的URAM 存储单元进行特定数值配置。

2.2 重离子辐照源及电荷沉积

高能粒子辐照源为中国原子能科学研究院的HI-13 及兰州重离子加速器国家实验室的HIRFL,以上加速器能够提供多种重离子粒子。所激发的束流满足5 cm×5 cm 区域内90%的均匀性,粒子注量率调节区间为10~107cm-2/s。加速器重离子参数如表2 所示,本次试验选取7Li3+、19F9+、35Cl11,14+、48Ti10,15+、74Ge11,20+、127I15,25+、181Ta、209Bi 8 种粒子作为辐照重离子,其硅中射程均超过30 μm,满足试验硅晶的穿透要求。

表2 加速器重离子参数

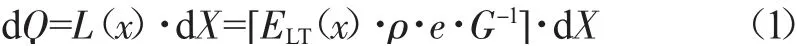

重离子射入硅晶时会不断电离,在库伦力的作用下与周围的原子之间相互作用产生电荷,游离的电荷被晶体管的敏感区收集并触发SEE[8]。LET 是评估高能粒子电离能力的指标,设为ELT,单位为MeV·cm2·mg-1,也作为重离子激发电荷的主要理化参数。在重离子射入硅晶时,其在单位路径上释放的电荷数Q为:

其中Q为电离的电荷量;L(x)为重离子单位距离释放的电荷量;X为入射距离;ρ 为硅晶密度,约为2.328g·cm-3;e为单电荷的电荷量,为1.6×10-19C;G为在硅中激发一对电子-空穴所需的平均能量,约为3.62 eV。

19F9+、35Cl11,14+、48Ti10,15+、74Ge11,20+、127I15,25+5 种重离子在硅晶表面所释放的电荷量与其原子质量呈正相关,并在0.420×10-4~6.793×10-4pC·μm-1之间递增。重离子硅中射程各有差异进而影响各自的布拉格峰深度[9],导致重离子速度降低、电离能力增强,电荷积累量达到临界值时有可能会引发硬件故障,造成SEL。

2.3 FinFET 结构下的抗辐照设计

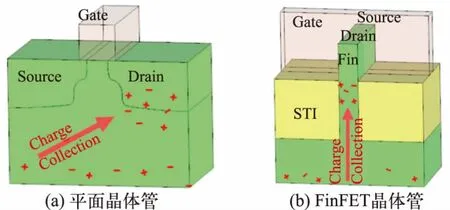

FinFET 工艺能够有效抑制晶体管尺寸缩小带来的SEE。在微观尺寸上,晶体管产生单粒子异常的机理主要包括电荷漂移及扩散。重离子穿过集成电路时电离一定数量的电荷,激发的电荷在晶体管的漏极端积聚并发生沉积,衬底中的电荷也会在电压差及扩散效应下向漏极方向转移并引发翻转[10]。由此可见,实际漏极区域的大小直接影响该晶体管对电荷的收集率。平面晶体管的电荷迁移如图1(a)所示,在同等特征尺寸下传统的平面晶体管与衬底的接触面积显著高于图1(b)中Fin 结构处的有效接触面积。电荷收集率的降低能够有效提升FinFET 的粒子翻转抗性,但是晶体管特征尺寸的缩小引发的翻转阈值降低仍需要进一步验证。

图1 平面晶体管与FinFET 晶体管的电荷迁移示意图

与平面晶体管工艺不同,FinFET 在空间上具有三维差异性,需要考察不同辐照倾角对器件的影响。除垂直于器件表面外,按照Fin 的分布可分为平行Fin向的入射角α,垂直Fin 向的倾角β。在进行非垂直辐照试验时,其有效LET 值ELTe为:

其中ELT0为垂直入射的LET 值;θ 为入射角度,包括α及β。

3 UltraScale+架构器件的辐照测试系统

3.1 SEE 测试板

DUT 测试板分为辐照区和控制区2 个区域。辐照区安装LGA/BGA668_R 插座,背部留有23.6 mm×23.6 mm 的裸露区域用于粒子束辐照。控制区域包括被测电路的配置芯片、主控芯片及配套配置电路和Flash 电路、总线芯片、电源芯片、外部晶振及LED 等器件。

表3 测试板元器件型号

为避免游离电子影响数据读取及外部晶振输入,除辐照区域保持裸露外,控制区域应覆盖隔绝材料,测试板与外界的数据传输通过串口总线进行。为促使高能粒子到达电路层时具有足够的辐照能,对除盖样品进行研磨处理使得硅晶厚度小于入射重离子的硅中射程,本试验将晶圆厚度研磨至30 μm。为确保配置模块正常运行,采用屏蔽材料对所映射物理区域进行抗辐照防护。完成预处理后的样片需经过功能验证。

图2 SEE 测试板

3.2 辐照测试电源系统

本试验涉及的辐照测试电源系统最多可实现5 路供电。NI 工控机自带的电源板卡可提供最大电流为3 A 的4 个独立电源通道,但无法负载DUT 的内核电流,因此需额外配备辅助电源并接入NI 工控机控制系统。电源控制系统见图3,除VCCINT 由辅助电源单独供电外,其余2 路电源VCCO、VCCAUX 由NI 工控机控制。

图3 SEE 试验电源控制系统

在电源控制系统中,所配置的NI 工控机及配置电脑负责收集记录电源卡发出的电流数据并控制试验板上电、掉电、软复位等功能。配置电脑负责收集并存储电源卡发来的数据流,时间间隔为10 ms。在采集到额定电流值后根据上位机指令对芯片进行软复位,若电流恢复正常则试验继续进行,若电流依然处于高位则切断被测芯片的电源,保护测试电路。

3.3 辐照测试配置程序

辐照测试配置程序根据行使功能分为SEL 配置程序及SEU 配置程序2 种。SEL 配置程序调用加法器资源使总资源占用率达到70%,并选择相应的输出以确认程序在DUT 正常运行。

粒子翻转测试的目的是检测UltraScale+架构电路的SRAM、BRAM 及URAM 在静态SEE 下的翻转状态。设置全部的BRAM 和URAM 为全“0”或全“1”,生成mcs 配置文件进行预加载。在完成配置程序加载后开始辐照,以5 MHz 的频率读取SRAM 的状态并与上次数据做对比,得到该状态下的静态翻转次数。

3.4 辐照测试系统

辐照测试系统分为4 个模块,分别为测试电路模块、电源模块、数据收集控制模块及上位机控制模块。测试板安装在带铰链的三维度平动平台上,高能离子经过加速器后入射到DUT 上。固定离子源位置,控制三维度平动平台以调整DUT 位置及入射倾角。试验板通过长2 m 的转接线缆转接到NI 工控机及辅助电源上,经过50 m 长线连接到监测室进行控制。

上位机作为总控中心,负责监视试验状态并实时显示粒子翻转情况。上位机与电路的通讯是双向的,测试板实时发送各项信息给上位机并接收上位机相关指令。DUT 的测试数据通过串口最终发送到上位机,其电流值及翻转次数可作为调节粒子发射率的重要依据。该系统能够实现在测试板的主控芯片上实时比对数据并完成大部分数据处理,并将粒子翻转数量及对应片区和地址发送给上位机以实现可视化监控。

4 UltraScale+架构器件的辐照试验流程及统计方案

本次辐照试验参照QJ 10005-2008《宇航用半导体器件重离子效应试验指南》的相关规定。辐照测试因素见表4,所涉及测试按照功能分为SEL、SEU 阈值、SEU 截面及单粒子多位翻转测试。各试验在重离子种类选取及注量率设定上有所差异,其硬件测试系统基本一致。

表4 辐照测试因素

4.1 SEL 测试

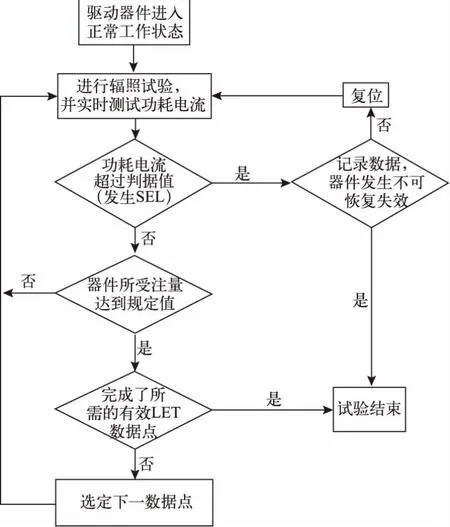

重离子试验中的SEL 试验粒子LET 值需达到75.0 MeV·cm2·mg-1,选取181Ta、209Bi 进行辐照。SEL 测试流程如图4 所示,在合格性测试中,当入射离子累积注量达到107cm-2且电路没有发生锁定时,认为DUT通过SEL 考核。

图4 SEL 测试流程

极限测试主要考察单粒子在一定注量率下可承受的最大重离子累计注量值,以及沿不同Fin 倾角下SEL 的耐受情况。在进行Fin 倾角测试时,需对有效辐照面积进行折算,以记录电路的真实累计注量值。

4.2 SEU 阈值及截面测试

SEU 试验采用HI-13 串列加速器,选取7Li3+、19F9+、35Cl11,14+、127I15,25+、48Ti10,15+、74Ge11,20+6 种重离子,其LET 覆盖范围为0.44~65.6 MeV·cm2·mg-1。在进行SEU 时,DUT 需要在真空环境下进行辐照试验。截面翻转测试与SEU 阈值测试的试验同步进行,其注量率保持在10000 cm-2·s-1。受限于主控芯片的数据处理能力,无法实现对全局SRAM 数据的高频运算处理,特选取在硅晶上物理映射几乎互不胶连的3 处特定区域作为SRAM、BRAM 及URAM 样本进行SEU 分析。所涉及样本的总存储值为53.74 Mb,约占总存储的28.82%,三者占据样本存储的比值分别为10%、30%及60%。

在辐照之前需对DUT 进行功能验证并确保与上位通讯正常。在完成阶段测定后,根据测定数据建立DUT 关于LET 的Weibull 拟合曲线,并推导出DUT的单粒子触发阈值[11]。重离子辐照中DUT SEU 截面σ(cm2·bit-1)为:

其中U为取样区域粒子翻转数;I为重离子单位面积注量率;M为取样区域存储值,单位是bit。

4.3 单粒子多位翻转测试

多位翻转判定逻辑图见图5,多位翻转测试的目的在于探究不同LET 及不同射入倾角下的单位翻转及多位翻转的比值。为避免将短时间内多个粒子单独引发的多个翻转误判为多位翻转,将重离子注量率从10000 cm-2/s 降低为100 cm-2/s。在对多位翻转进行识别时,以互不胶连的取样区域作为物理划分依据,以时间触点作为精准识别因素。将翻转事件划分为单位翻转、多位翻转和粘连翻转。

图5 多位翻转判定逻辑图

本试验所涉及的重离子穿过硅晶的时间为纳秒级,但由于布拉格峰效应的影响,重离子在滞止点附近持续释放大量空穴及电荷。重离子射入后电荷聚集并向漏极方向迁移引发邻近晶体管电荷共享,在此期间重离子射入与晶体管异常显现之间存在延迟[12]。如图5 所示,考虑到多位翻转并非严格同步,后续会将同一采样区域内5 ns 内的翻转划分为多位翻转,根据翻转的位数分为MBU-n,将5~100 ns 内的翻转划分为粘连翻转。调整LET 值及射入倾角,记录并分析各试验条件下单位翻转、粘连翻转及多位翻转的比值,得到DUT 的SEE 特性。

5 结论

本文以UltraScale+架构的SRAM 型FPGA 为对象,搭建重离子-SEE 测试系统并提出测试方法。

针对器件加工工艺逼近摩尔定律极限造成SRAM 单元密集及FinFET 立体差异的特性,提出与之匹配的SEL、SEU 阈值及SEU 截面测试方法;搭建包含上位机监控通讯的测试系统,可实现板卡级的数据预处理及针对测试电流、粒子翻转数量、对应地址等数据的可视化监控;以URAM 为主要测试对象,建立单位翻转及多位翻转的识别分类算法以考察不同LET 对MBU 几率的影响。本文提出的SEE 测试方法能够较为全面地评估UltraScale+ 架构FPGA 的抗SEE 特性,为其在空间电子系统的后续应用提供支持。