片上SRAM 物理不可克隆函数特性优化设计

2022-08-01高国平赵维林

高国平,赵维林

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

1 引言

安全性对于几乎所有电子产品来说都是非常重要的,物理不可克隆函数(PUF)的提出为保护芯片数据安全提供了一种切实有效的方法。以静态随机存储器(SRAM)PUF 为代表的基于存储器的PUF 设计具有很大的优势,在核心集成电路中,存储器是必须具备的单元,其实现简单,现已成为PUF 主流设计方向。

在实际应用过程中,嵌入SRAM 集成电路产生的随机数特性大不相同。通常的方法是寻找具有产生较好随机数特性的集成电路[1-3],然而随着工艺节点的进步,这种方法显露出了较大的局限性[4]。为了便于获得具有SRAM PUF 的集成电路,本文提出了一种设计优化方法。

2 原理分析

SRAM 单元及工艺噪声影响如图1 所示,每一位存储单元通常包含6 个MOS 管,由2 个交叉连接的反相器和2 个读写开关管构成。读写SRAM 存储单元时,控制使能字线,使开关管导通,此时,可以通过位线对SRAM 单元进行读写。当SRAM 断电时,由于SRAM 没有电荷存储,所以SRAM 存储单元瞬间无电荷,AB 状态为“00”。由于反向器为非稳定状态,上电时,其中一个反相器必须翻转一次,AB 状态变为“01”或“10”。理想状态下,AB 的“01”或“10”状态完全是随机的,即无偏差单元。然而事实上,由于制造过程中的不可控因素,单个SRAM 存储单元倾向“0”或者“1”,形成“0”偏(0-skewed)或“1”偏(1-skewed)存储单元。

图1 SRAM 单元及工艺噪声影响

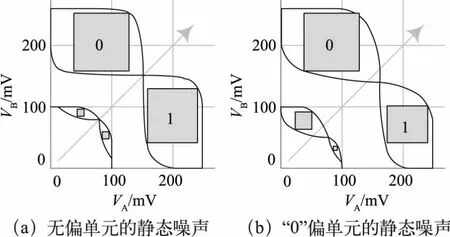

静态噪声容限(SNM)σNoise是描述SRAM 单元噪声容限的指标。单元的SNM 是给定电源电压的最大噪声电压[5]。对于外界噪声的影响,存储单元对称结构匹配越好,外界噪声的影响作用就会越大,甚至会造成存储器偏向相反方向。存储单元上电倾向以及噪声影响如图2 所示,其中VA、VB为A、B 点电压。

图2 存储单元上电倾向以及噪声影响

除了外界噪声和工艺变化,电源电压也会影响SRAM 单元的初始状态。电源电压越低,SRAM 单元的噪声容限越小,对噪声越敏感;电源电压越高,SRAM 单元噪声容限增加,对噪声就会免疫。最低的电源电压使得SRAM 单元不改变原来的状态,典型值为100~300 mV[6-10]。上电过程中,假设电源电压从0 V开始,所有SRAM 单元受到外界噪声的影响。当电源电压大于300 mV 时,所有SRAM 单元状态不再因噪声而改变。

在反相器电压传输曲线(VTC)上,噪声免疫单元有两个大的“眼”,电源电压下降,静态噪声容限也大大减小。在没有噪声影响的无偏单元里,低电源电压导致同样小的静态噪声容限。然而,在高偏差的单元,低电源电压减小了“0”偏的静态噪声容限,仅存在单个噪声容限。

通过控制电源上电的速度,也能够影响SRAM 单元的随机状态。如果上电维持在100 mV,非常微弱的噪声会引起有偏差单元进入“0”状态。在100 mV 维持的时间越长,越会增加SRAM 单元状态随机可能性。电源电压上电越慢,越有利于SRAM 单元的随机性。

然而在某种应用场景下,掉电后的电源电压高于100~300 mV,上电后的SRAM 不能产生理想的具有物理特征的随机数据。因此为了能利用片上SRAM 生成稳定的本征数据,需要对芯片进行优化设计。

3 芯片设计

为了实现上电后产生具体物理特征的SRAM 本征数据,需要进行两方面的设计:1)下电电压控制,让SRAM 电源充分掉电到100 mV 以下;2)上电斜率控制,SRAM 电源上电速度的有效控制。

优化SRAM 的具体实现如图3 所示。通过上下电控制电路实现下电后SRAM 的电源下降到100 mV以下,通过上电部分电路控制SRAM 单元的上电曲线斜率。

图3 SRAM 优化设计实现示意图

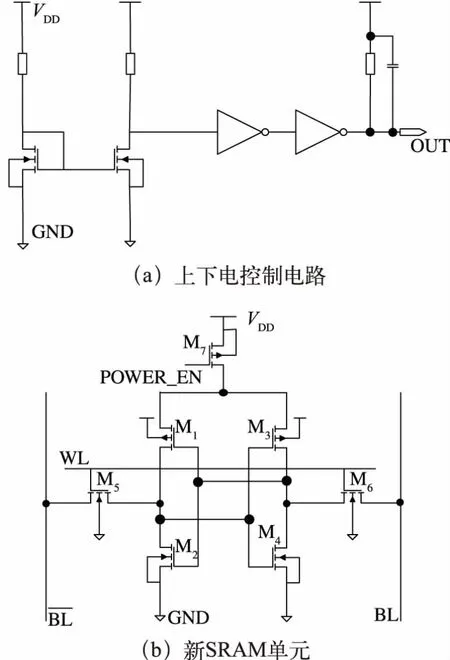

上下电控制电路的具体实现如图4(a)所示。由于3.3 V 和5 V 工艺的器件最低工作电压都在1.5 V 以上,为了留有一定设计余量,设计上下电电源电压典型值为2.1 V,此时电路能稳定工作。对最后一级的驱动进行斜率控制。通过对该电路的控制,电源电压低于2.1 V 时SRAM 单元能快速切断电源,确保SRAM单元的电源能充分掉电,从而确保其电源电压能低于100 mV。若不能切断电源,电源上的残余电压完全可以处于300 mV 以上,导致下一次上电保持上一次的数据。另外通过对上电斜率的控制,在上电过程中避免噪声对SRAM 单元的数据产生决定性影响,使SRAM 单元更能体现其物理唯一性。

新SRAM 的单元结构如图4(b)所示。在原来的SRAM 电源端增加PMOS 管M7,通过上下的控制电路控制其导通或关闭。当其关闭后,SRAM 单元靠自身的漏电充分掉电;当其导通时,可以通过电源对SRAM 进行充电,斜率可由M7的导通电阻进行一定的调节。因外部电源在初始上电时可能较缓或由于系统等因素不受控,因而在上下电电路的控制下,能够在电源电压为2.1 V 左右时稳定有序上电,提升SRAM PUF 的稳定性。

图4 电路设计

4 测试结果

经0.35 μm 3.3 V/5 V CMOS 工艺流片验证,常温测试电源上下电电压在2.1 V 左右,全温范围(-40~85 ℃)测试结果为1.7~2.3 V。外部电源只要下电到1.7 V 以下,全“0”或全“1”的SRAM 单元阵列的电源就会被关断,再次上电后SRAM 单元整列的数据已经和掉电前的数据很不相同,可见电源控制电路可以让SRAM 充分掉电,而不受外部电源电压的影响。

为了验证SRAM 产生随机数的情况,使用优化后的单片机电路1 只,在室温条件下,读取芯片SRAM上电数据64 bit,分别统计“0”和“1”的个数,统计结果如图5(a)所示。由图5(a)可见,“0”和“1”的数据比较均衡。SRAM 部分单元阵列的“0”和“1”的物理分布如图5(b)所示,也可见其分布较均衡。

图5 SRAM 产生随机数的情况

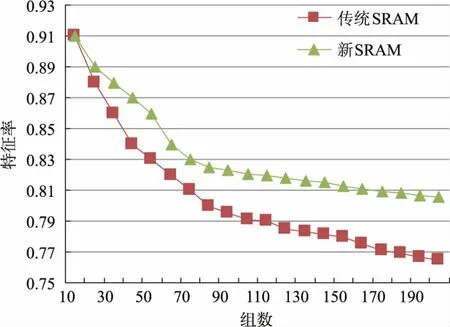

为了验证SRAM 上电特征率,在室温条件下分别对传统SRAM 和新SRAM 同一位置读200 组大小为64 bit 的SRAM 上电初始值。以10 组为步进直至200组,统计同一位置上固定不变位数的比例(上电特征率),统计结果如图6 所示。从图6 中可见,随着测试组数的增加,单片机中的SRAM 上电特征率逐渐减小,最后特征率趋于稳定,稳定值分别约为80%(新SRAM)和76%(传统SRAM)。新SRAM 单元相比传统SRAM 单元的上电特征率略有提升。

图6 传统SRAM 单元和新SRAM 单元上电特征率

从测试结果可知,单片机电源在未充分掉电的情况下,可以实现SRAM 的充分掉电,使得SRAM 单元的数据在上电过程中易实现其上电特征数值。SRAM单元不仅具有较均匀的数值分布,同时具有较好的唯一性,可以应用于密码安全技术中。

5 结论

本文提出了一种上电控制电路,对单片机中SRAM 的不可克隆物理特性进行上电优化;描述了SRAM PUF 在安全密钥方面的优势,同时分析了SRAM PUF 的物理特性。通过增加上电控制电路优化SRAM 单元上下电电压和时间,确保展现真实的SRAM PUF 的物理特性。流片验证后测试结果表明,该方法可以实现SRAM 单元数据在上电后的物理特征数值,相比传统的SRAM 电路结构具有更好的唯一性,已成功应用到单片机的设计中。