电离层测高仪高速采集系统设计

2020-04-18朱正平展旭强

朱正平,展旭强

(中南民族大学 电子信息工程学院,武汉 430074)

电离层是地球大气的一个电离区域,人类通过电离层传递信息,如无线电通讯、无线电导航、雷达定位等.当发生电离层暴和电离层不规则时,对电离层通讯和广播可能造成严重影响,甚至发生讯号中断问题.因此对电离层观测研究具有一定的科学价值[1-4].电离层测高仪是对电离层进行日常观测的设备,具体工作过程是从地面垂直向上发射频率随时间变化的无线电脉冲[5],在同一地点接收电离层反射的回波脉冲信号,通过接收机中数据采集系统将数据传输到上位机,测量出电波往返的时延,从而获得虚高与频率的变化曲线.

随着电子通信技术和计算机迅速发展,速度更快、性能更优的电离层测高仪的研制成为可能.其中测高仪的数据传输速度与精度是至关重要的.传统测高仪数据采集传输系统是基于ISA总线设计实现的.ISA总线是并行数据传输方式,受到位宽的限制,传输速率过低、CPU占用率高等缺点.PCIE总线[6,7]与ISA总线对比有以下特点1、在数据传输模式上,PCIE总线采用双工串行点对点传输模式,不受位宽的限制,串行收发数据同时进行,单向数据传输速度为2.5 Gb/s.2、所连接设备分配独享通道带宽,有多种规格配置PCIE ×1/2/4/8/16/32,能够满足将来不同传输设备的需求.3、串行传输抗电磁干扰能力加强,对于测高仪高频电磁干扰问题的解决起到重要作用.4、串行连接引入嵌入式时钟技术,即发送端不在向接收端发送时钟,接收端通过8bit/10bit编码从数据链中恢复出时钟.本文设计以PCIE总线的测高仪数据采集系统.方案采用不同以往的接口芯片来实现总线方式,选择以IP硬核模块完成总线设计.本文首先描述了电离层测高仪的硬件平台,然后介绍了数据采集系统硬件模块设计和软件模块的设计,在测高仪平台下进行探测采集,最后给出了采集系统的DMA读写速度和采集的频高图、原始数据图.

1 系统硬件设计

电离层测高仪是对电离层进行垂直观测的仪器,采用脉冲编码、频率交错等技术得到各种电离层参数.根据电离层参数可以分析电离层结构、电子浓度剖面和扰动等信息.测高仪由接收系统、发射系统、数据采集系统和上位机处理系统组成.系统结构框图如图1所示.上位机通过采集系统的自定义ICSA测高仪总线检测各个模块工作是否正常无误后下达发射命令到DDS信号源,信号源响应通过功率放大器和发射天线把1~30 MHz的电磁脉冲垂直发射到天空,信号经过电离层反射的作用在同一地点接收回波信号.电离层回波信号被两个垂直接收天线接收后在宽带滤波与本地DDS信号源进行混频,再中频滤波放大,最后输出两路同向分量I信号和正交分量Q信号.两路模拟信号经过ADC芯片(LTC2192)采集量化后的数据通过FPGA(EP4CGX150CF23C8N)进行相关解码运算经串并转换后对数据时序进行同步调整,确保高速信号的时序同步.再通过PCIE总线传输到上位机处理系统,得到频率与虚高变化的曲线图,即频高图.从图1中可以得出数据采集系统肩负着上位机指令的传输与电离层回波信号数据的采集任务,采集的精度与速度决定着频高图的质量,在测高仪中担任着重要的作用.

图1 测高仪系统结构框图Fig.1 Structure diagram of altimeter system

1.1 采集系统硬件设计

本文设计测高仪数据采集系统的硬件结构如图2所示.主要包括电源模块、晶振模块、IP硬核接口模块、FPGA控制模块、ADC模块等组成.

图2 采集系统硬件框图Fig.2 Acquisition system hardware block diagram

由于FPGA电源需要3.3 V、2.5 V、1.8 V和内核电压1.2 V,为了解决不同电源需求采用AMS1117系列低压差线性稳压器.FPGA参考时钟由100MHz的有源晶振提供其他模块的时钟由PLL分频,配置芯片选择EPCS4SI8N防止FPGA芯片断电程序丢失.IP硬核接口模块能够自动完成数据链路层和物理层的数据处理功能,减少了复杂的底层协议规范方便设计核心放在总线的应用层接口设计上,有利于缩短开发周期.FPGA控制模块是系统的控制核心,主要包括ADC模块控制、双口RAM模块、SRAM模块控制、DMA控制器等.首先ADC模块完成采集量化的回波数据,然后在双口RAM中进行缓存数据接着启动DMA模块,最后RAM采用乒乓模式通过DMA模块将数据不断取出通过PCIE接口传输到上位机处理系统,同时它还需要完成对ADC控制,配置ADC内部的控制寄存器.SRAM模块是存储上位机对测高仪硬件模块的控制指令.ADC模数转换器是采集系统的核心器件,主要是实现把回波模拟信号转换为数字信号.

1.1.1 ADC电路设计

LTC2192是一个双通道采样率为16位,单通道速度为65 Msps 的A/D转换器.由一个1.8 V单电源供电,具有高采样率、低噪声、低功耗等特点.为了减少数据线的数量,数字输出为串行LVDS,每个通道一次输出一位、两位或四位[8].LVDS驱动器具有可选的内部端接和可调节的输出电平,以确保信号完整性.LVDS输出还可以减少印刷电路板上的数字噪声同时简化PCB布局设计.

考虑到电离层回波信号为单端信号,而LTC2192的输入端为差分输入,需要在信号采样前进行信号调理.调理电路的核心是Mini-Circuits公司的ADT2-1T器件,是带有中心抽头的射频变压器驱动的模拟输入进行转换为差分信号,信号调理电路设计如图3所示.

中心抽头与A21_1VCM1偏置,将A/D输入设置在最佳直流电平.在较高的输入频率下,传输线变压器具有更好的平衡,从而降低A/D失真.设计能够调理输入频率从1~70MHz的信号转换,同时在模拟输入端有一个RC低通滤波器.此低通滤波器将驱动电路与A/D采样保持开关隔离,还限制了驱动电路的宽带噪声.

LTC2192外围接口电路设计如图4所示.AIN1+/AIN1-为差分模拟信号输入对,噪声对差分编码输入信号质量有很大的影响.噪声主要可通过电源输入端和模拟输入端进入转换器.模拟输入端已设计一个RC低通滤波器,对此在电源输入端以及在REFH和REFL参考电源引脚使用高质量0402封装旁路电容器,尤其重要的是该电容器应与ADC在电路板的同一侧,并尽可能靠近芯片来达到减少噪声作用.

图3 信号调理电路Fig.3 Signal conditioning circuit

图4 LTC2192外围接口电路Fig.4 LTC2192 peripheral interface circuit

2 软件设计

2.1 驱动程序设计

驱动程序是完成采集系统与上位机应用软件通信和数据交换的桥梁,PCIE总线驱动程序采用DriverStudio、DDK和Visual C++ 6.0开发完成的[9,10].本设计完成的应用程序主要实现以下功能:

(1)程序初始化,包括采集检测设备是否正常、对IP硬核进行参数配置、申请缓存数据的内存、基地址映射等.

(2)数据采集传输与处理,主要是实现回波数据采集传输到上位机以及上位机对数据进行数字信号处理.

(3)测高仪硬件系统的配置,主要是设置FPGA的参数包括DMA缓存、设置中断方式、采集程序任务的配置等.实现了上位机对硬件模块的控制功能.

2.2 应用程序设计

应用程序是完成对数据采集系统的控制和数据处理功能,其工作流程如图5所示.应用程序初始化,PCIE驱动程序检测:设备是否正确安装、基地址映射、数据缓存内存申请.成功初始化后通知主线程,主线程通过ICSA总线向硬件模块发送启动探测任务.发射系统立即进入到工作状态,此时采集系统进入到等待电离层回波信号状态.当采集系统完整无缺的将一个频点数据缓存到内存中后,采集系统对当前频点的采集任务结束进入到下一个频点的采集.同时在内存中的数据被上位机处理系统取出,采集和取出过程并行工作直到全部的频点采集完毕.此时采集得到的是原始数据需要经过进一步处理,上位机采用双机工作模式送入缓冲区中的数据通过网络端口传输,数据处理机启动数字信号处理解码差分算法、去噪等,将这个频点的结果显示在软件上等待着下一个频点数据一直循环到完成全部频点.本地存储数据是将原始数据和自定义DIF/ODF格式文件存在本地磁盘以方便研究使用.

图5 程序工作流程图Fig.5 Process flow chart

3 观测结果分析

3.1 DMA读写速度测试

为了验证本文设计的PCIE总线接口的传输性能,设计采用DMA传输模式测试其读写速度,在设计应用程序的同时结合Quartus Ⅱ开发环境使用Verilog HDL语言编写代码.其中主要的内容是IP硬核模块的设置有应用层接口模式(Avalon-ST 128-bit)、最大负载量(512 Bytes)、最大有效载荷写入(128 Bytes)、基地址寄存器大小、MSI中断设置等.依据DMA模式测试传输数据量,结果如图6所示.通过连续四十次速度测试,结果表明性能稳定无缺失数据求其平均值读速度为700 MB/s,写速度为630 MB/s.

图6 DMA读写测试Fig.6 DMA read write test

3.2 采集数据频高图

中南民族大学与中国科学院地质与地球物理研究所合作研制的测高仪(PDI2)运行于北京、武汉、海南地区进行长年的观测.将本文设计的PCIE总线高速采集系统结合测高仪平台经长时间运行性能稳定.频高图中数据经过反演可得出电离层电子浓度剖面、真高等信息.电离层的色散作用会将回波信号分解为两个圆偏振波在频高图中显示为O波(红)和X波(绿).电离层参数如真高的计算要用到O波和X波,另一个对于频高图标定也需要清晰完整的O波曲线,因此对于研究电离层的变化规律频高图的描迹曲线清晰完整很重要.

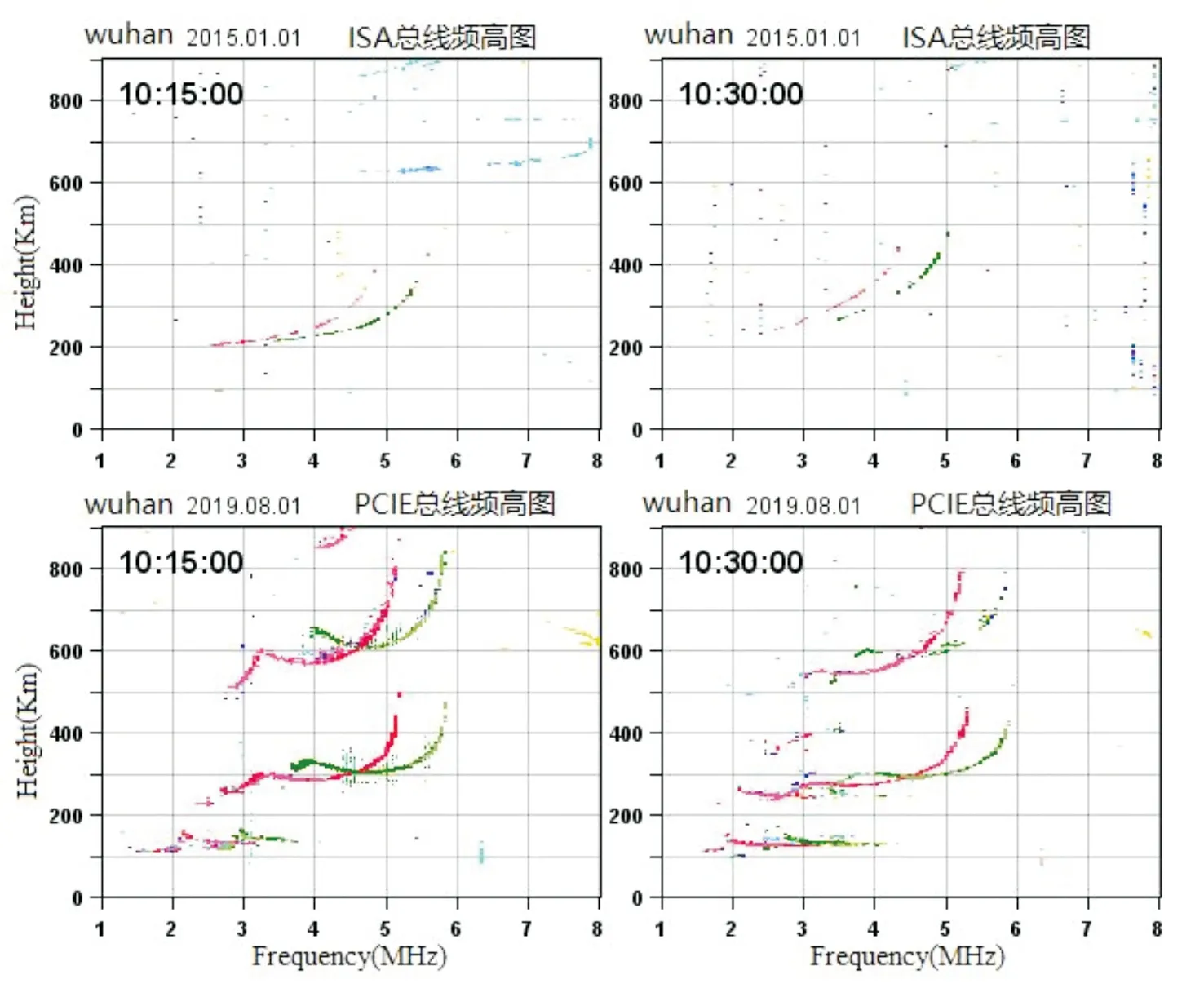

使用ISA总线数据采集系统存在采集精度低、传输速度慢等造成频高图数据不完整无法准确标定临界值影响电离层参数研究.图7、8分别给出了不同地区(武汉、海南、北京)的频高图结果.图7为武汉地区使用ISA总线和PCIE总线采集得到的频高图对比,采集时间间隔为15 min.图8为在海南和北京地区同一时间电离层测高仪基于PCIE总线采集得到的频高图,同为15 min间隔采集.

由图7可看出,对比原先的频高图使用本文设计的采集系统得到的频高图一次回波O波和X波更为清晰,还出现了清晰的二次回波信号曲线.原ISA总线采集得到的频高图一次回波O波和X波描迹不清,也不够清晰完整.在图8中海南和北京两个地区得到的频高图一次回波O波和X波均较为清晰.

图7 武汉地区ISA总线与PCIE总线频高图Fig.7 ISA bus and PCIE bus ionogram in Wuhan

图8 海南和北京地区PCIE总线频高图Fig.8 PCIE bus ionogram in Hainan and Beijing

3.3 原始数据图

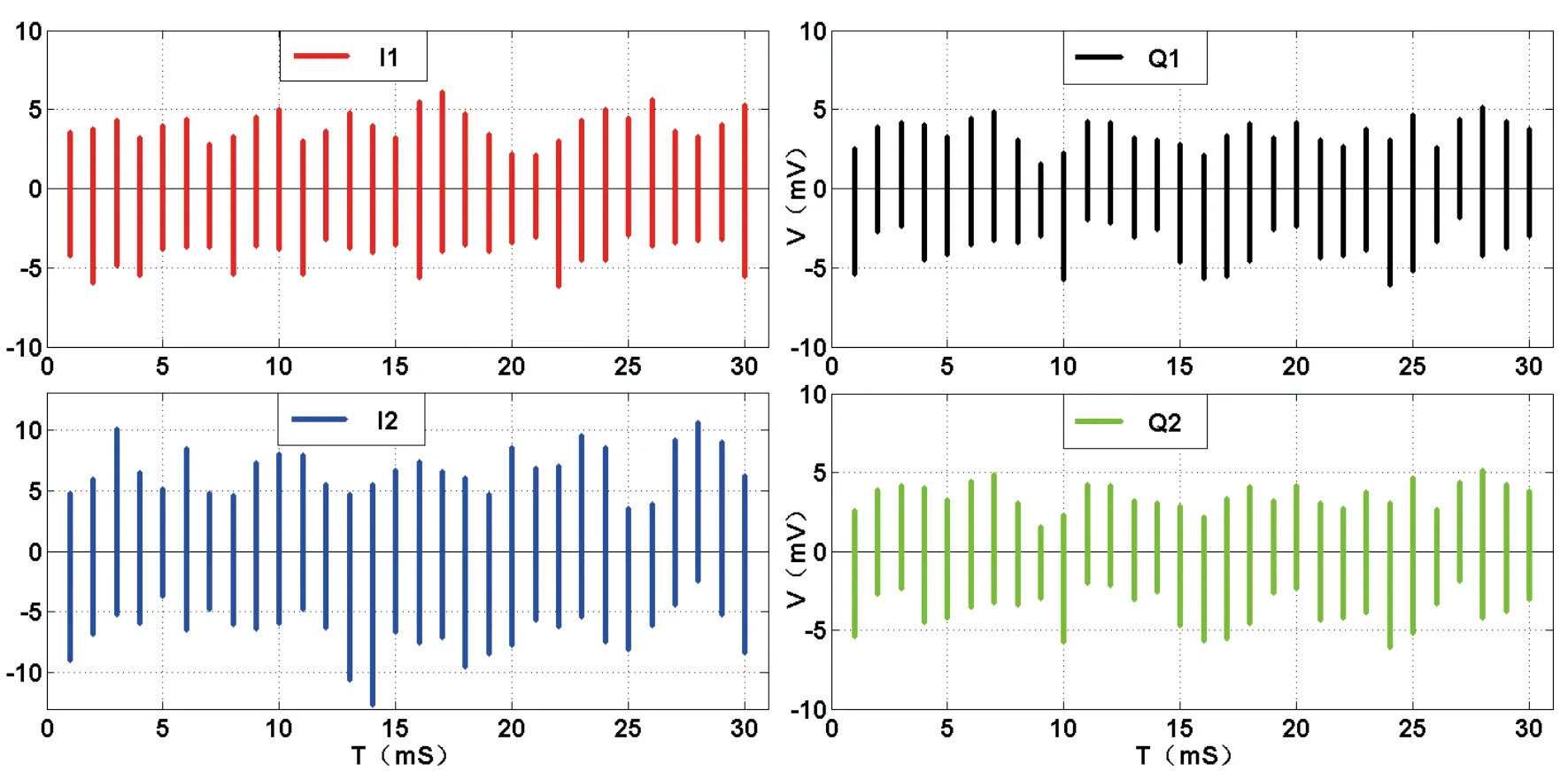

原始数据为测高仪采集未经过去噪、信道均衡等处理的数据.数据采用中南民族大学在2019年6月25日4:45 UT(国际时间)电离层测高仪采集得到的原始数据,利用MATLAB算法读取原始数据的信息,选择在9.3MHz频点主要原始数据格式自定义表1.

表1 频点原始数据格式Tab.1 Frequency point raw data format

从表1中可以得出探测脉冲信号是重复进行的,本次数据重复频率为32次.通过计算频率值与总频率个数得到频率分辨率为0.05 MHz.采集原始数据频率为1~16 MHz,数据结构存放按信息头和I1,Q1,I2,Q2的排列方式.利用MATLAB算法提取出I1,Q1,I2,Q2对数据进行矩阵处理按PulseNum* DataNumePerPulse方式排列得到结果如图9所示.可以得出I、Q的数据信号幅度.

图9 9.3 MHz I/Q信号幅度Fig.9 9.3 MHz I/Q signal amplitude

图10 O波与X波信号幅度Fig.10 O wave and X wave signal amplitude

通过I、Q数据可以计算得出原始的O波与X波幅度,测高仪接收天线为南北与东西垂直方向架设,设南北接收天线的复信号为YSN东西接收天线的复信号为YEW.定义如下:

YEW=I1+j·Q1,YSN=I2+j·Q2,

(1)

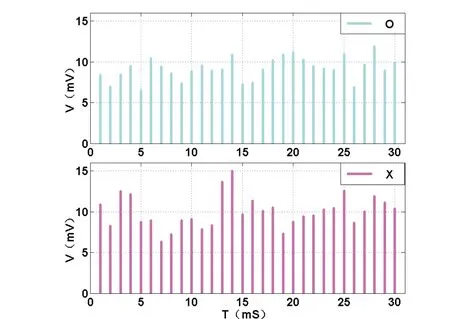

再按以下算法得到O波与X波的值,WO代表O波信号,WX代表X波信号其表示为:

(I1-Q2)+j(Q1+I2),

(2)

(I1+Q2)+j(Q1-I2),

(3)

其O波与X波幅度信息结果如图10所示.

O波与X波信号分离也是重要的,前提是要保证接收天线与接收机系统信号幅度和相位一致,但接收天线工艺、环境很难保证严格一致.可求出YEW通道相对于YSN幅度差值K,为解决双通道信号不均衡问题找到一种方法,接收系统根据不同频点相对幅度差生成通道补偿表用于系统校正.利用公式(4)得到相对幅度差值如图11所示.

(4)

利用采集系统在测高仪平台(PDI2)上运行采集得到的频高图一次回波O波和X波清晰,数据传输速度与精度性能都得到提升,利于缩短频高图采集时间.国际上的测高仪加密采集时间为每五分钟一次,而PDI2测高仪实现了加密采集时间为一分钟一次,是ISA总线所无法完成的,可用于研究多普勒频移(Doppler frequency shift).研究电离层多普勒频移对于研究电离层不同尺度的扰动与传播具有重要的作用.通过相位斜率方法将原始数据中多普勒进行提取,方法由公式(5)、(6)、(7)可得,其中φn是单个窄带回波信号的相位.

图11 通道相对幅度差值Fig.11 Channel relative amplitude difference

(5)

φ(ti)=Δω×ti+φ0,i=0,1,2,…,N-1,

(6)

(7)

图12 多普勒频移(Hz)与本地时间和扫描频率连续变化Fig.12 Doppler frequency shift (Hz) continuously changes with local time and scan frequency

4 结语

随着计算机及电子技术的不断发展,传统的ISA总线已满足不了性能更优的测高仪数据采集.为了提高测高仪采集精度及速度的性能,本文设计基于IP硬核PCIE 总线接口方案的采集系统.以FPGA作为系统的控制核心完成对ADC模块控制、时序控制、DMA数据传输等功能,在完成驱动程序与上位机应用软件的基础上进行系统探测采集.结果表明:设计的PCIE总线数据采集系统传输速度快,得到频高图O波、X波清晰,较传统的ISA总线数据采集系统更优,得到的多普勒频移可用于研究电离层不规则体的发生.此外本设计还引出足够的GPIO接口以方便进行系统再次开发,可适应日后功能更强的测高仪.