三维封装中的并行键合线信号仿真分析

2017-03-27王祺翔曹立强周云燕

王祺翔,曹立强,周云燕

(1.华进半导体封装先导研发中心,江苏 无锡 214135;2.中国科学院大学,北京 100049;3.中国科学院微电子研究所,北京 100029)

三维封装中的并行键合线信号仿真分析

王祺翔1,2,3,曹立强1,2,3,周云燕1,3

(1.华进半导体封装先导研发中心,江苏 无锡 214135;2.中国科学院大学,北京 100049;3.中国科学院微电子研究所,北京 100029)

当今便携式设备的速率可达数吉比特每秒,但是其通道的频宽限制其性能。在所有芯片与基板的传输结构中键合线是最常用的,但却渐渐成为了带宽主要的限制。基于一款高密度布线系统级封装的研发项目,使用全波电磁场仿真工具进行建模分析,研究了不同参数对键合传输线DDR单端信号与差分信号传输质量的影响。最终通过键合线设计的优化,仿真结果通过了眼图的验证。

键合线;系统级封装;DDR;单端信号;差分信号

1 引言

随着半导体技术的进步,使得芯片的特征尺寸逐渐缩小,传统的光刻工艺逐渐趋于极限。为保持集成电路的发展,联合系统级芯片与系统级封装的高价值系统成为了新的解决方案。微电子的进步最终使得信号的频率不断增高,而通用的键合传输线结构逐渐成为了制约频宽的关键因素[1]。键合引线参数多,波导结构更局限与不均衡。如果没有合理的设计方案,信号的损耗将难以接受。本文基于对一款三维系统级封装中控制芯片与存储芯片的 DDR 信号互连进行研究,实现了一种通过系统仿真眼图验证的高密度互连,为今后各种高密度高频的引线键合设计提供了优化参考方案。

2 键合线的电学传输模型

在微波多芯片组件(MCM)中,键合线互连是实现微波多芯片组件电气互连的关键技术。目前很多新技术可以代替键合线实现信号传输,如倒装焊、刻蚀通孔等,但键合线仍因工艺简单和价格低廉在实际生产中普遍采用。随着频率的升高,键合线的长度、弧高、间距和数量对微波传输特性有很大的影响[2]。

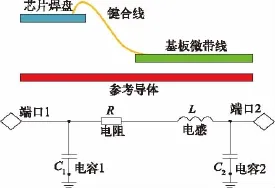

通常情况下,微带线之间的键合线互连结构及等效电路模型如图1所示。其等效电路模型可以简单地用并联电容 C1、串联电阻 R 和串联电感 L、并联电容C2组成的低通滤波器网络表示,该模型中起主要作用的是键合线的串联电感 L,而并联电容 C1和 C2很小,可以用开路短截线近似求得。适当增加键合传输线的宽度以提高并联电容可以在一定频带范围内补偿串联电感的作用。

图1 键合线互连模型与等效电路图

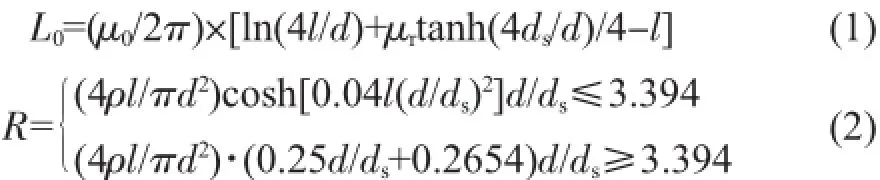

对于自由空间长度为 l、直径为 d 的圆形键合线,其电感和串联电阻 R 可分别由式(1)、式(2)表示:

式 中:μ0为空气介质的磁导率(μ0=4π×10-7H/m); μr和 ρ分别为键合线材料的相对磁导率和电阻率;ds为键合线的趋肤深度。由于趋肤深度f为频 率),且在微波波段通常ds/d<<1,结 合 L0和 R 的 公式可知电感 L0随频率的变化很小,而串联电阻几乎与频率的平方根成正比变化[2]。

以上是当参考的导体为以一均衡共面、类似低频共地短接的情况。实际键合传输线的参考导体并不理想,应根据实际的频率及波导结构建立等效的电路模型而确定。本文中研究的参考导体为芯片与基板互连前仅能依靠键合线传输,即参考导体与传输导体的电路模型相仿,信号完整性更差[3]。

3 键合线的电学仿真

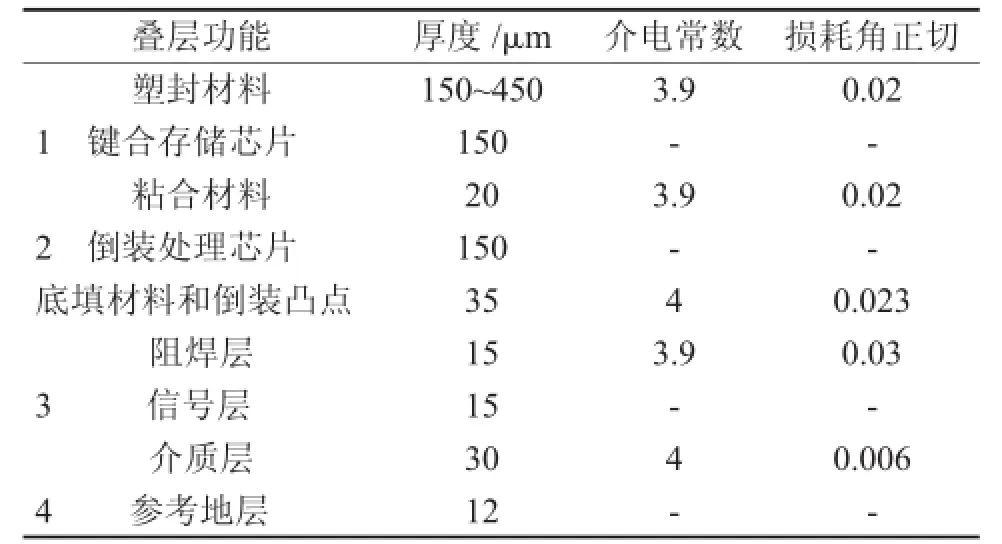

在本文中假定电源线对信号线没有影响并与地线一样为其提供参考面,即地电之间阻抗极小,可忽略不计。芯片本身的焊盘分布上每两条DQ数据线以及数据选通 DQS差分信号线被一对地电线环绕,起始焊盘的位置、间距固定无法改变,为了保证工艺的可靠性,键合线按照焊盘的顺序分布没有交错,保持制造容差使 finger焊盘间距大于芯片原始焊盘分布,相对原芯片焊盘间距均扇出一定角度。表1是该系统级封装的上层叠层信息。

表1 叠层信息

3.1 模型接地与铺地回路仿真分析

先建立初期设计模型,设定最小键合线纵向引线距离为3000μm。建立工艺最小的键合线高度以保证最大的集成度与性能。最小的键合线高度也能使得键合线信号传输距离更短,与表层参考面更近,信号质量尽可能做到最佳[9]。finger 焊盘为最小设计规则的简化长方体模型,最小间距 50μm,键合线宽为 20.32μm,保证小尺寸finger焊面的可靠性与表层高密度布线,图2为键合线模型示意图。

图2 键合线模型

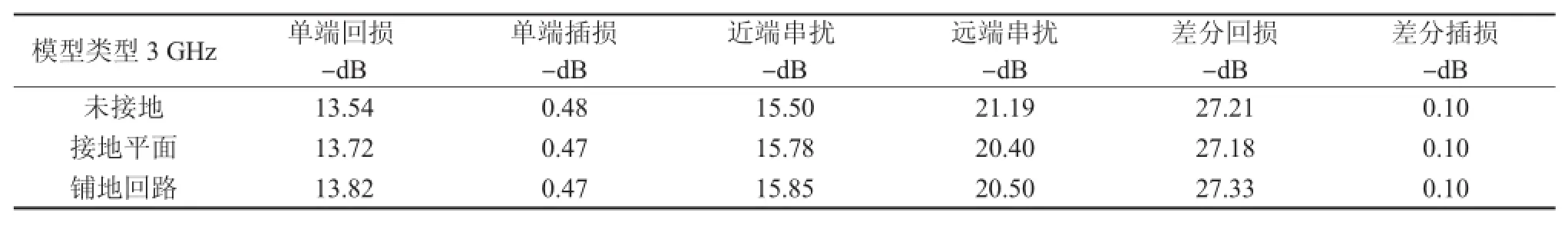

表2 是 S 参数仿真结果,从中可以看出,当键合线末端 finger接第二层地平面后,信号质量不论插入损耗还是回波损耗皆普遍优于未接地之前。回波损耗最大改善低于0.2dB,插入损耗最大改善低于 0.01 dB。由于末端增大了返回路径,一定程度上改善了波导通道的传输阻抗,但也在客观上增加了一定的传输距离,近端串扰由于回路改善而略有减小,最大低于0.3dB。远端串扰由于传输距离增大而略有增大,增幅低于1dB。

表2 3GHz S参数仿真结果

差分线的差模信号主要通过信号两端的地返回路径和两信号间传播,从仿真结果上看,接地与否几乎没有差别,铺地回路也仅是略优于接地情况。从以上结论中可以看出,不论差分信号以及单端信号,信号返回路径接地与表层铺地对于键合信号传播改善很小。实际的基板布线密度非常高,信号还有一定的时序要求,除了基本的线宽、线距外还需要更多的布线面积,以下的仿真分析皆只采用了高效的接地优化方案。

3.2 键合线 GSSG(Ground&Signal)横向 finger 焊盘分布仿真分析

下面讨论 GS finger 焊盘间距以及SSfinger 焊盘间距对单端及差分信号完整性的影响。当信号finger焊盘间距保持50μm时,设置地焊盘间距由原来的50μm到300μm。

图3 GS间距50μm到300μmDQ信号回波损耗与插入损耗

图3 显示单端线的回波损耗随着地焊盘的远离逐渐增大,插入损耗不断减小,这是由于参考线的远离导致导体间的信号传播质量变差。串扰随着GS距离的增大而提高,当参考平面距离同信号距离相比越小时,信号与参考面的耦合传播效应将大于信号线之间的有害串扰效应,降低参考面与信号导体之间的距离对于信号本身的传播以及串扰都有积极的影响。

差分信号同单端信号一样,反射损耗将随着参考线的远离阻抗失配加大而增大,插入损耗逐渐减小。但是参考线距离加大对差分线插入损耗远远小于以上任何一种效应,因为差分信号传播当参考面较信号耦合弱时主要以信号导体间传播为主[10]。不论对于差分键合线还是单端键合线,GS finger焊盘距离的增大都会使其传播信号的质量减小,随着GS距离的增大,对信号质量的影响愈发减弱,在这方面差分键合线比单端键合线趋势更明显。

下面固定 GSSG 键合线波导传输结构的整体范围,讨论当两端 GG(Ground&Ground)间距为 770μm时,SS(Signal&Signal)间距从50μm到550μm时 ,单端键合线和差分键合线的波导传输能力。

图4 SS间距50μm至550μm DQS信号回波损耗与插入损耗

当信号线间距从50μm到550μm时单端信号的传输质量会呈现微小的波动变化。起始随着SS距离的增大、GS距离的相应减小会改善整体的末端传播阻抗,使得信号略有改善,后期虽然保持优化 GS 间距但也增加了整体的传输距离,反射损耗减小,插入损耗降低。从图4 中可以看出,改变SS横向距离对差分DQS 的信号影响最大,SS距离的增加使得差分键合线的回波损耗增大,插入损耗减小,信号质量变差,而当SS距离从450μm到550μm时信号质量开始回升,这是由于差分对SS间距增大的负面影响接近饱和而GS间距的减小使得末端阻抗得以改善所致。

因此对于单端DQ信号线而言,当GG间距一定、使得SS信号有一定的调整范围时,减小GS的间距、加大SS的间距可以减少串扰,提高整体的信号质量。对于差分 DQS 信号线而言,减少SS间距可以使得差分线间的耦合作用更强,针对键合线这种最紧耦合波导传输结构是保持信号质量最好的方式。

3.3 键合线纵向参数仿真分析

在对上述不同方案 GSSG 波导传输键合线横向参数进行研究后,这里对最紧密的 GSSG 结构做纵向距离调整。由于下层 AP 芯片边缘为纵向2000μm左右,设定为纵向2500μm、3 500μm、4 000μm加以讨论。实际2500μm过于靠近芯片边缘并且布线调整面积紧张较难实现,这里的设定主要为了研究和讨论。超过4000μm,同样工艺上良率会有影响,也会干扰后排其他信号布线并加大 DDR芯片信号至AP芯片整体的信号走线长度,增大损耗、降低信号质量以及占用更多的布线面积。

图5 纵向 2500μm至4000μm最紧密GSSG DQS信号回波与插入损耗

图5 展示了差分线信号的变化,不论单端信号线还是差分信号线,键合线的长度越长信号的质量越差,由于键合线的长度越长将会导致键合线间耦合距离加大,因此会使得信号的串扰问题越来越严重,因此键合线越短,对信号质量的优化越大;而且随着键合线的缩短,从 finger焊盘到倒装控制芯片焊盘的信号走线越短。再结合 3.2中的结论,对于DQ等单端信号,要适当地增加SS距离,因为当SS距离增加时,由于角度的扇出,最终会使得键合线的传输长度增大,信号损耗严重。

3.4 键合线紧密排列仿真分析

上述的讨论都是建立在 GSSG 键合线波导传输没有外加影响的情况下,实际的DQ单端信号焊盘和DQS差分信号焊盘都是分别排列在一起的,这里对比研究实际中在外界串扰作用下对处于中间的单端以及差分信号传播情况的影响。

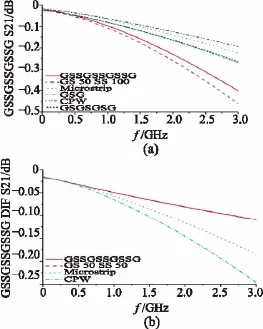

图6 DQ信号与DQS信号插入损耗对比

图6 得出了与预期相反的惊人结果:紧密排列最终使得信号的质量优于没有外在影响的情况。这是由于紧密排列波导传输导体的增多使得整体信号的传播阻抗更加均匀,减少了键合线扇出角度及高度弯折造成的二维平面传输结构变化。差分线和单端线的回波损耗也由于紧密排列有所减小。这是因为增加了传输导体和整体的波导结构,虽然对中间的DQ信号的串扰增大,但由于周围地键合线的屏蔽使得这种负面效应非常微弱,最紧耦合的排列方式反而使得信号的质量得到了提升。

图6(a)DQ 插损的对比采用 3.2中得出的单端优化方案(GS 50μmSS 100μm,减少串扰)进行对比,发现还是紧密排列传输方式质量更高。同时采用GSG间距为50μm与GSGSGSG的紧密排列方式验证得出结论,紧密排列同样略优于无外加影响的方式。从而可以得出:只要引线键合芯片的焊盘分布较为合理,键合线紧密排列多导体传输会保持最好的信号质量。图6(a)中还验证了表面微带线3000μm和平面波导结构,这里采用设计最小的20μm/20μm线宽线距,可以看出CPW单端传输能力优于普通微带线,远高于原键合线传输结构[1],工艺允许条件下单端信号尽量通过平面走线传播。

图6(b)通过差分信号的插损结果可以得到和3.2节仿真分析GS间距对差分信号质量中类似的结论。在紧耦合情况下,差分线的抗干扰能力很强,不论周围是否有键合线,插入损耗几乎没有变化,结果在仿真中重合。表层采用 CPW 的方式传播差分信号反而使得差分信号的插入损耗减小,这是由于间距20μm小于与地层的间距30μm,导致差模阻抗减小、失配增加,差分键合线匹配程度反而高于平面走线。

3.5 DDR系统眼图仿真分析

图7 是Ansys designer下DDR信号眼图仿真的电路图,从之前优化的DQ、DQS键合传输线末端建立等长并行时序约束表层走线至倒装芯片对应网络焊盘处,从而完成整体系统互连结构。求解对应传输结构 S 参数的仿真结果以建立 N-port无源模型。导入行为级模型,建立两芯片的驱动端和接收端。图中仅示意了LANE1中DQ0信号在write模式下所建立的系统仿真DDR电路图,其余链路可依次导入建立模型添加激励、探头等进行仿真。

图7 系统仿真DDR电路图

图8 为LANE1至LANE4 所有仿真链路的DQ及DQS的眼图结果,所使用的分析码型是伪随机码,从图中可以看出信号的时序正确,眼高眼宽良好,有足够的建立时间及保持时间,从而验证了通过上述布线方案可以实现高密度信号走线的系统级传输。

图8 DQ和DQS全链路系统仿真眼图

4 结束语

本文针对一款引线键合芯片与倒装芯片的三维堆叠系统级封装中的DDR信号完整性问题,研究得出以GSSG键合线波导传输模型为主的影响单端信号以及差分信号质量的不同因素,并且提出了优化方案。根据研究成果,最终实现了高质量的信号传输。建议引线键合芯片焊盘分布设计的工程师们合理设计地电与信号输出分布,以使得针对未来高堆叠长距离高弧度的键合线,在最小设计规则的紧密排列下达到更好的信号传输效果。

[1]Dong Gun Kam,Joungho Kim,Jiheon Yu,etal.PackagingA40-Gbps serial link usingAw ire-bonded plastic ball grid array[J].IEEEDesign&Testof Computers,2006,23(3): 212-219.

[2] 徐兴福,高宽栋,任建,等.HFSS 射频仿真设计大全[M].北京:电子工业出版社,2015.

[3]Huang-Kuang Kung,Bo-Wun Huang,Hsiang-Chen Hsu. Theeffectof cross-section geometry of bonding wire onw ire sweep for semiconductor packages [C].M icrosystems Packaging Assembly and Circuits Technology Conference (IMPACT).IEEE,2010:1-4.

[4]毛忠宇,潘计划,袁正红.IC 封装基础与工程设计实例[M].北京:电子工业出版社,2014.

[5]Jitesh Shah,San Jose. 金 线 键 合与铜线键合的性能比较[N].半导体国际,2010.

[6]丁雨田,曹军,许广济,等.电子封装 Cu 键合丝的研究及应用[J].铸造技术,2006,27(9):971-974.

[7]Huang-Kang Tseng,Mei-LingWu.Dynamie simulation for microelectronic packaging of Al pad/underlying pad structure during copper wire bonding [C].2014 9thInternational M icrosystems,Packaging,Assembly and Circuits Technology Conference(IMPACT).IEEE,2014: 250-254.

[8]Ivy Qin,Hui Xu,Basil M ilton,et al.Process optim ization and reliability study for Cu wire bonding advanced nodes [C].2014 IEEE 64thElectronic Components and Technology Conference(ECTC).IEEE,2014:1523-1528.

[9]杨玲玲,孙玲,孙海燕.IC 封装中键合线传输结构的仿真分析[J].电子与封装,2014,14(9):1-4.

[10]Stephen H Hall,Howard L Heck. 高 级 信 号 完整 性 技术[M].张徐亮,鲍景富,张雅丽,于永斌,译.北京:电子工业出版社,2015.

The Simulation Analysis of Parallel Bonding W ire Signal in a3DSystem-in-Package

WANGQixiang1,2,3,CAO Liqiang1,2,3,ZHOU Yunyan1,3

(1.National Center for Advanced Packaging(NCAPChina),Wuxi214135,China; 2.University of Chinese Academy of Sciences,Beijing 100049,China; 3.Institute of Microelectronics,Chinese Academy of Sciences,Beijing 100029,China)

Today's portable electrical devices can run atgigabits per second(Gbps),but the bandw idth of the channel lim its its performance.Among all the transm ission structures between the chips and substrates,the bonding w ire is the most commonly used, but it is becom ingAmajor bandw idth constraint.This paper is based on the research and development projectof high-density w iring System-in-Package.Modeling analysis is conducted w ith the full-wave electromagnetic field simulation tools to research the influences of different parameterson DDR single-ended and differential signal transmission quality of the bondingw ire transm ission line.Finally,through the optimization of bonding w ire design,the simulation results were verified by eye diagram.

bondingw ire;System-in-Package;DDR;single-ended signal;differentialsignal

TN403

A

1681-1070 (2017) 03-0013-06

王祺翔(1992—),男,朝鲜族,吉林长春人,硕士,主要研究方向为系统级封装设计与电学仿真;

2016-11-21

曹立强(1974—),男,博士,研究员,主要从事系统级封装和先进封装的有限元建模;

周云燕(1980—),女,博士,研究员,研究方向为电磁仿真方法学与电磁仿真软件设计。