基于 BCD工艺的模拟多路复用器设计

2017-03-27臧凯旋范晓捷

臧凯旋,范晓捷,丁 宁

(中国电子科技集团公司第 58 研究所,江苏 无锡 214072)

基于 BCD工艺的模拟多路复用器设计

臧凯旋,范晓捷,丁 宁

(中国电子科技集团公司第 58 研究所,江苏 无锡 214072)

基于 BCD 工艺设计了一款模拟多路复用器。电路支持单电源或双电源供电 (单电源2.5~5.5V,双电源±2.5 V),内含 32 个 CMOS 开关,通过 5~32 译码器实现 32 选 1 功能。采用 SM IC 0.18μmBCD 工艺流片,电路经测试验证,关键参数导通电阻和传输延迟达到设计要求。

CMOS开关;电平转换

1 引言

多路复用器(MULTIPLEXER,也称为数据选择器)用来选择数字信号通路;模拟开关传递模拟信号,因为数字信号也是高低两个模拟电压组成的,所以模拟开关也能传输数字信号。在CMOS多路复用器中,因为其数据通道也是模拟开关的结构,所以也能用于选择多路模拟信号。用CMOS多路复用器传递模拟信号时需注意,模拟信号的变化值必须在正负电源电压之间,当传递有正负半周的正弦波时,必须使用正负电源且电源电压大于传递的模拟信号峰值,这时其控制或者地址信号必须以负电源电压为0,以正电源电压为 1[1~2]。

本文介绍了一款通用的模拟多路复用器,电路实现32选1的功能,可以传输在电源范围内的模拟信号,具有较快的传输速度以及较低的导通电阻。电路基于 BCD 工艺设计制作,性能可靠,实用性强[3]。

2 电路整体结构和功能分析

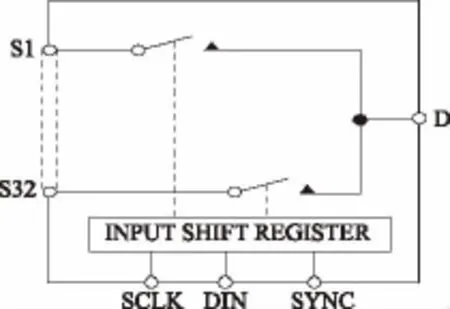

本文设计的模拟多路复用器由 CMOS 开关、输入串行寄存器模块组成,如图1所示。

图1 总体电路框图

该产品为 32路选 1 模拟多路复用器,从端口S1~S32 输入32路信号,其中一路开关导通,从端口D输出信号。输入串行寄存器模块包含8位寄存器、5位锁存器以及5~32的译码器[2]。输入时钟信号SCLK控制数据的输入,在时钟的下降沿时存储数据。当SYNC变为低电平,在时钟SCLK的下降沿,数据从端口DIN输入,存储于寄存器单元,直到寄存器单元存储8位数据,其中5位地址经过5~32译码器的译码,控制32位开关中的一位导通。

3 关键模块设计

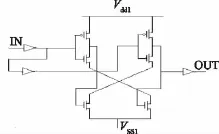

3.1 电平转换电路

输入串行寄存器模块的输入信号为数字逻辑电平,如图2所示,本模块将逻辑高电平转变为正电源,低电平转换为负电源的模拟信号;逻辑信号经过前两级反相器转换为高电平为正电源电压、低电平为地的信号;这个信号再通过下一级转换为高电平为正电源电压、低电平为负电源电压的信号;最后一级结构将转换后的信号整形。

图2 电平转换电路

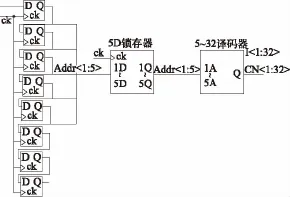

3.2 输入串行寄存器结构

如图3所示,输入串行寄存器结构的主要功能为实现 32 选 1 的功能。SYNC 变为低电平,在时钟SCLK 的下降沿,数据从端口 D 串行输入,存储于寄存器单元,直到寄存器单元存储8位数据,其中前 5 位数据为地址,存储于锁存器中;5位被锁存的地址通过5~32 译码器实现 32 选 1 的功能。

图3 输入串行寄存器结构

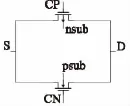

图4 CMOS开关

图5 浮动衬底结构

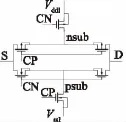

3.3 CMOS 开关电路

由于衬底偏置效应的影响,CMOS导通电阻在不同输入电压下差异非常大,通道导通电阻平滑度较差;为此,电路采用浮动衬底结构,如图4 、图5 所示。开关管的衬底分别接在浮动电位nsub、psub上;当开关关断时,nsub连接到VDD,psub连接到VSS,防止出现源端和衬底的 PN 结导通的情况;当开关开启时,衬底根据输入端电位调整,减小衬底偏置效应,同时保证反偏 PN 结关断[4~5]。

4 版图设计与仿真测试验证

4.1 版图设计

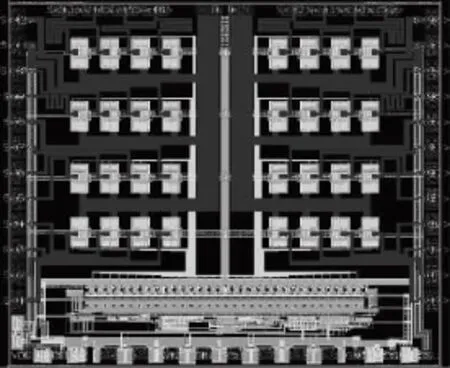

该电路版图采用 SMIC0.18μmBCD工艺设计规则进行设计,芯片面积 3.0mm×3.0mm,如图6所示。

图6 电路版图设计

4.2 仿真分析

选用SMIC 0.18μmBCD 工艺模型,在电源电压VDD为 2.5~5.5 V、±2.5V以及全温 T 在-55~125 ℃范围内,利用 HSPICE 仿真软件对所设计的电路进行仿真验证。下边以电源电压VDD=5V时的仿真情况为例,对仿真结果进行说明。

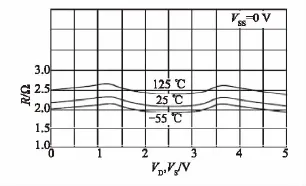

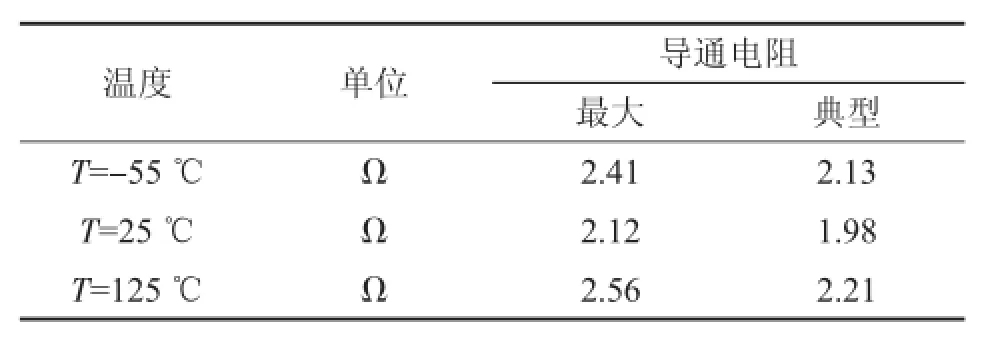

图7是对 CMOS开关导通电阻随传输电压变化的仿真波形,从图中可以看出,传输电压在 0~5 V电源电压范围内,温度分别为-55℃、25℃、125℃,导通电阻的变化曲线、电阻的平滑度在1Ω范围内。

图7 CMOS导通电阻

表1 CMOS导通电阻仿真结果

传输的延迟时间为时钟下降沿到数据传输到输出端,本电路的延迟时间仿真波形如图8 所示。

图8 传输延迟时间仿真验证

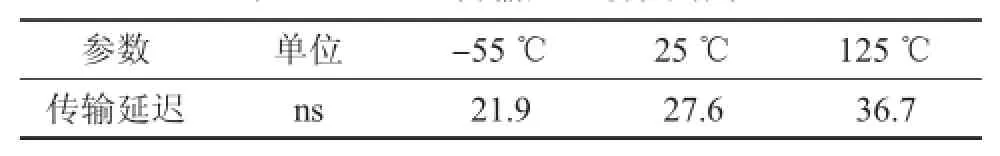

表2 CMOS传输延迟仿真结果

4.3 测试验证

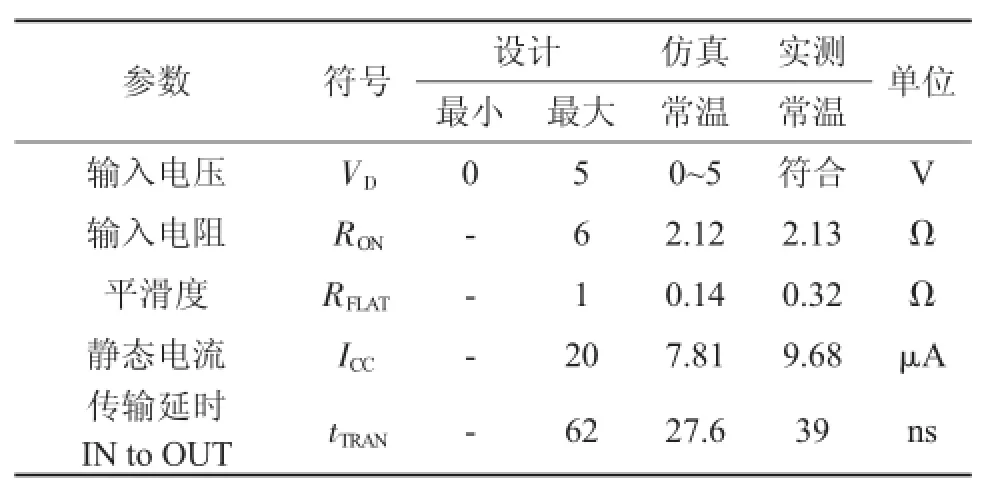

电路在 SMIC 0.18μmBCD工艺线上完成流片,电路功能与电参数达到设计要求。在电源电压VDD为2.5~5.5 V、±2.5V以及全温T为-55~125℃范围内,电路均能正常工作。在VDD=5V时,电参数的实测与仿真数据如表3所示。

表3 电路实测结果

经表3仿真与实测数据的对比分析可知,导通电阻、传输延迟等参数实测结果与仿真一致,符合设计预期。

5 结论

基于0.18μmBCD 工艺,设计了一款通用的模拟多路复用器,实现32选1的功能,可以传输在电源范围内的模拟信号,具有较快的传输速度、较低的导通电阻。功能与电参数达到设计要求,符合预期。

[1]毕查德·拉扎维.模拟 CMOS 集成电路设计 [M].西安:西安交通大学出版社,2003.

[2]苏晨,张世文,石红.一种单刀双掷高速模拟开关的研制[J].微电子学,2006,36(6):814-816.

[3]吴建辉.CMOS 模拟集成电路分析与设计 [M].北京:电子工业出版社,2004.

[4]李洪明.数字集成电路讲座第八讲:模拟开关[J].电子时间,1999,30(3):49-50.

[5]何茗,杨谟华.一种高性能高动态范围 CMOS 模拟开关[J].微电子学,2004,34(4):479-481.

Design of BCD-Based Analog M ultip lexer

ZANG Kaixuan,FAN Xiaojie,DINGNing

(China Electronic Technology Group Corporation No.58 Research Institute,Wuxi214072,China)

In the article,an analogmultiplexerbased on BCD technology ispresented.The device isdesigned to operate on eitherAsingle or double supply (single supply:2.5~5.5 V;double supply: ±2.5 V).The device includes 32 CMOS sw itches and achieves 1/32 function choice using 5~32 decoder.The circuit is of SM IC 0.18μmBCD technology.Test results show that key parameters of conduction resistance and transmission delaymeet thedesign requirements.

CMOSsw itch;levelshift

TN402

A

1681-1070 (2017) 03-0029-03

臧凯旋(1986—),男,安徽砀山人,2013 年毕业于电子科技大学微电子与固体电子学院,硕士学历,现在中国电子科技集团公司第 58研究所从事模拟集成电路设计研发工作,主要研究方向为模拟开关、存储器等。

2016-7-14