多电源域集成电路静电放电试验方法研究

2017-03-27姜汝栋蔡依林李小亮

姜汝栋,蔡依林,李小亮

(1.中国电子科技集团公司第 58 研究所,江苏 无锡 214035;

2.中国电子技术标准化研究院,北京 100007)

多电源域集成电路静电放电试验方法研究

姜汝栋1,蔡依林2,李小亮1

(1.中国电子科技集团公司第 58 研究所,江苏 无锡 214035;

2.中国电子技术标准化研究院,北京 100007)

随着集成电路技术的发展,电路从原来的单一电源域向多电源域进行转移,而其中的静电放电 (ESD) 试验是考核集成电路性能的一项重要指标,如何有效选择合适的试验方法变得越来越重要。结合国内外相关静电放电试验标准,研究标准之间存在的相同和不同的地方。结合实际情况,探究多电源域集成电路静电放电试验方法的选择。

静电放电;试验方法;多电源域

1 前言

静 电 放电(ESD,Electro-Static discharge),是 指 处于不同静电电位的两个物体间电荷的转移。ESD 是一种常见的近场危害源,可形成高电压、强电场、瞬间大电流。ESD 脉冲产生的瞬间大电流会对集成电路产生非常严重的损伤,而且该损伤是不可逆的,因此抗静电放电的能力成为检验集成电路的一项重要指标。在1982 年,美国专家志愿者协会在美国成立了 ESD 协会,专门从事静电防护理论和实践的研究,在此之后建立了部分静电放电模型和相关的标准。

目前国内对于集成电路静电放电试验使用的标准大致分为两种:一种是国军标,还有一种是 JEDEC标准。两者之间存在相似和不同的地方。本文重点介绍多电源域集成电路人体模式静电放电试验在运用两个标准时的相同和不同点。

2 试验方法

2.1 国军标静电放电试验方法

首先介绍国军标中关于静电放电敏感度的试验方法。

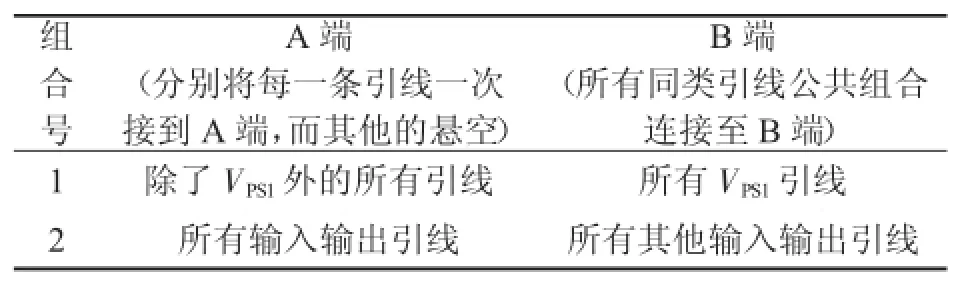

我们以最新的GJB845B-2005 方法3015来说,国军标中规定样品数量为3个,标准中要求试验需要按照电路的引线组合进行打击,每次打击正负3个脉冲,脉冲之间间隔大于 1 秒,具体的试验引线组合见表1。

表1 国军标试验引线的组合

根据表1可知,A端为脉冲进入端口,B端指接地端口,在进行组合1试验时,我们需要将不同的电源引线或者电源引线组合(如VCC1,VCC2,VSS1,VSS2等)接入B端,而其他每条引线一次接入A端,除了当前接入A端的那条引线和接入B端的电源引线或引线组合,其他所有引线必须悬空。在进行组合2试验时,所有的电源引线或引线组合必须悬空,依次将每条输入输出引线接入A端,而除了当前接入A 端的输入输出引线,其他所有输入输出引线全部接入B端。

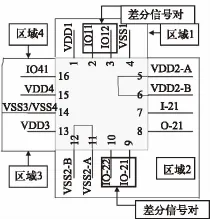

我们以具体的多电源域电路来详细解读一下国军标中静电放电敏感度的试验方法,见图1。

图1 样品电路引脚定义图

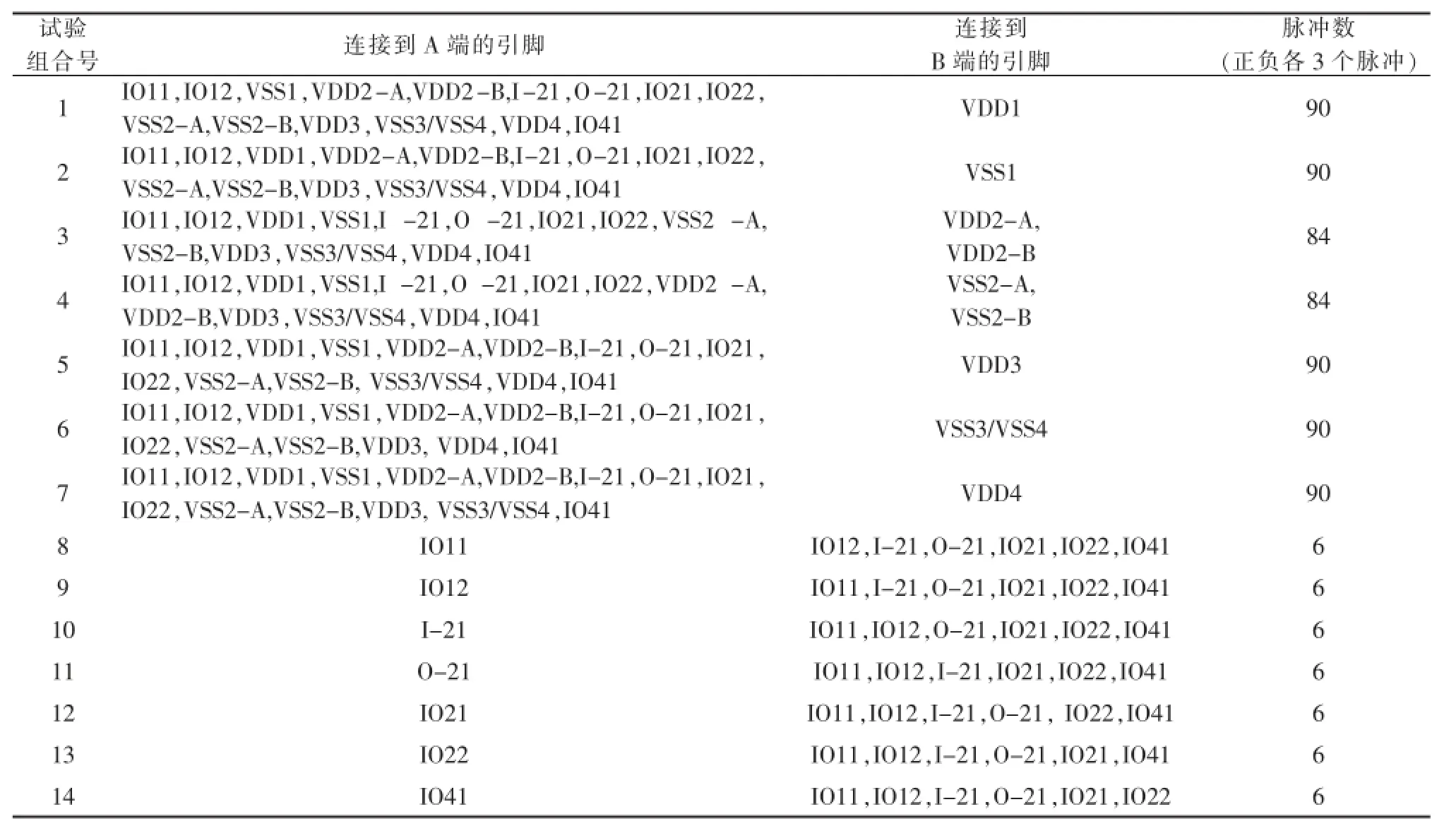

从图1中可以看出,该样品电路总计4个电源域,VDD2-A、VDD2-B 在芯片内部短路在一起,VSS2-A、VSS2-B 在芯片内部同样也短路在一起,并且在区域 1和区域2中各有一对差分信号。因此我们结合表1国军标中静电放电的试验方法,可以得到以下的打击方案,见表2。

表2 样品电路国军标打击方案

运用国军标静电放电试验方法,脉冲数总计 660个,而且电路引脚 VDD2-A 和 VDD2-B、VSS2-A 和VSS2-B 作为B端时是连接在一起连接到设备地上,而作为A端时每个引脚都是独立的,需要分别打击。

2.2 JEDEC 静电放电试验方法

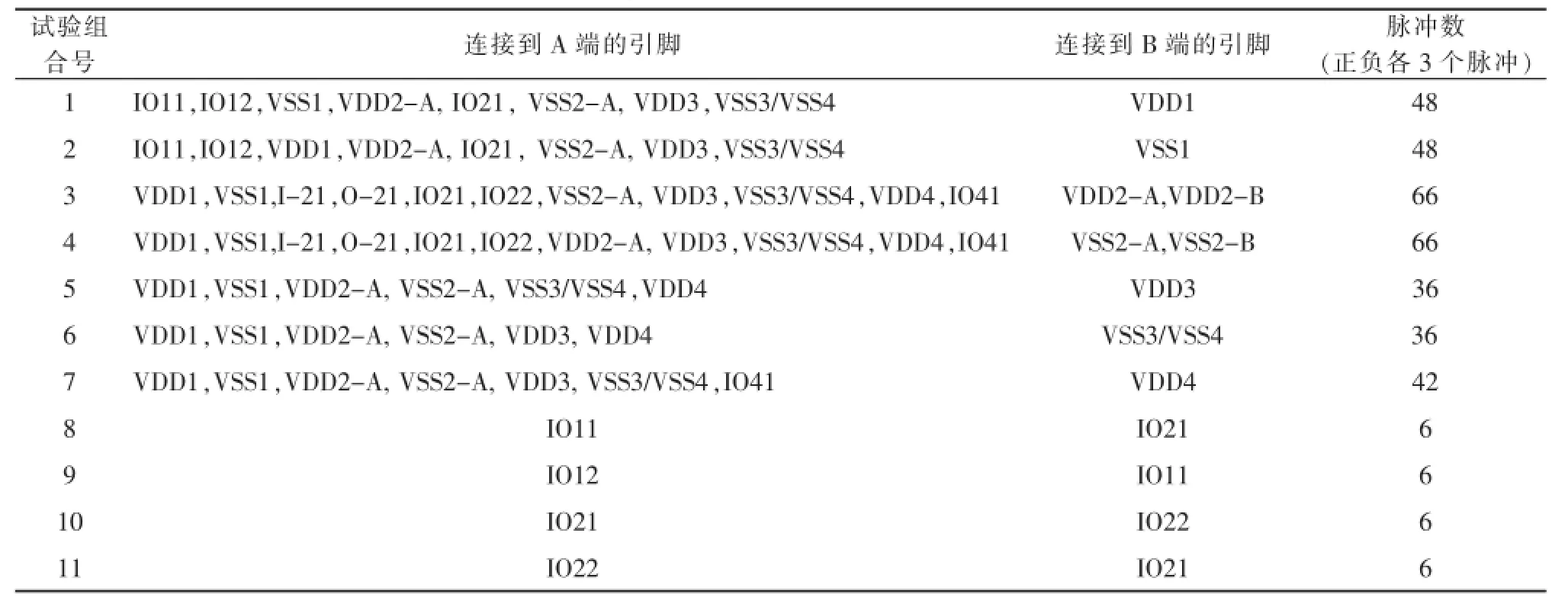

我们以 JS-001-2012 的静电放电标准对上述多电源域电路进行打击,可以得到以下打击方案,见表3。

该标准中规定样品数量为18个,每3个电路作为1组,总计6组,第一分组进行所有电源之间的正脉冲打击,第二分组进行所有电源之间的负脉冲打击,第三分组打击方式为某一电源域内的IO端口仅对该电源域的电源进行正打击,第四分组打击方式为某一电源域内的 IO端口仅对该电源域的电源进行负打击,第五分组打击方式为某一电源域内的差分信号端口之间进行正脉冲打击,第六分组打击方式为某一电源域内的差分信号端口之间进行负脉冲打击。

2.3 两个标准之间的区别

以上述电路为例,GJB 方法和JEDEC方法关于ESD 打击的区别如下:

·GJB中规定样品数量为3只,每次打击3个正脉冲,3个负脉冲,脉冲之间延迟至少1s;而 JEDEC中规定样品数量为18只,每次打击至少1个正脉冲,1个负脉冲,脉冲之间延迟至少0.1s。

·GJB中规定IO端口需要对电路的所有电源(地)进行打击,而JEDEC中IO端口只对自己区域内的电源(地)进行打击。

·GJB中,对于内部短路的电源组在作为A端时,每个电源引脚都必须打击,而在JEDEC中,内部短路的电源组在作为A端时,只需对其中某一个引脚进行打击,而其他引脚不需要进行打击。

表3 样品电路JEDEC标准打击方案

3 两个方法在实际应用中的互补

某公司的 XX95T 项目,在鉴定考核前需要对该电路进行 ESD 摸底,项目要求该电路电压等级 1000V,由于电路引脚有 1152 个,为了确定电路 ESD 等级是否达标,如果不达标可能失效的引脚是哪里,所以选择了JEDEC中的方法进行打击。

在实际打击过程中,IO端口IO_L2N_6(AJ22)对该区域内电源VCCO_6进行正脉冲打击时,发现该IO端口曲线发生变化,后续对该电路进行电参数测试,发现端口电流超标。

根据该电路的结果,设计部门对该端口的ESD保护结构进行改善,重新流片封装,对该打击模式进行试验,结果显示PASS。

后续该项目在鉴定过程时,考虑成品问题,选择了GJB方式进行考核,选取3只样品进行试验,结果合格。

4 总结

随着工艺的发展,集成电路的密度越来越高,实现的功能也越来越强大,多电源域是目前乃至将来集成电路发展的趋势,ESD 等级作为电路的一项重要指标,如何合理运用不同的打击方案来有效地寻找电路ESD 相对薄弱的地方变得尤为重要。

该论文分析了GJB和JEDEC两种打击方案,JEDEC 方案更偏向于分析验证,该标准利用不同电路打击不同方案,能够为后续失效分析提供有效证据;而GJB更偏向于考核鉴定,由于电路自身的价值,而且ESD属于破坏性试验,所以在考核时,GJB的方案更加适合。

[1]GJB54B8-2005.电子器件试验方法和程序[S].

[2]JS-001-2012 Human Body Model(HBM)-Component Level [S].

Research of Electro-Static Discharge Test for Multip le Power Domains Circuits

JIANGRudong1,CAIYilin2,LiXiaoliang1

(1.China Electronics Technology Group Corporation No.58 Research Institute,Wuxi214035,China;2.China Electronics Standardization Institute,Beijing 100007,China)

Along w ith the developmentof technology of integrated circuits,circuithas evolved from single power domain tomultiple ones.Electro-Static discharge(ESD)hasbecomean important index assessing the IC performance.Effective choice of testmethods has been increasingly important.The article explores the choiceof testmethods formulti-domain ICsby comparing domestic and international ESD standards.

ESD;testmethod;multiplepower domains

TN406

A

1681-1070 (2017) 03-0026-03

姜汝栋(1989—),男,江苏常州人,2011 年毕业于南京农业大学,主要从事集成电路可靠性分析工作;

2016-7-27

蔡依林(1979—),男,四川射洪人,2002 年毕业于成都电子科技大学,主要从事电子元器件可靠性检测工作;

李小亮(1990—),男,江苏泰州人,2013 年毕业于江南大学,主要从事集成电路可靠性分析与设计工作。