宽带数字波形产生中的广义多相滤波>

2016-01-10

(中国电子科技集团公司第三十八研究所,安徽合肥230088)

0 引言

近年来,随着雷达、通信与电子对抗技术的不断更新,要求数字波形产生系统的带宽不断增加,这同时给数模变换器件(DAC)和数字信号处理器件带来了巨大挑战。随着DAC技术的高速发展,数字信号处理器件对数字波形产生系统的带宽的制约尤为明显。多相滤波理论的提出有效缓解了数字信号处理器件对宽带数字波形产生的制约,其滤波器位于内插器之前,即滤波是在提速之前进行的,大大降低了对信号处理器件运算速度的要求,提高了系统的实时处理能力[1-2]。多相滤波的本质是在进行数字滤波的同时实现了内插。

传统多相滤波算法将滤波处理的速度降为输出信号速度的1/I(I为多相合成的阶数),并实现了I倍内插,即多相合成的阶数与内插比是一致的[3]。在工程实践中这只是一种特殊情形,一个经常遇到的情形是多相合成的阶数与所需的内插比并不一致。笔者在研究传统多相滤波算法的基础上,试图通过一种“广义多相滤波”的概念,为这两种情形找到一种统一的表述方式,使得多相滤波在实现K倍降速(K为多相合成的阶数)的同时进行I倍内插(I为内插比,K=I或者K≠I)。

1 广义多相滤波

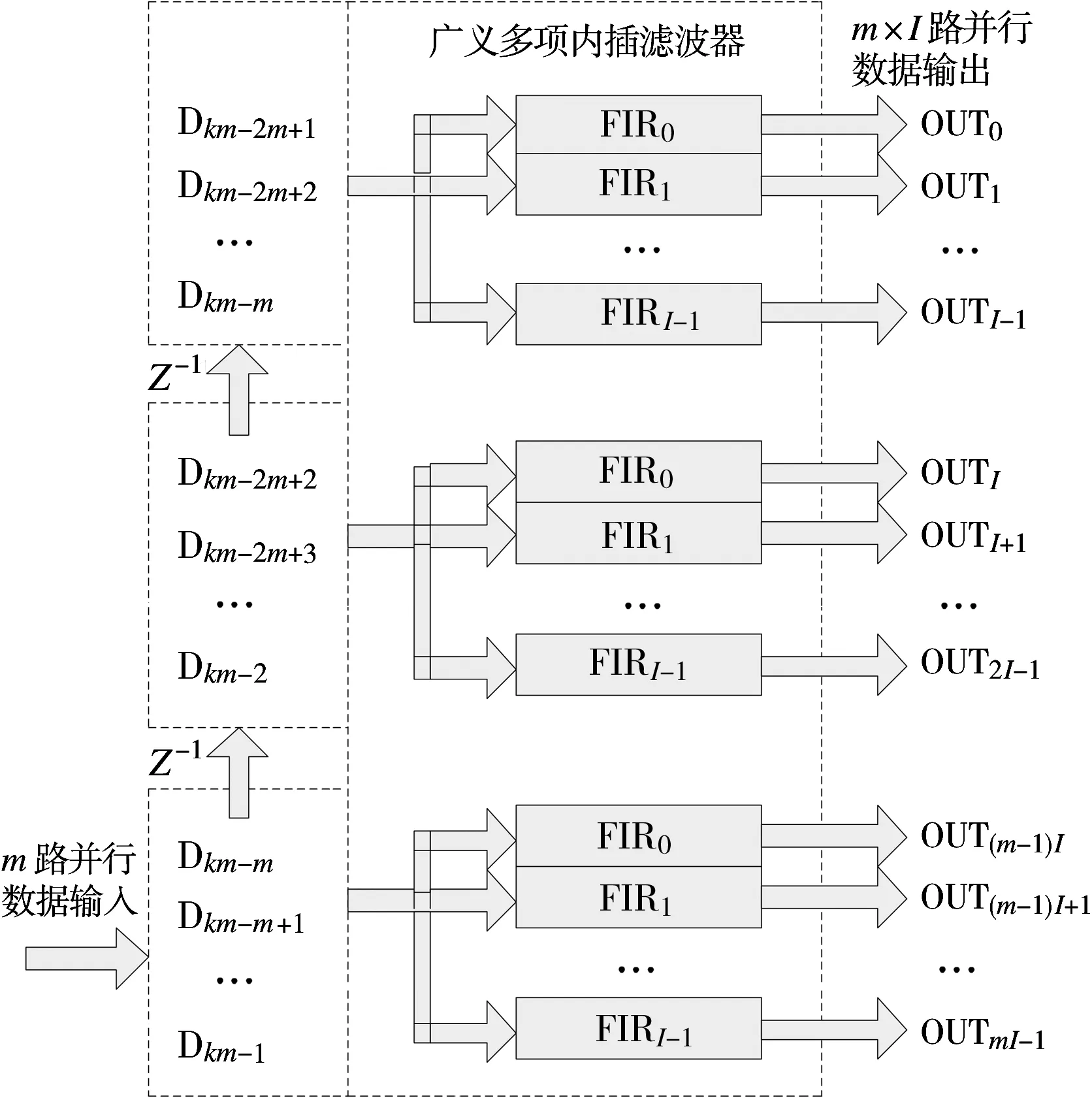

不同于抽取系统所要求的对输入数据进行多相分解[4],内插系统在使用多相滤波时,需要对原型滤波器系数进行多相分解后完成分支滤波,输出多路并行数据,再进行多项合成[5],从而实现所需处理速度的上升,如图1所示,虚线框内即为多相合成的过程。在宽带数字波形产生的工程应用中,信号处理器件输出的并行数据在进入DAC之前往往需要进行并串转换,这一并串转换过程正好实现了多相滤波所需的多相合成操作[6]。

多相合成的阶数主要由两个因素决定,一是数字信号处理器件的处理速度,二是实现多相合成的硬件结构。如某宽带波形产生系统,需要通过数字上变频和数模转换产生中心频率500MHz、带宽400MHz的中频信号,使用现场可编程门阵列(FPGA)作为数字信号处理器件,在FPGA中对要送给DAC的高速数字信号进行并串转换。为了减少芯片输出引脚数,DAC输入的高速数据采用1∶2数据复用器(DEMUX)和DDR格式,而集成在该FPGA中的并串转换器的转换比只能是固定的4,6,8,10和14。故多项合成的阶数为8,12,16,20,28这5种,这就是多相合成的阶数受实际硬件结构影响的典型情形。

对于一个多速率信号处理系统,其内插比主要由转换速率和信号带宽决定,比如在上述数字波形产生系统,当转换速率为2 000MHz时,内插比不能超过4,否则便不能满足系统带宽对输入信号速率的需求。

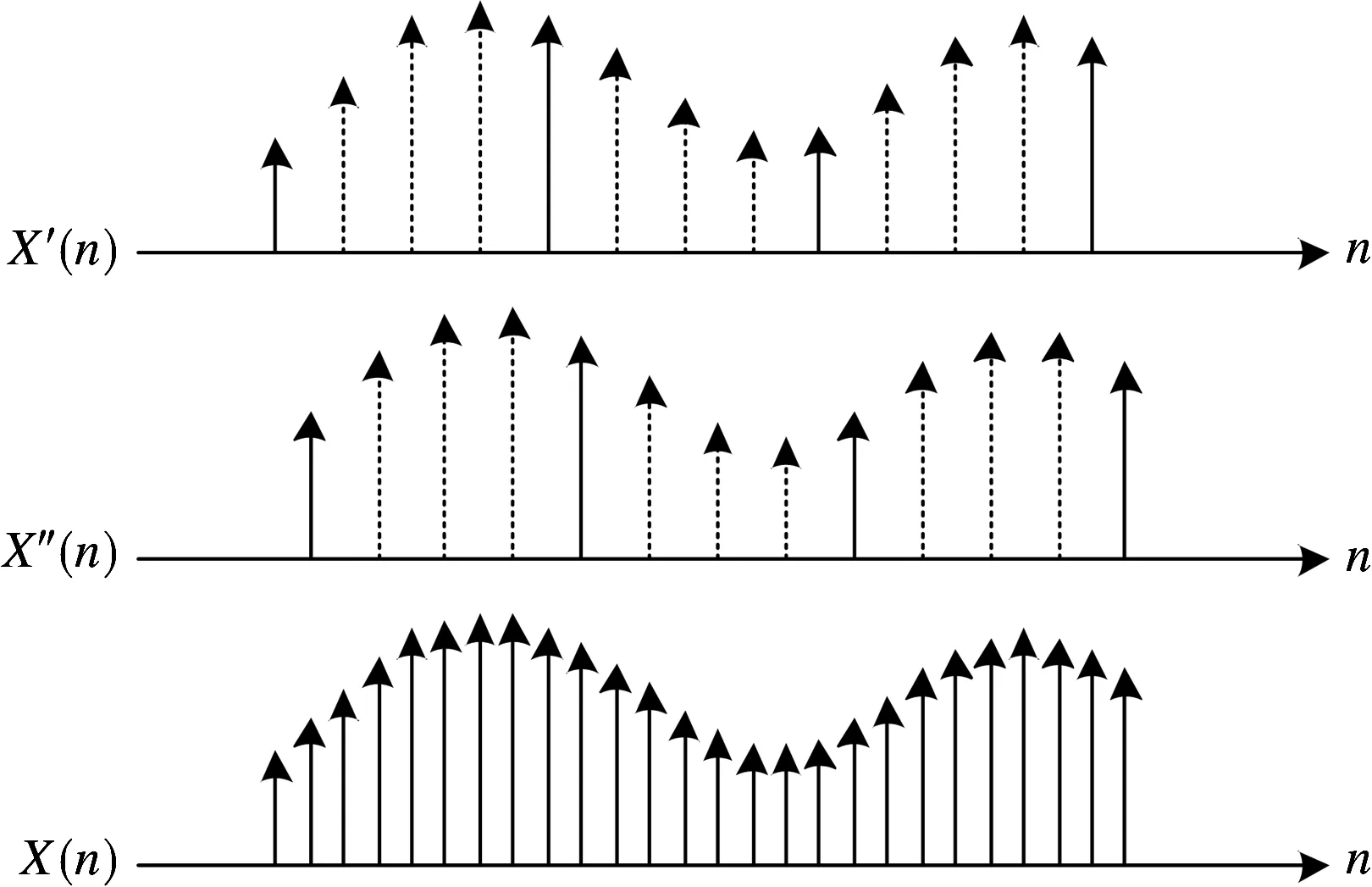

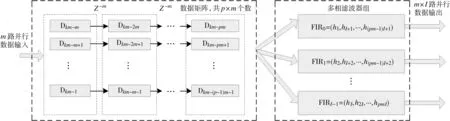

针对这里遇到的多相合成的阶数K与内插比I不一致的情形,为了实现对I倍内插数据的K阶多相合成(I≤K,m=K/I为正整数),可以在传统多相滤波的基础上进行m-1倍“补相”操作,使其输出为并行的K路数据。如图2所示,图中X′(n)为输入数据,X″(n)为补相数据,X′(n)和X″(n)分别完成I倍内插滤波,生成时间交织(time-interleaved)信号,m路时间交织信号合成后输出K路并行数据(K≥I)。

图2 “补相”示意图

相比于通常频域上的滤波抽取分析,在时域上考察内插滤波过程则更为简洁与直观,如图3所示。

图3 内插滤波过程

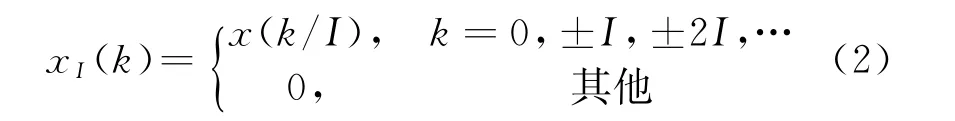

设图中FIR滤波器的单位脉冲响应为h(n),设定滤波器的阶数为p×m×I-1,p为正整数,m为并行输入路数,I为内插倍数,则

由内插原理可知,

联立式(1)与式(2),可得传统多项滤波器的I个输出分支:

针对图3中的m×I个输出分支,将式(3)进一步展开,可得

由此得到内插滤波器的广义多项滤波架构,如图4所示。

图4中共有m×I路(即为K项)输出,每连续I路数据组成一个广义多项滤波器分支,故有m路滤波器分支。每个分支滤波器的实现架构如图5所示,基于传统的多项滤波器架构,只是将数据输入改为由寄存器组构成的数据矩阵。最后一路分支为输入数据产生的多项滤波结果,其余m-1路分支即为补相数据产生的多项滤波结果。输入支路与各补相支路拥有相同的多项滤波器组,但滤波器输入数据依次存在单位时延。

图4 内插滤波的广义多项滤波架构

图5 广义多相滤波器分支

由此可得到广义多相滤波的具体步骤如下:

1)将m路并行输入数据进行m-1级单位延时,形成m组m路并行数据,作为分支滤波器的输入;

2)选定内插低通原型滤波器的阶数位p×m×I-1,以I为间隔对滤波器系数进行抽取重排,形成I组多项滤波器组,每组系数为p×m个;

3)对每个分支滤波器的m路并行数据寄存p-1级,形成m行×p列的数据矩阵,共p×m个有效数据;

4)对于每个分支滤波器,用3)中数据和2)中滤波器系数作卷积运算,形成I路分支滤波输出;

5)基于m组分支滤波器,重复完成4)中运算,最后形成m×I路并行数据输出。

2 基于广义多相滤波的L波段数字波形产生

2.1 数字波形产生架构

以上文所述宽带数字波形产生为例,通过光纤接收基带数字信号,再经过广义多项滤波和正交混频生成中频为500MHz、带宽为400MHz的数字信号。选用具有混频模式(Mix-Mode)的DAC芯片,DAC转换速率为2 GS/s时,可直接生成中频为1 500MHz、带宽为400MHz的L波段中频模拟信号,如图6所示。

图6 基于广义多相滤波的数字波形产生架构

DAC采用某公司XXX9739芯片,最高转换速率为2.5 GS/s,基带或混频模式可供选择。该芯片输入为两路高速并行LVDS信号(内置1∶2数据复用器),以DDR模式传输。为了满足高速源同步系统的应用需求,所用FPGA中集成了具有专用时钟和逻辑性能的并串转换器,当输出数据采用DDR模式时,该并串转换器的转换比可以为4,6,8,10,14。考虑到后续处理资源的使用,选用的转换比为4,此时并串转换器的输入为八路250 MS/s并行数字信号,输出为两路1 GS/s的并行数字信号。

由于转换速率和信号中心频率之间正好满足最佳采样率的要求,在进行数字混频时可以避免乘法器的使用,直接与“1,0,-1,0”和“0,-1,0,1”相乘即完成数字混频和正交变换。不难根据前述的并串转换比推导出每一路250MHz信号的转换规律,比如第一路应依次乘以“1,-1,1,-1,…”第二路为全0,以此类推。全0的无效数据使得广义多项滤波器的一半滤波支路可被省去,大大节省了硬件资源。

在该数字波形产生中,信号带宽达400MHz,为了保证一定的过采样,基带数据率选为500 MS/s。由于数字信号处理硬件的限制,无法直接工作在500MHz这样高的运算速度上,只能采用并行降速的方法,将数据率降为两路250 MS/s。传统的多相滤波方法已无法直接使用,需要采用广义多相滤波架构,进行m=2倍补相,内插因子I=4,多相合成因子m×I=8。广义多相滤波共输出八路250 MS/s信号,等效数据率为2 GS/s,与DAC接口速率相匹配。同时,广义多相滤波还为实际应用提供了更多的选择。比如,当带宽更宽时,可以令m=8,I=1,即不对数据进行内插操作,但是同样可以通过多相滤波降低处理速率,而当带宽更窄时,可以令m=1,I=8,此时成了传统的多相滤波,它是广义多相滤波的一个特例。由此可见,设计者可以在广义多相滤波概念的框架内灵活进行速度与面积的互换。

2.2 仿真验证

为了对所述广义多相滤波及数字波形产生进行验证,使用 Matlab软件产生测试数据,使用Verilog语言实现上述功能模块,在目标芯片中进行布局布线,将产生的网表文件和测试数据一起导入Modelsim软件进行仿真,并使用Matlab读出仿真结果。

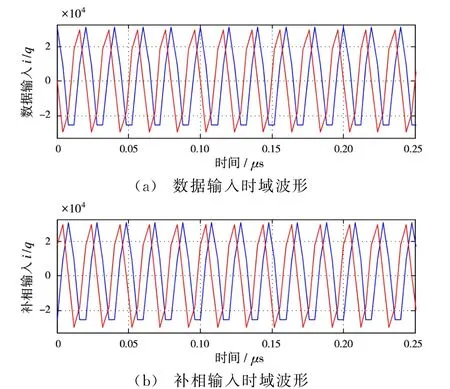

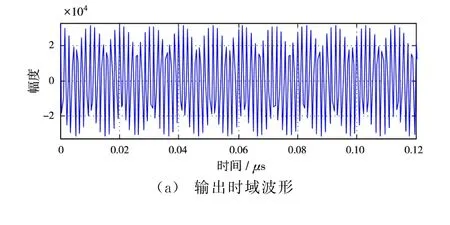

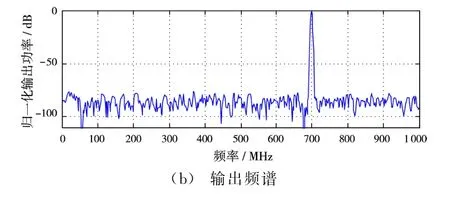

假定输入基带信号速率500 MS/s,带宽400MHz,输出数字中频为500MHz,按上述架构实现数字波形产生系统,其中广义多相滤波的阶数为p×m×I-1=8×4×2-1=63阶,输出时域信号如图7所示,图7(a)为输入数据的同相/正交分量,图7(b)为补相数据的同相/正交分量。图8为经过广义多相滤波和上变频后的时域波形和频谱。

图7 广义多相滤波输入信号时域波形

图8 广义多相滤波输出信号时域波形和频谱

2.3 硬件资源评估

上述广义多相滤波(64阶FIR滤波)的综合结果在某FPGA芯片上进行布局布线,所需的资源如下:

Number of Slice Registers:3 968

Number of Slice LUTs:3 445

Number of DSP48E1s:128(即128个18×25乘法器)

这里重点关注的是乘法器资源的使用,64阶FIR滤波器在进行m=2广义多相滤波时,需要128个18×25乘法器。对于进行m=1的广义多相滤波,即传统多相滤波时,所需的乘法器资源为64个18×25乘法器。这说明广义多相滤波对乘法器资源的需求正比于补相数m(m=K/I,即多相合成的阶数和内插比之间的比例)。设计者可以灵活调节m值,按实际需求在速度与面积之间进行权衡。

3 结束语

本文所述广义多相滤波解决了工程中常见的多相合成的阶数与所需内插比不一致的问题,传统多相滤波器可以看作广义多相滤波在m=1时的一个特例。本文在广义多相滤波的基础上构建了一个宽带数字波形产生系统,仿真验证表明,该算法能够满足宽带数字波形产生的使用要求,为工程实践中的速度与面积互换原则提供了一种新的理解方式。广义多相滤波通用性强,可用来构建宽带数字波形产生系统中的各种内插滤波器。

[1]HARRIS F J.通信系统中的多采样率信号处理[M].王霞,张国梅,刘树棠,译.西安:西安交通大学出版社,2008:126-128.

[2]梁广,龚文斌,刘会杰,等.星载多波束发射阵列天线多通道数字上变频设计[J].宇航学报,2009,30(6):2270-2276.LIANG Guang,GONG Wenbin,LIU Huijie,et al.The Design and Implementation of Multi-Channels Digital-up-Converters of Multi-Beam Phased Array Antenna on Satellite[J].Journal of Astronautics,2009,30(6):2270-2276.(in Chinese)

[3]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2005:28-31.

[4]张飞,伍小保.广义多相滤波及其应用[J].雷达科学与技术,2014,12(3):262-266.ZHANG Fei,WU Xiaobao.Generalized Polyphase Filtering(GPF)and Its Application[J].Radar Science and Technology,2014,12(3):262-266.(in Chinese)

[5]吕影影,徐强,崔志超.一种基于多相滤波的高速信号处理算法[J].雷达科学与技术,2014,12(2):161-165.LYU Yingying,XU Qiang,CUI Zhichao.Algorithms of High-Speed Signal Processing Based on Poly-Phase Filter[J].Radar Science and Technology,2014,12(2):161-165.(in Chinese).

[6]王锰,吕卫祥.基于高速D/A AD9739的宽带信号产生[J].雷达与对抗,2011,31(4):55-58.WANG Meng,LYU Weixiang.The High-Speed D/A AD9739-Based Wideband Signal Generation[J].Radar&ECM,2011,31(4):55-58.(in Chinese)