基于PC机和运动控制卡的运动控制系统设计

2015-02-16张清勇张丹红

张清勇,张丹红,姜 文

(武汉理工大学 自动化学院,湖北 武汉 430070)

基于PC机和运动控制卡的运动控制系统设计

张清勇,张丹红,姜 文

(武汉理工大学 自动化学院,湖北 武汉 430070)

介绍了由PC机和运动控制卡构成的运动控制系统,设计了由FPGA和PCI专用接口芯片组成的运动控制卡PCI接口控制器,实现了上位机与运动控制卡之间灵活而高速地通信,理论最大通信速率最高可达140 MB/s。

运动控制卡;PCI总线;接口控制器;FPGA

运动控制卡是一种可用于各种运动控制场合的上位控制单元。工业运动控制系统中,大多数运动控制卡通过PCI总线与上位机通信,PCI总线接口控制器的性能直接决定了运动控制卡与上位机的通信性能。PCI总线规范十分复杂,采用CPLD或FPGA等可编程逻辑器件直接实现接口控制器在技术和经济上要求比较高[1],为了达到PCI规范的严格要求,需要作大量的逻辑验证、时序分析和程序调试,而采用专用PCI接口芯片和可编程逻辑器件相结合的设计方法可使设计开发者免除繁琐的时序分析,增加接口设计的灵活性。

笔者设计的PCI接口控制器由专用PCI接口芯片和FPGA组成。PCI9054是美国PLX公司生产的一款32bit/33MHz的通用PCI总线控制芯片[2-5],突发传输速率可达到132 MB/s,能够完成PCI总线信号与Local总线信号的相互转换。

FPGA(field-programmable gate array),即现场可编程门阵列是在CPLD基础上发展起来的新型高性能可编程逻辑器件[6],可完成极其复杂的时序与组合逻辑电路功能。该设计选用Altera公司Cyclone II系列的EP2C5T144完成PCI9054 Local总线与PCL6143 8086总线的对接。运动控制卡的大部分运动控制功能是由PCL6143实现的,EP2C5T144除了实现PCI9054与PCL6143总线接口的对接外,还可实现与PCI9054直接通信,以拓展运动控制卡的运动控制功能。

1 运动控制系统总体结构

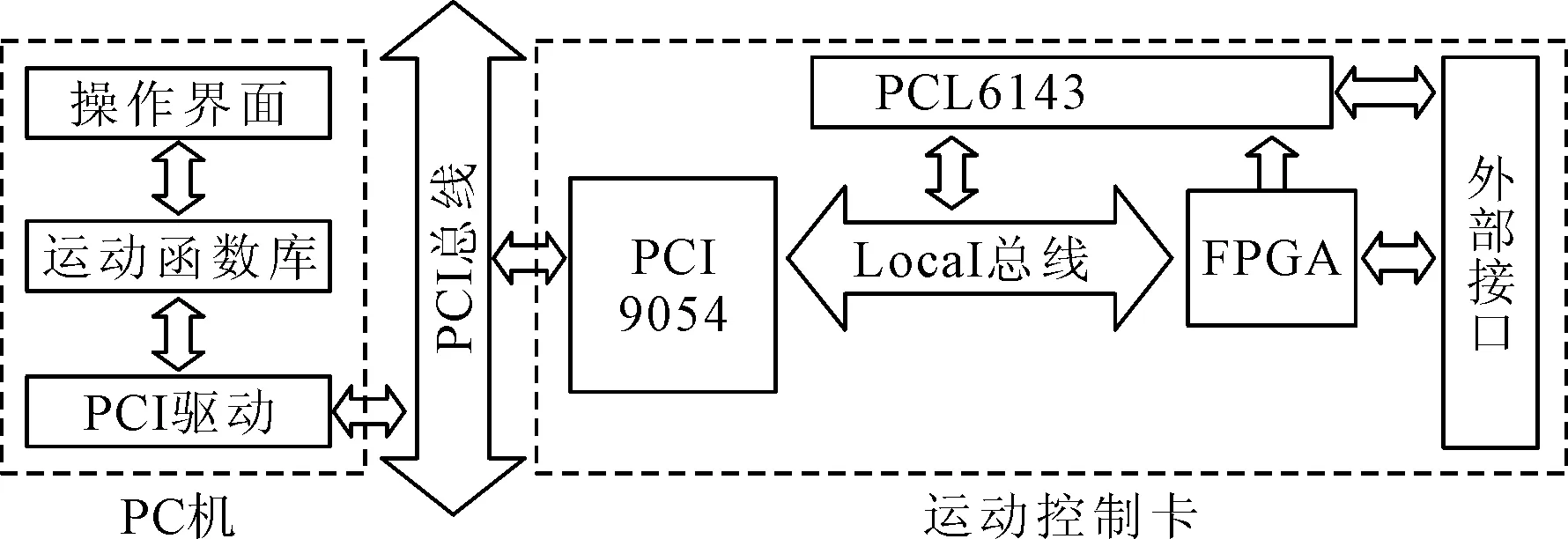

笔者的运动函数是通过PCI驱动程序驱动PCI总线传输数据至运动控制卡。运动控制卡实现各种速度和位置控制,并提供通用和专用I/O口与外界连接,系统结构如图1所示。系统中,上位机作为控制系统的核心部分[7-8],用户通过操作界面直接调用运动函数库的运动函数,PCI插槽直接插入PC机中,板卡提供外部接口与伺服驱动器、限位开关和指示灯等相连接。

图1 运动控制系统总体结构图

所设计的运动控制卡主要分为通信部分和运动控制部分,通信部分采用PCI9054作为桥接芯片与上位机进行通信,完成PCI总线信号到Local总线信号的转换。FPGA用于实现PCI9054 Local总线与PCL6143 8086总线的逻辑粘合,保证PCI9054接收的上位机数据通过Local总线传送至PCL6143,FPGA还可直接与PCI9054进行通信。运动控制部分的大部分功能由PCL6143实现,FPGA用来拓展PCL6143的功能。

2 PCI9054的Local总线

PCI9054提供了PCI总线、EEPROM和Local总线3个接口,PCI总线接口与PC机的PCI总线相接,以完成PC机PCI总线到Local总线的桥接,并在两者之间传递数据和信息。Local总线负责与外部设备的总线相接,外部设备通过简单的时序设计便可与PCI9054 Local端通信。

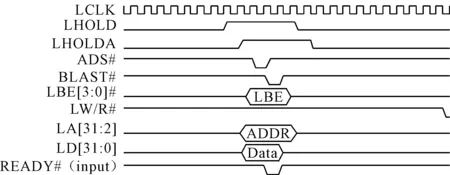

PCI9054具有3种工作模式:M模式、J模式和C模式。Local总线与PCI总线之间的数据传输有3种方式:PCI Initiator、PCI Target和DMA。该设计根据需求选择了PCI9054数据传输方式为PCI Target,工作方式为C模式(数据、地址总线非复用),16位总线读写。在该工作模式中,字节使能信号LBE1#可等效为地址信号次低位LA1。由于PCI9054完成了PCI总线所需的全部时序,因此设计重点集中在Local总线,Local总线单周期写时序图如图2所示。

图2 Local总线单周期写时序图

Local总线的读、写时序基本相同,以PCI Target单周期写为例,首先PCI9054通过驱动LHOLD有效来申请Local总线的主控权,如果Local总线空闲,FPGA驱动LHOLDA有效以使PCI9054成为Local总线的主控。随后PCI9054驱动ADS#有效,使得地址总线信号LA[ 31: 2]、字节使能信号LBE[ 3: 0]#和读写使能信号LW/R# 进入有效状态,FPGA需对以上信号锁存和译码来确定操作目标和操作类型。目标设备通过驱动READY#信号有效,来通知PCI9054目标设备已经准备好,这时PCI9054将数据传输到数据总线LD上,目标设备需在下一个时钟上升沿读取数据。而后PCI9054驱动BLAST#有效来表示单周期写操作的结束。最后,PCI9054将使能LHOLD信号来释放Local总线,FPGA也需使能LHOLDA信号。

3 PCL6143的8086总线

PCL6143是美国NPM公司设计的一款高性能、低成本的专用运动控制器[9],用户通过简单的内部控制指令就可实现复杂的运动功能。PCL6143能够进行定速、直线加减速、S曲线加减速的速度控制,也可进行连续运动、定长运动、回原点运动等位置控制。1片PCL6143控制4个轴,用户可以控制1个芯片或者多个芯片进行多轴直线插补,同时可对PCL各种运动状态进行监视。此外,芯片可产生各种条件下的中断信号,还具有用于控制伺服马达驱动器的功能。

PCL6143 内部集成有各种不同接口电路, 允许与 4 种类型的 CPU 连接, 分别是 Z80、8086、H8 和 68000。考虑到通用性,该设计选择应用广泛的Intel接口(8086接口)实现16位数据传输。因运动控制功能已集成在芯片内部,故设计重点为PCL6143的8086总线接口,接口单周期写时序图如图3所示。

图3 8086总线单周期写时序图

针对时序图3的时序条件的具体说明如表1所示。8086总线单周期读时序分析基本与写时序一致,以写时序为例,由图3和表1可知,FPGA首先要驱动地址总线A1~A4和片选信号CS#有效,且要满足A1~A4和CS#的建立时间,在A1~A4保持有效至少10 ns和CS#保持有效至少4 ns后才能驱动WR#有效。在CS#有效后若WRQ#有效,则PCL6143处于忙碌状态,请求CPU等待。待WRQ#无效后,CPU便将有效数据送至数据总线,等待至少12 ns后FPGA再置WR#为高电平,在WR#上升沿期间,数据被写入至PCL6143。

表1 8086总线单周期写时序表 ns

4 接口控制器的实现

PCI总线接口控制器中PCI9054实现其与PC机PCI总线的通信,FPGA实现PCI9054 Local端与PCL6143的通信,以及与PCI9054 Local端的直接通信。通过对Local总线和8086总线的时序分析可知,Local总线属于同步总线接口,而8086总线属于异步总线接口,两者的接口时序完全不符。由于组合逻辑电路的产生延时并不固定,且容易产生毛刺和亚稳态,通过简单组合逻辑电路将两者进行逻辑粘合的方案可行性不高,笔者采用的Local端接口电路方案如图4所示。

图4 Local端接口控制器电路图

图4中,FPGA分别驱动Local总线和8086总线。FPGA驱动模块左侧接口与Local总线属于同步通信,为减小时钟偏斜和时钟抖动,使用FPGA的锁相环和全局时钟网络,且锁相环的输出经过全局时钟网络和输出引脚直接驱动Local端时钟。由于Local端只有一个从机,不存在总线仲裁问题,因此PCI9054 LHOLD信号线随时申请主控权便可随时获得LHOLDA信号的应答。若将LHOLD和LHOLDA直接相连,很容易造成计算机运行的不稳定,这是因为当环境温度、工作电压等外界因素变化时,大多数逻辑器件的引脚延时会有相应的变化。利用D触发器只在触发时钟有效边沿对信号敏感的特性进行设计,可提高电路运行的稳定性,因此该设计将LHOLD在FPGA中经D触发器后输出为LHOLDA。

FPGA驱动模块右侧接口与8086总线属于异步通信,驱动模块需提供4根地址线供PCL6143片内寻址。由于FPGA需要与PCI9054直接通信以实现运动控制功能,因此自身也需4根地址线供其片内寻址。Local端的PCI_LA[4..2]和PCI_LBE1#用于片内寻址,PCI_LA5用于片外寻址,以区分FPGA和PCL6143。

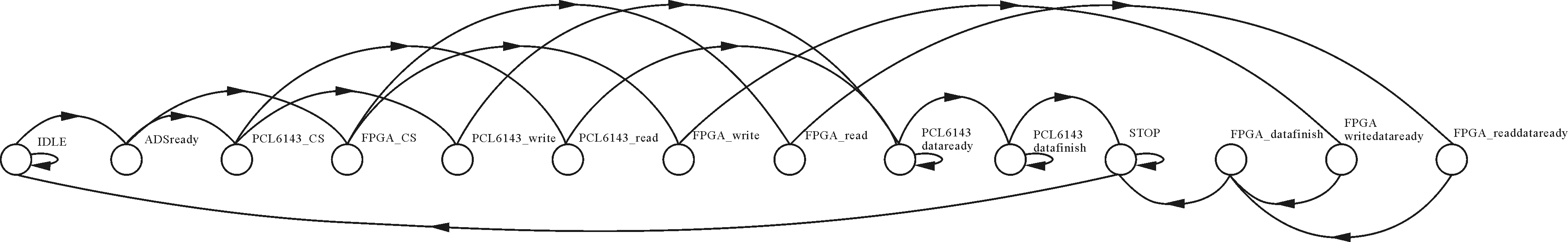

Local端接口控制器的主体部分是由有限状态机实现的,所设计的状态机采用高效的one-hot编码,运用三段式描述方法,使FSM做到同步寄存器输出,消除了组合逻辑输出的不稳定与产生毛刺的隐患,且更利于时序路径分析,在FPGA上的综合与布局布线效果更佳。状态机的状体转移图如图5所示。

图5 接口控制器状态机的状态转移图

一个完备的状态机应该具备初始化状态和默认状态,所设计的状体机初始化状态和默认状态都为IDLE。该状态机的转移是由驱动模块的输入信号PCI_ADS#、PCI_BLAST#、PCI_LW/R#和PCI_LA5的变化引起的。在初始状态IDLE下,若Local端PCI_ADS#有效,则进入状态ADSready,在该状态中锁存PCI_LA[5:2]和PCI_LBE1#,根据最高位地址线PCI_LA5判断此次读写操作是PCL6143还是FPGA,若PCI_LA5为低电平则进入状态PCL6143_CS,否则进入状态FPGA_CS。

针对PCL6143的读写操作,在状态PCL6143_CS中,驱动PCL6143片选信号PCL_CS#和地址信号FPGA_LA[4..1]有效,并判断PCI_LW/R#,若为高电平则进入状态PCL6143_write,否则进入状态PCL6143_read。在状态PCL6143_write或PCL6143_read中,驱动PCL6143写信号PCL_WR#或读信号PCL_RD#有效,并进入状态PCL6143_dataready。在状态PCL6143_dataready中判断PCL_WRQ#,若有效则停留在原状态,否则驱动PCI_READY#有效,即PCL6143已经准备好读写数据,并进入状态PCL6143_datafinish。在状态PCL6143_datafinish中,驱动PCL_WR#和PCL_RD#无效,并判断PCI_BLAST#,若无效则停留在原状态,即该次读写操作还未结束,否则驱动PCI_READY#和PCL6143_CS#无效并进入状态STOP。在状态STOP中,判断PCI_LHOLD,若有效则停留在原状态,即PCI9054还未释放Local总线,否则进入状态IDLE。

针对FPGA的读写操作,在状态FPGA_CS中,判断PCI_LW/R#,若为高电平则进入状态FPGA_write,否则读取在状态PCI_ADS#锁存的PCI_LA[ 4..2] 和PCI_LBE1#地址值并获取该地址中的数据,进入状态FPGA_read。在状态FPGA_read中,将要读的数据送至数据总线PCI_LD[15:0]上,保证PCI9054在读取Local端数据时已将数据准备好,并进入状态FPGA_readdataready。在状态FPGA_readdataready中,驱动PCI_READY#有效,即通知PCI9054数据已经准备好,可以开始读取数据,并进入状态FPGA_datafinish。若此时处在状态FPGA_write中,驱动PCI_READY#有效,即通知PCI9054已经准备好接收数据,并进入状态FPGA_writedataready。状态FPGA_writedataready中,获取数据总线PCI_LD[15:0]的数据,并进入状态FPGA_datafinish。在状态FPGA_datafinish中,驱动状态PCI_READY#无效,即通知PCI9054接收数据已经完成,并进入状态STOP。在状态STOP中,判断PCI_LHOLD,若有效则停留在原状态,否则进入状态IDLE。

为了保证设计稳定可靠,必须对设计附加时序约束,对综合结果进行时序分析。该设计采用TimeQuest Timing Analyzer时序分析工具对全局时钟、全局I/O、输入最大/最小延时和输出最大/最小延时进行约束,经布局布线优化后,时序分析报告结果显示系统可以运行的最高时钟频率fmax=69.99 MHz (period=14.288 ns ),时序余量slack=5.712 ns,完全满足设计要求。

5 结论

笔者提出了一种基于PC机和运动控制卡的运动控制系统设计方案,选用专用接口芯片PCI9054避免了复杂的逻辑设计和时序分析,采用高性能FPGA实现了PCI9054与PCL6143的通信并可拓展PCL6143部分运动控制功能。同时重点讨论了PCI总线接口控制器的实现,分析了PCI9054 Local总线时序和PCL6143 8086总线时序,使用三段式状态机实现了Local总线与8086总线的通信,以及FPGA与PCI9054的直接通信。静态时序分析结果和现场通信测试表明,该设计稳定可靠,通信高效流畅。

[1] 刘军智,王亚海.基于PCI9054与FPGA结合的PXI 总线接口电路的设计[J].电子质量,2010(7):9-11.

[2] 童鹏,吴新建.PCI9054芯片接口设计中若干问题的深入研究[J].电子技术应用,2005,31(10):64-66.

[3] 韩雪峰,黄炎,杨涛.基于PCI总线的高速数据采集接口的设计与实现[J].微计算机信息,2005,21(8):71-73.

[4] 谢黎明,陈宏涛.DSP运动控制器与PCI总线的接口设计[J].新技术新工艺,2010(5):36-37.

[5] 张丹红,张孝勇,刘文.基于PCI9054的数据通信接口卡设计[J].武汉理工大学学报(信息与管理工程版),2013,35(3):305-308.

[6] 王金明.Verilog HDL程序设计教程[M].北京:人民邮电出版社,2004:1-8.

[7] 李颖,谭立新,张文凯.基于PC和运动控制卡的开放式运动控制系统[J].仪表技术,2007(4):43-44.

[8] 何林,孟宪翠,董砚,等.基于DSP和CPLD的运动控制器简化设计与应用[J].自动化与仪表,2011(1):36-39.

[9] 罗继合,刘建群,余孝伟,等.PCL6143运动控制器的原理及应用[J].国外电子元器件,2008(1):48-51.

ZHANG Qingyong:Laboratory Technician; School of Automation, WUT, Wuhan 430070, China.

[编辑:王志全]

Design of Motion Control System Based on PC and Motion Control Card

ZHANGQingyong,ZHANGDanhong,JIANGWen

Firstly, motion control system structure based on PC and movement control card was introduced. Then the realization of interface controller between PCI bus and special motion control chip by use of interface chip PCI9054 and programmable logic device FPGA was mainly described. The interface controller also implements the direct communication between FPGA and PCI9054 to expand the function of PCL6143, which makes the motion control system more open-ended. The maximal theoretical communication rate is up to 140MB/s.

motion control card; PCI bus; interface controller; FPGA

2015-09-06.

张清勇(1984-),女,湖北仙桃人,武汉理工大学自动化学院实验师.

湖北省自然科学基金资助项目(2013CFB335).

2095-3852(2015)06-0837-04

A

TP23

10.3963/j.issn.2095-3852.2015.06.038