抗辐射SOI器件栅氧可靠性研究

2014-09-19吴建伟谢儒彬刘国柱

吴建伟,谢儒彬,顾 祥,刘国柱

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

绝缘体上硅(SOI,Silicon-on-Insulator)技术是在传统硅衬底表面下引入一层绝缘层,通常是SiO2。SOI技术作为一种全介质隔离技术,有着许多体硅技术不可比拟的优越性,相对于体硅工艺,SOI技术具有集成度高、速度快、抗干扰能力强的特点[1]。由于SOI CMOS电路实现了完全的介质隔离,PN结面积小,因此,SOI电路在抗单粒子事件、瞬时辐射等方面有着突出优势,远高于体硅CMOS电路[2,3]。但是,由于在SOI CMOS电路中埋氧层的存在,使得SOI CMOS电路在抗总剂量方面反而不如体硅有优势,辐射会在隐埋氧化层中产生电流,同时还会形成埋氧化层-硅界面陷阱,因此,SOI器件的抗总剂量辐射能力比体硅要差。为了提高SOI电路的抗总剂量辐射能力,采用抗总剂量加固技术[4],对SOI材料中的SiO2埋层进行加固,实验证明,经过加固后的SOI器件抗总剂量辐射能力可以达到1 M rad(Si)[5]。

电路的可靠性是研究与生产过程中一个重要的环节,随着器件尺寸的不断减小,相关可靠性方面的问题愈显突出,抗辐射可靠性仅是针对抗辐射电路的一个比较重要的因素,与此同时,栅氧质量也是集成电路研究中值得关注的问题[6,7]。目前的研究大部分针对体硅器件的栅氧可靠性,对于SOI器件的栅氧可靠性问题研究并不全面,特别是抗总剂量辐射埋氧加固工艺对器件栅氧可靠性的影响这一问题,研究的并不深入。因此,有必要针对抗总剂量辐射埋氧加固SOI器件的栅氧可靠性做详细的研究。

2 实验

介质按照击穿时的情况,通常可分为瞬时击穿与经时击穿[8]。瞬时击穿是指电压一加上去,电场强度达到或超过该介质材料所能承受的临界场强,介质中产生的大电流使得介质瞬间击穿,又称为本征击穿。在实际栅氧化层中,某些局部位置厚度较薄,从而导致局部场强增强,或者介质内存在空洞、裂缝等瑕疵,进而造成介质漏电甚至击穿。这些由缺陷引起的栅氧问题可在前期老化筛选过程中剔除;经时击穿是指施加的电场低于栅氧的本征击穿场强,不会引起介质的瞬时击穿,但是经过一定时间后则会发生击穿,这是由于电场应力的作用下,氧化层内产生并积累了大量缺陷,从而导致了栅氧击穿,这是考核栅氧质量的一个重要方面。

栅氧层经时击穿的过程可以大致分为两个阶段,第一阶段是在电场应力作用下,栅氧层内部及SiO2-Si界面处发生缺陷积累,积累的缺陷达到一定程度后,使局部区域的电场强度达到临界值,进而转入第二阶段;第二阶段是在热、电正反馈作用下,迅速使得栅氧层击穿。

对于电场应力作用下栅氧层及界面处产生的陷阱,一般都认为是由电荷引起的,但具体的模型尚无定论。虽然到目前为止己经有很多研究栅氧可靠性和退化机理的模型被提出,并且在一定的条件下得到了很好的实际验证,但是依然没能非常完美地解释各种器件特性退化的过程,目前最有影响的是空穴注入击穿模型[9,10]和电子陷阱产生击穿模型[11,12]。

2.1 样品制备

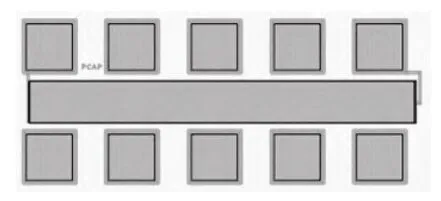

为了更好地研究栅氧层的质量,在PCM测试版图中设计了专门用于栅氧质量评估的结构,它是由P-well、栅氧、多晶硅所组成的栅氧电容结构,如图1所示,电容面积为75 μm×700 μm。

图1 栅氧测试结构图

本文所使用的材料片为SOI衬底材料片,材料片参数如下:P<100>10-20Ω,Top-Si(顶层硅)=235±10 nm,BOX(埋层二氧化硅)=375±10 nm。然后,运用离子注入技术对埋层二氧化硅进行加固注入。

制备栅氧测试结构的流程为(如图2):(1)一次氧化和一次氮化硅工艺(SiN),光刻有源区,腐蚀氮化硅后,定义形成场区;(2)场氧化形成FOX场氧区域,去掉氮化硅材料,进行离子注入形成P阱,形成电容测试结构下电极;(3)生长12.5 nm栅氧层,多晶硅淀积、多晶硅掺杂形成重掺杂多晶硅,通过多晶硅光刻、腐蚀形成多晶硅栅,作为电容测试结构的上电极,淀积LP SiO2350 nm,通过各向异性腐蚀形成侧墙;(4)通过离子注入工艺形成重掺杂区,用于电学连接,完成PMD(金属前介质淀积)和接触孔光刻、腐蚀,形成用于连接重掺杂区和金属布线的接触孔;(5)最后淀积金属,并进行金属光刻、腐蚀后,形成金属布线层,合金后完成多晶硅栅和P-well区域的连接,形成完整的栅氧电容测试结构,以下的测试结果将基于此结构进行测试分析。

2.2 实验与分析

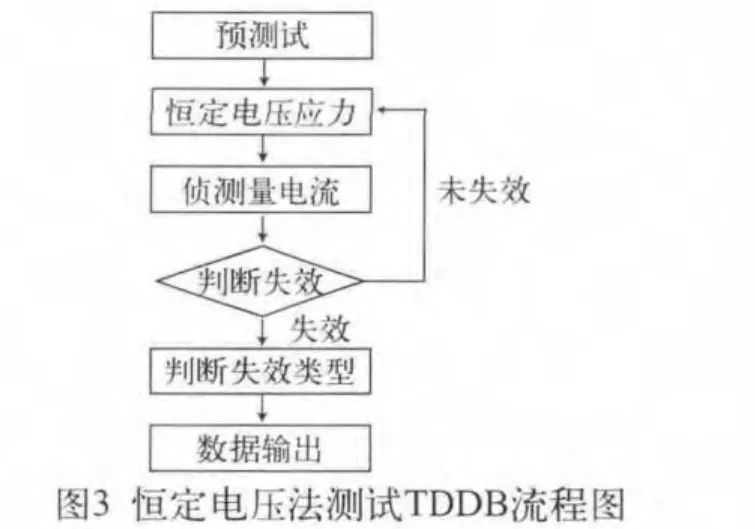

运用上述方法制备的栅氧测试结构,对其评估栅氧质量。测试的方法是在栅氧电容的上极板加应力,测量电学参量随时间的变化。应力条件的施加有多种方法,如:恒定电流应力(CCS)、恒定电压应力(CVS)、脉冲电压应力(PVS)、扫描应力,这里采用的是恒定电压应力法。用恒定电压法测试栅氧电容结构TDDB的流程如图3所示。

(1)在设定应力温度下,将一些初始化即失效的样品筛选出来;(2)保持应力温度,升到设定应力电压下,开始恒定电压测试;(3)持续侦测栅氧漏电流;(4)判断器件失效有否,如果暂没有失效则持续3、4步骤;(5)判断失效或达到预设上限时间则进入后测试阶段,目的是检查并判断失效模式;(6)数据输出,记录失效时间t,完成本次测试。

通过以上测试方法,对采用了抗总剂量辐射加固工艺的栅氧电容结构进行TDDB测试,记录失效时间。根据JEDEC/FSA Joint Publication No.001的要求,选用测试温度为125 ℃,评估栅氧电容在高温下的寿命。

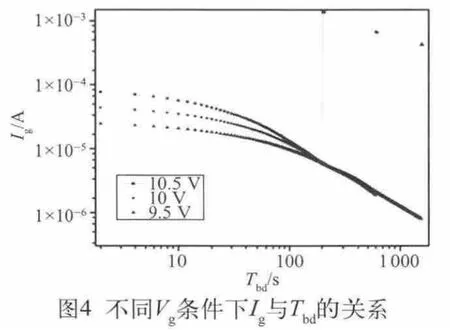

图4是对栅氧电容施加不同恒定电压时的测试结果。从图上可以看出,当样品施加恒定电压应力时,随着时间的增加,Ig缓慢下降。当达到某一临界值的时候,Ig突然上升,样品击穿。在测试过程中并没有观测到Ig出现饱和的现象,说明在持续应力下,栅氧中不断有陷阱产生。产生的新陷阱会不断俘获电荷,从而导致注入栅氧化层的电流随时间而改变。对于不同的栅电压Vg,随着Vg的增加,击穿时间Tbd减小。上述现象说明,栅氧的击穿包含了两个阶段,即形成积累阶段和突变阶段。

为了更好地研究抗总剂量辐射加固技术对栅氧质量的影响,同时对未使用加固工艺的SOI材料片与体硅片做了栅氧可靠性评估,测试方法如前所述,测试环境同样是维持在125 ℃,根据材料片的不同选取相应的应力条件。对测试所得的失效时间采用Weibull分布进行统计,取63.2%作为分布的中心值,做出累积失效概率图,如图5所示。

取63.2%的值作为评估栅氧寿命的击穿时间,将栅氧的击穿时间和电场应力强度做散点图,采用指数模型进行拟合,栅氧的击穿时间与电场应力强度之间呈指数线性关系,如图6所示。通过模型倒推栅氧在5.5 V工作,即电场应力在4.4 MV·cm-1的情况下的工作时间,最终得出,加固工艺样品栅氧寿命为14.65年,未加固SOI工艺样品栅氧寿命为20.62年,体硅样品栅氧寿命为355年,均大于10年的寿命时间。

从结果中可以发现,体硅样品的栅氧寿命远大于SOI样品的栅氧寿命,结合栅氧失效机理,可以认为这是由于在SOI材料片的制备过程中,顶层硅膜受到损伤,引入了更多缺陷造成了最终栅氧质量的下降。目前国内SOI材料片的制备主要有以下几种主流的技术:离子注入注氧隔离技术(SIMOX)、键合减薄技术(BESOI)、注氢智能剥离技术(Smart-Cut)和外延层转移技术(ELTRAN)。其中SIMOX主要采用的方法就是在普通圆片层间注入氧离子,经超过1 300 ℃高温退火后形成隔离层,注入过程中,会在圆片内形成氧化物沉淀,同时也会对圆片造成一定的损坏,随后高温退火形成二氧化硅绝缘层。尽管之后的高温退火能够一定程度的修复圆片,但是这两个过程不可避免的还是会对顶层硅膜的质量造成损伤,最终导致形成的栅氧层中存在较多的缺陷,从而加速了栅氧化层的击穿,使得栅氧寿命变短。

我们又对三组样品的栅氧电容击穿电压做了比较,如图7。从图上发现,体硅样品的栅氧击穿直到9 V的时候才出现漏电,而另外两个SOI样品的栅氧击穿在7 V的时候就出现漏电。因此认为,SOI样品存在较大的由应力导致的漏电SILC。

关于应力导致的漏电问题,目前已经提出了几种机制进行解释[13~15]。Dumin和Rico认为高压应力下,氧化层内部和界面将会有陷阱产生,陷阱的存在成为过渡能级。电子从阴极导带隧穿入陷阱能级,进而又从该陷阱能级隧穿到阳极导带,陷阱辅助电子隧穿从而产生SILC。陷阱密度较高的区域,其额外泄漏电流就越大。而SOI材料片由于离子注入引发了较多的陷阱,因此,在相同的应力条件下较容易产生隧穿电流。当某个局部区域陷阱浓度超过临界值时,就会促使低能级电流增加,热量将会沿着该局部路径逃逸,在阴极和阳极之间会形成一个短路通道,从而发生击穿。从图上还能看出,增加了抗总剂量辐射加固工艺的样品击穿电压小于未作加固的样品,这同样可能是由于加固工艺过程中的离子注入引入了部分陷阱导致的。

3 结论

本文对体硅片、SOI材料片、抗总剂量辐射加固的SOI材料片上的栅氧电容结构进行了栅氧可靠性评估,使用了恒压应力法,结果说明栅氧的击穿时间与应力大小成反比,证明栅氧介质的击穿时间主要由第一阶段缺陷积累时间决定。对比三组样品的栅氧寿命,体硅样品的寿命最长,未加固SOI样品次之,加固SOI样品最小,但两者相差不多,这主要是由于离子注入引入的陷阱造成的,总的来说寿命满足10年的要求。后续考虑用其他方法制备的SOI材料片做进一步研究,以减少离子注入带来的损伤对栅氧寿命的影响。

[1]Auberton-Herve A J.SOI: materials to systems [J].IEEE International Electron Device Meeting Technical Digest,1996.

[2]Hatano H.Radiation hardened high performance CMOS VlSI circuit design [J].IEE Proceedings-G,1992,139:287.

[3]Brady F T,S cott T,Brown R,et al.Fully-depleted submicron SOI for radiation hardened application [J].IEEE Trans NuclSci,1994,41:2304.

[4]Yang Hui,Zhang Enxia,Zhang Zhengxuan.Effects of Si Ion Implantation on the Total-Dose Radiation Properties of SIMOX SOI Materials [J].Chinese Journal of Semiconductors,2007,28(3):323-326.

[5]Gao Xiang-dong,Wu Jian-wei,Liu Guo-zhu,Zhou Miao.Study of Radiation Hardened SOI Gate Oxide Reliability[J].2012,8(12):44-48.

[6]Zhang J F,SiiHK,Groeseneken G et al.Hole trapping and trap generation in the gate silicon dioxide [J].IEEE tans.On Eleetron Deviees,2001,48(6):1127-1135.

[7]Buehanan D A.Sealing the gate dielectric:Materials,integration,and reliability [J].IBM J.Res.Develop.1999 43(3):245-264.

[8]史保华,贾新章.微电子器件可靠性[M].西安:西安电子科技大学出版社,1999.

[9]K F Schuegraf.Effects of temperature and defects on breakdown lifetime of thin SiO2at Very low voltages [J].IEEE Trans.Electron Devices,1994,41:1227-1232.

[10]K F Schuegraf.Holes injection SiO2breakdown model for very low voltage lifetime extrapolation [J].IEEE Trans.Electron Devices,1994,41:761-767.

[11]D J Dumin,S K Mopuri,S Vanchinathan.High filed related thin oxide wearout break-down [J].IEEE Trans.Electron Devices,1995,42:760-772.

[12]D J Dumin,S Vanchinathan.Bipolar Stressing,breakdown and trapping generation in thin silicon oxides [J].IEEE Trans.Electron Devices,1994,41:936-940.

[13]J Maserjian,N Zamani.Observation of positively charged state generation near the Si-SiO2interface during fowlernordheimtunneling [J].J.VacSci.Tech.,1992,20:743-746.

[14]刘红侠.超薄栅氧化层经时击穿效应与可靠性仿真技术研究[D].西安电子科技大学博士学位论文,2001.

[15]刘红侠,郝跃.薄栅介质TDDB效应[J].半导体学报,2001,22:1592-1595.