基于0.18μm CMOS高压工艺的低压器件优化设计

2014-09-19华梦琪宣志斌张又丹

朱 琪,华梦琪,宣志斌,张又丹

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

近年来,各种功率MOS器件层出不穷,由于其具有开关速度快、输入阻抗高、热稳定性好,高可靠性等优点,在应用中取代了许多双极型功率器件,在国内IC制造领域得到了广泛的应用。其特殊的工艺特点推动了电力电子技术的迅猛发展。

现代工艺技术通过把高耐压的HVMOS、LDMOS器件和数字CMOS 控制器件以及BIPOLAR模拟器件集成在一起,形成HVLDMOS、BICMOS或BCD工艺,为各种驱动设计提供便捷的工艺平台。随着应用领域的扩展,常规CMOS低压器件的局限性与高压器件的兼容性等问题越来越突出,亟待有效解决方案出台。本文从版图的角度提出了优化设计方案,解决了在0.18 μm工艺平台下高低压器件间的兼容性问题。

2 工艺选择

普通CMOS晶体管可传导大电流,但工作电压有限制。双扩散MOS或DMOS(Double Diffused Mosfet)晶体管器件结构紧密,可承受大电流和大电压。随着横向DMOS晶体管的发展及Resurf技术进步,许多工艺都提供双扩散MOS或DMOS晶体管作为工艺扩展,横向DMOS晶体管已经成为15 V及以上功率器件的首选。

本电路中的电源最高为±15 V,基于电路的工作电压较高,考虑采用DMOS器件,并在30 V耐压的前提下比较1 mm2面积内DMOS器件的导通电阻Ron大小来决定工艺的选择;对于数字CMOS控制器件的选择,要求高压器件的宽长可调,Ron和BVds都符合本电路的性能要求,并且要求设计中可以自由选择HVMOS、LDMOS类高压器件。高压工艺为了实现高压器件的高耐压特性,并兼容特定的CMOS低压器件,高压器件与低压器件的版图设计都有特定的设计标准,晶圆厂家一般都是根据工艺条件进行规范参数设计,不可随意更改。虽然可以通过采用集成进诸如外延[1]等复杂的工艺技术来实现工艺集成,获得优越的器件性能,但这势必增加工艺复杂度和生产成本,故不考虑使用外延片。此外综合考虑芯片面积要求及封装要求,最后选用了普通SMIC 0.18 μm 40 V HV-LDMOS工艺进行设计。

3 设计中面临的问题

高压工艺设计时,需要性能优良的器件,同时也需要工艺能整合出可塑性的器件,方便设计时灵活应用。但为了降低成本,设计中选择的是SMIC 0.18 μm 40 V HV-LDMOS工艺,且为不带外延的High Voltage工艺,工艺中LDMOS器件结构通过自身的高压阱实现了电位隔离和40 V的耐压;CMOS低压器件应用了浮动盆结构,使器件源端与衬底之间可以引入不同电位。但是该工艺是SMIC基于P型衬底接0 V的基础上,配合端口设计需要用到HV device器件而开发的高压工艺。所以针对该项目多电源、多电压的转换,低压器件应用时产生了局限性。目前P衬底接VCC-(-15 V),电源接VCC+(+15 V),可获得最高压差30 V,5 V低压器件的最高压差只可达20 V。

典型电路见图1,这是一个线形稳压器的电路图,由运放①、调整管②和分压电阻③组成。其功能是利用一个15 V左右的电压生成5 V的稳恒电压。运放的作用是采样稳压器输出,形成负反馈,调节调整管得到稳定的输出电压。调整管为大尺寸的高压管,接成源极跟随器形式。运放的正端接入来自带隙基准的输出电压。该运放为单级共源共栅运放,具有增益高、稳定性好、功耗低的特点,不足之处为消耗的电压过大,正好适用于本电路的应用条件。在本电路采用的工艺中,高压管栅氧较厚,跨导较小,而低压管具有较好的跨导性能。为增大运放的增益,提高系统性能,在保证了安全的电压工作范围后,本电路中运放的输入对管采用了低压管。运放输出端还添加了电阻和电容构成的补偿结构,通过调整电阻和电容的取值,调节零极点的分布,改善系统的稳定性。

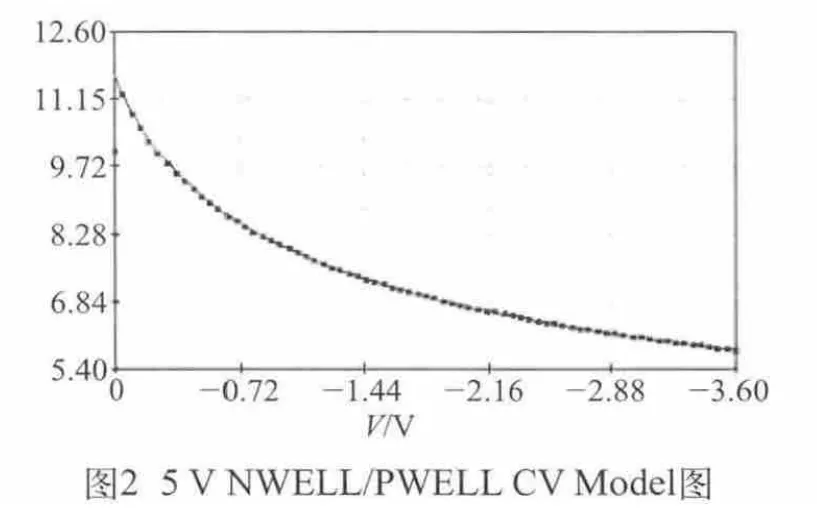

而对于此工艺的LDMOS高压器件来讲,可以满足电特性;但是对于兼容使用的低压器件来讲,压差20 V超过了此工艺低压器件的击穿电压(见图2)。

考虑到低压器件所能承受的横向和纵向的击穿电压特性[2],而器件的耐压在30~40 V之间并不是一个特别高的SOA(Safe Operation Area)[3]指标,但要在不增加工艺版次与成本的前提下,在同一芯片上实现多电源、实现电路的高低压转换,满足各种器件的电特性指标,对所采用的工艺来说是一个极大的难题,需要从一个全新的角度思考,以期满足器件的电压要求。

4 器件的版图优化

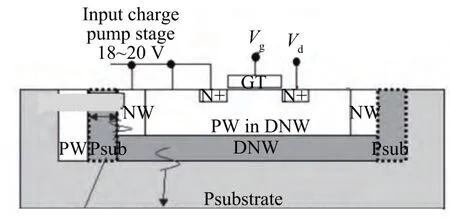

在设计中,尽量量化、确认器件电压的种类,把器件电压控制在可应用范围内来优化高压器件与低压器件的兼容性。考虑到高压工艺的纵向结构和结深一般都是不可更改的,并且高压工艺的纵向击穿电压一般比较高,因此从低压器件入手,考虑低压器件的横向击穿特性,尝试通过改变低压器件的横向阱间距来提高横向击穿电压,使得低压器件的横向与纵向的击穿电压特性都能满足最高压差20 V的要求。因此在设计时,把常规低压CMOS器件(见图3),通过添加一个现有的版图设计层次,作为辅助层来调整低压器件的版图设计,此辅助层的应用是希望最后版图数据根据mask逻辑运算生成所需mask版,且在mask不冲突的前提下,使得数据生成后NWELL和PWELL可以有一个较宽的间距,即展宽NWELL与PWELL之间的耗尽层,以便提高5 V器件的横向击穿电压,改进后的版图器件及纵向结构如图4、图5所示。

图3 5 V NMOS_ isolation和5 V PMOS器件版图

图4 改进后的5 V NMOS_ isolation和5 V PMOS器件版图

图5 NMOS纵向结构示意图

此设计方法的应用不需要增加额外的光刻次数,不增加额外的生产成本,但又满足了稳定的生产和电性能指标,同时实现了低压器件设计上的创新和突破。

5 仿真与流片测试结果

新的设计需要有一系列的数据验证,工艺配合设计,通过工艺仿真软件仿真了工艺的可行性,为优化版图设计提供了重要的参考数据。基于CMOS器件电压为5 V,NW和Psub的击穿电压需要大于20 V,通过TCAD仿真结果显示如图6所示。

PW-DNW-Psub的击穿电压需要大于15 V,通过TCAD仿真结果显示如图7。

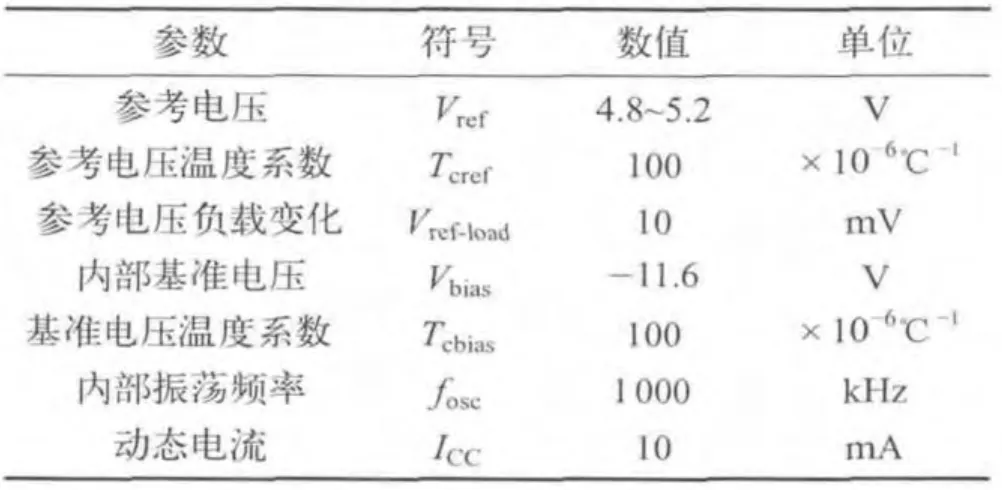

仿真结果显示MVPW-DNW-Psub的Breakdown inVPW可以达到57 V左右,满足设计要求。采用此设计后,该芯片主要性能参数如表1所示。

表1 芯片实际测试性能参数

6 结论

本文对基于SMIC 0.18 μm 40V HV-LDMOS工艺的CMOS低压器件的版图设计进行了改进,通过理论分析、仿真验证、流片测试结果表明,版图采用此优化设计,在±15 V电源下,高压器件和低压器件都没有发生击穿漏电现象,电路工作稳定、性能可靠,整体性能良好。

[1]朱正涌.半导体集成电路[M].北京:清华大学出版社,2001.

[2]Alan Hastings.模拟电路板图的艺术[M].北京:电子工业出版社,2007.

[3]P L Hower.Safe Operating Area: a New Frontier in Ldmos Design [C].Proc.14th Int.Symposium on Power Semiconductor Devices and ICs,2002,1-8.