极大规模集成电路测试技术发展

2014-09-19刘远华

刘远华

(上海华岭集成电路技术股份有限公司,上海 201203)

1 引言

集成电路工艺进步和设计技术发展促使芯片功能日益复杂,集成度越来越高,其测试越来越困难。极大规模集成电路测试的理论与技术已经成为现代集成电路领域中的一个重要研究方向。

极大规模集成电路测试技术的发展主要延续两条路径,一是对完备性测试技术的研究开发,体现了人们对科学技术研究和集成电路设计、制造及功能、性能尽善尽美的追求;另一条路径则是不断研究开发提高测试质量、降低测试成本、提高测试效益的产品化测试技术。前者主要包括集成电路的评测和芯片测试验证分析,后者主要是产业化测试生产。而同时,极大规模集成电路测试技术的发展与整个产业链的发展是密不可分的,集成电路测试贯穿设计、制造、封装与应用整个产业链,本文对测试与设计、封装、应用等产业链环节联接的典型技术一一进行了描述。

2 集成电路测试面临的挑战

目前中国集成电路产业思路为以市场应用为导向,整机与芯片联动[1]。拉动产业发展的应用领域有移动互联网、物联网、可穿戴应用等,其引领了集成电路设计的发展。集成电路产品外形上向“轻薄短小”发展,技术上主要设计趋势为高速和高集成度[2]。

2.1 高速对测试的挑战

高速不仅体现在集成电路工作频率高,同时也体现在接口单元数据速率越来越高,低电压、高速度是集成电路发展的一个典型方向。

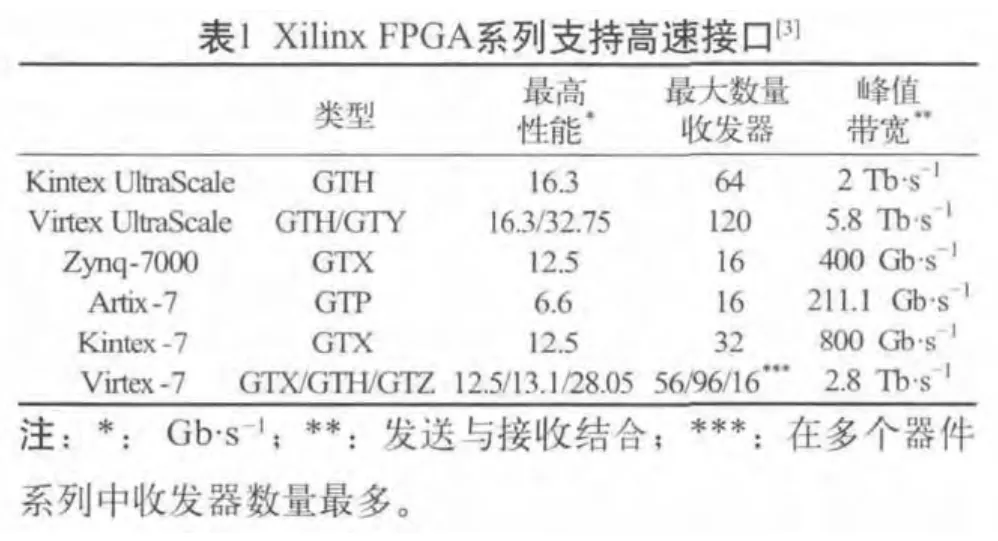

表1显示了Xilinx高速接口目前支持的速率,在计算、网络、消费电子领域,多种Gbps/GHz的高速接口不断发展,如PCIe、hyper-transport、QPI、GDDR、DisplayPort、DDR、USB、Infiniband、SATA、SAS、Fiber channel、Gigabit Ethernet、XAUI、SONET、OTU和OIF/CEI等均得到广泛应用。高速串行和差分接口协议的发展又推动了DFT设计和生产测试技术的革新。

表1 Xilinx FPGA系列支持高速接口[3]注:*: Gb·s-1;**:发送与接收结合;***:在多个器件系列中收发器数量最多。

在过去几年,业内领先的测试技术研发机构均针对高速接口推出了相应的高速串行链路测试解决方案,如美国泰瑞达公司的ULTRA SERIAL10G、SB6G、日本爱德万公司T2000 HSDM3、V93000 Smart Scale等。到目前来讲,应该说10 Gbps左右的高速接口已有了完善的测试解决方案,但是由于上述技术本身主要基于仿真应用场景和应用功能测试的指导思想,往往落后于当前市场更高端芯片的测试需求,因此在大量技术研发实践的基础上,目前高速、高精度集成电路的生产测试解决方案更多的是从集成芯片DFT设计的内部数字回环、辅以DFT的数字回环、外部连线回环、外部有源回环和芯片外部ATE专用测试选件、测试模块、测试负载板等方面进行系统考虑,权衡测试用户要求、性能、成本和研发时间等,提出成套测试解决方案。

2.2 高集成度对测试的挑战

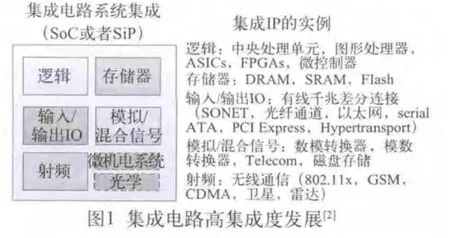

随着可穿戴、智能移动终端的发展,高集成度顺应了集成电路“轻薄短小”的趋势,用尽可能小的空间、尽可能低的功耗,低成本实现产品功能和性能的优化是集成电路设计领域的发展趋势。SOC(系统级芯片)和SiP(系统级封装)芯片是达到这一目标的两条不同途径。无论在SoC还是SiP技术中,众多新兴技术均列入集成IP核范畴,如MEMS、光电转换等,即使是传统的集成IP,如逻辑、存储器、IO、模拟/混合信号、射频IP,其技术复杂度或性能与以往相比也有较大的革新,如逻辑IP中CPU向多核心体系发展;嵌入存储器的容量和性能得到较大提升;输入输出IO的类型不断丰富、带宽不断提高;模拟/混合信号集成的模数/数模转换器无论是分辨率、转换速率、性能均有提高;射频IP也向更高载波频率和性能发展。

集成电路测试面对集成度越来越高的情况,首先对DFT技术提出新的要求,数字DFT相对成熟,但在现在如此高集成度的情况下,DFT不但要侦测出失效、还需要定位失效,而对模拟/混合/射频的DFT需求就更为迫切,因为目前尚缺乏较完善的模拟/混合/射频的DFT方案。同时,测试在原来的多工位测试上也要有所发展,必须研发并发测试、自适应测试等技术方案。高集成度的集成电路测试变得日益复杂,需要在测试流程中对芯片进行定制或者对芯片进行修复,尤其在SiP(系统级封装)中,必须在传统测试中增加新的测试环节,如3D封装测试中mid_bond test和post_bond test环节也变得必要[4],其面临着测试流程、测试访问、异构堆叠、诊断调试、功耗等关键性测试挑战。

2.3 成本对测试的挑战

随着我国集成电路进入55 nm-40 nm-28 nm技术领域,芯片产品集成度越来越高,功能性能越来越复杂,原来复杂的电子系统变成了现在的单芯片,因此芯片测试的复杂度极大提高了,使得集成电路测试成本不断提高。根据ITRS(国际半导体技术路线图)调查,测试技术的价值贡献最主要在于集成电路产品的质量控制和产品良率提升,目前有40%的人认为测试成本不断提高是其最担忧因素之一,同时有85%的人认为预期降低测试成本的技术是未来最大的挑战之一。

当前影响测试成本的因素主要有昂贵的ATE费用和配套接口部件、ATE整体利用效能、测试程序开发费用、测试时间和故障覆盖率;同时可以看到的是集成电路发展带来的新缺陷和可靠性成本、新的封装技术带来的测试需求、高速高密度接口持续提高的成本、数据处理方面的成本。目前集成电路测试领域主要应对的方案包括并行测试、压缩芯片引脚数量以减低对测试通道需求、结构测试、扫描测试、BIST、DFT、并发测试、自适应测试、芯片级全速测试等,正发展的测试解决方案包括采用更先进经济的嵌入式仪器,如PXI导入[6],新的连接技术如无接触探测方案,系统级测试、容错、测试数据服务器集中处理等,这些测试技术将持续研究,以图遏制测试成本持续上升的态势。

3 测试与产业链

集成电路测试贯穿在集成电路设计、芯片制造、封装及集成电路应用的全过程。

测试设计、开发、量产与集成电路产业链环节均存在密切的联系。

3.1 测试与设计

在设计阶段利用EDA工具对芯片进行建模、设计、仿真、测试等工作,与设计环节衔接,测试需要解决设计与测试文件的兼容性。通过EDA导出的测试文件有VCD、EVCD、WGL、STIL等波形格式,这些文件通常并不能被ATE自动识别,需通过时序分割、周期化、矢量生成,自动转换、矢量压缩等技术,将基于事件(Event-Based)波形转换为ATE能识别的基于周期(Cycle-Based)向量,以实现激励信号送入器件的输入管脚,在输出管脚检测响应输出,与仿真文件转换的期待值进行比较,从而验证器件的功能。

由于设计仿真和芯片功能的不同,通过工具转换VCD而生成的测试向量,会生成较多的时序沿,而导致无法转换为ATE适用的测试向量,通过分析波形文件的语法结构和特点,设计测试时序优化算法[7],可以解决部分VCD转换后时序沿和测试波形数量过多的问题。而随着集成电路规模的变大,为保证足够的测试覆盖率,测试向量深度变成一个天文数字,同时占用的ATE测试向量存储空间过大,很多情况下无法一次性加载,导致整个测试开发进程拉长和测试效率下降、测试成本上升,因此不仅需要在仿真文件时进行相应压缩,在生成的测试向量中也需要采用相应的压缩算法与技术来解决以上问题。

3.2 测试与制造

目前具备先进工艺能力的集成电路制造企业屈指可数,尤其是到了40 nm工艺后。这些制造企业通常具备较完整的数据分析工具以提高工艺良率,测试需要解决的典型要求有测试数据信息化无缝联接要求,如测试生产线的数据与制造企业数据分析系统互联等。

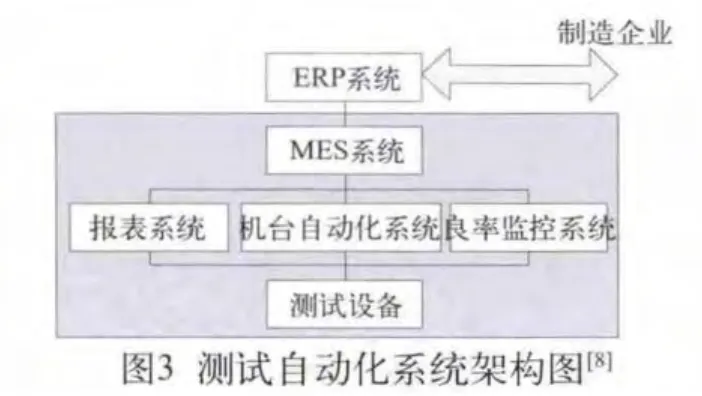

图3是一种半导体测试企业的自动化系统架构图,利用现代网络技术和自动化技术,开发企业资源规划系统、产品数据管理系统、仓库管理系统、制造执行系统、客户关系管理系统、物流管理系统等,实现在线良率自动规则过滤与监控。在测试程序、测试规范、测试数据、报表、图表、软件、图纸、计划、波形等方面实现实时互动,实现全格式兼容,信息实时传递。

3.3 测试与封装

晶圆测试在封装前进行,测试结果通常以ink磁性墨点方式和inkless map文件两种方式传递,当大芯片工艺发展到12英寸后,原ink的方式已被产业界淘汰,基本为inkless map方式作为测试结果,该文件除了作为封装应用外,同时可提供给制造、设计企业。

同时测试结果往往需要与Visual Inspection结果进行合并以确定最终的测试结果,因此inkless map是测试需要解决的关键问题。

不同的封装企业对inkless map会有不同的格式要求和规定[9],在测试环节,需要在灵活匹配的前提下,实现测试与封装满足国际标准的test map自对准技术、自对准精度,在提交good die芯片的同时,提供准确inkless map文件。

4 结束语

随着集成电路工艺制程、集成技术、产品技术的不断发展,极大规模集成电路测试面临愈加严峻的挑战,本文讨论了新出现的测试技术以及传统测试技术的革新,推动了整个集成电路产业技术进步,同时讨论了如何在提高测试覆盖率的情况下降低测试成本,提高测试开发效率,缩短测试周期的测试业难题。相信通过测试与产业链互动和互联网、云计算的结合,极大规模集成电路测试技术必将引来新的飞跃突破。

[1]工业和信息化部.集成电路产业“十二五”发展规划[EB/OL].http://www.miit.gov.cn/n11293472/n11293832/n11293907/n11368223/n14473435.files/n14473350.doc.

[2]INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS.TEST AND TEST EQUIPMENT[EB/OL].http://www.itrs.net/Links/2013ITRS/2013Chapters/2013Test.pdf.

[3]Xilinx.Transceiver Offerings [EB/OL].http://www.xilinx.com/products/technology/high-speed-serial/index.htm.

[4]Brandon Noia,Krishnendu Chakrabarty.Design-for-Test and Test Optimization Techniques for TSV-based 3D Stacked ICs [M].Switzerland:Springer International Publishing,2014:159-180.

[5]M Bhushan,M B Ketchen.Microelectronic Test Structures for CMOS Technology [M].LLC:Springer International Publishing,2011,317-357.

[6]NATIONAL INSTRUMENTS.Semiconductor [EB/OL].http://www.ni.com/automatedtest/semiconductor/zhs

[7]陈辉,姚若河,王晓晗.一种ATE测试向量时序优化算法[J].微电子学,2011,41(2).

[8]郭旭棋.12寸半导体测试厂自动化研究[D].上海交通大学,2007.

[9]XUELIN ZHOU.DESIGN OF AN AUTOMATED INKLESS WAFERMAP SYSTEM [D].Texas Tech University,2001.