3D-TSV封装技术

2014-09-19燕英强明雪飞

燕英强,吉 勇,明雪飞

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

TSV(Through Silicon Via,硅通孔)技术可实现芯片与芯片间垂直叠层互连,无需引线键合,有效缩短互连线长度,减少信号传输延迟和损失,提高信号速度和带宽,降低功耗和封装体积,是实现多功能、高性能、高可靠且更轻、更薄、更小的半导体系统级封装的有效途径之一[1~4]。

TSV工艺分前通孔和后通孔,但具有相同的关键技术:通孔制作、通孔薄膜淀积技术、通孔填充、铜化学机械研磨、超薄晶圆减薄、芯片/晶圆叠层键合。

2 通孔制作技术

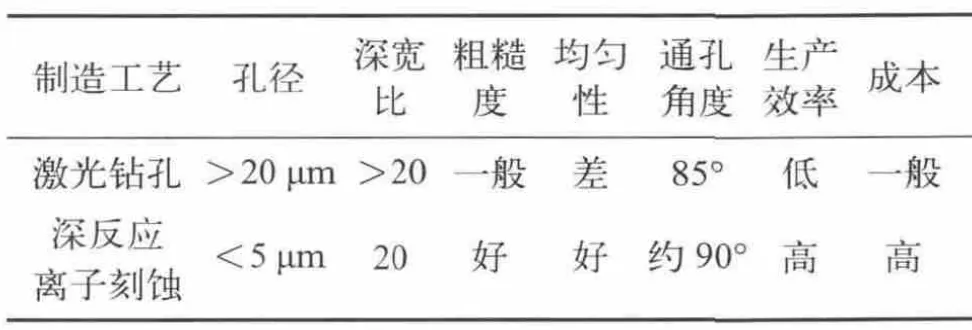

制作TSV通孔的方法主要有:激光钻孔(Laser Drill)、深反应离子刻蚀(DRIE)等,其工艺特性参见表1[5,6]。

表1 不同通孔制作技术特点

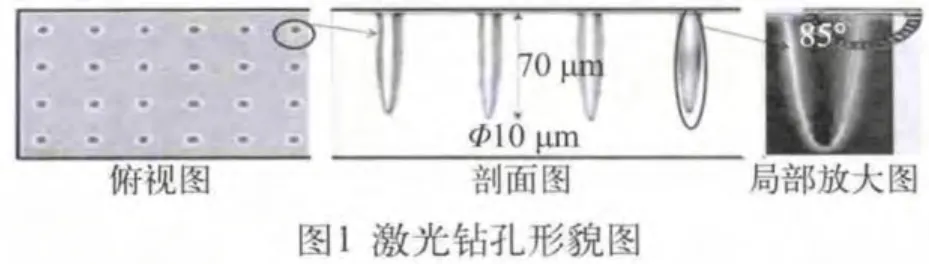

2.1 激光钻孔技术

激光钻孔技术是利用激光的局部超高温度使材料汽化而形成通孔。激光钻孔技术无需掩模材料,一次性穿透芯片表面绝缘层、金属层和硅基体,形成TSV通孔;且激光钻孔技术可形成侧壁倾斜的通孔(图1),利于侧壁钝化层或种子层薄膜淀积和电镀填充。

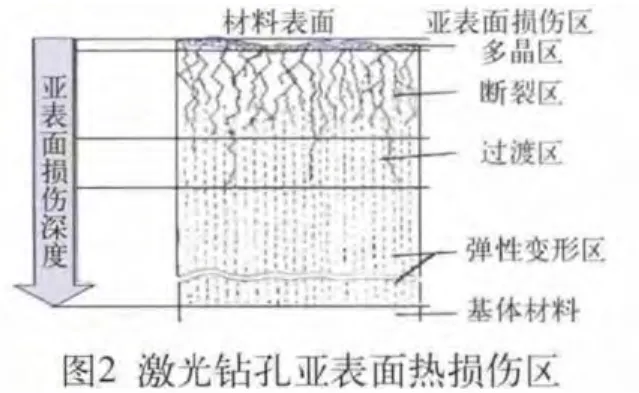

但激光钻孔也有其缺点和不足[7],参见图2,无法满足未来更小孔径、高深宽比TSV通孔制作:(1)硅熔化再快速凝固,易在通孔表面形成球形瘤,通孔内壁粗糙度较大,难以淀积连续绝缘层/种子层;(2)通孔内壁亚表面热损伤较大(图2),影响填充后孔的可靠性;(3)制作通孔尺寸精确度<5 μm。

目前,激光钻孔技术可以加工直径10 μm的通孔,但只适用于直径大于25 μm的硅通孔商用加工[6]。随着通孔直径逐渐减小,为提高通孔精度和热损伤,UV(紫外)激光已取代红外激光。激光钻孔技术需要重点解决机械装置移动精度低、可重复性低及生产效率低、降低亚表面热损伤等问题。

2.2 深反应离子刻蚀

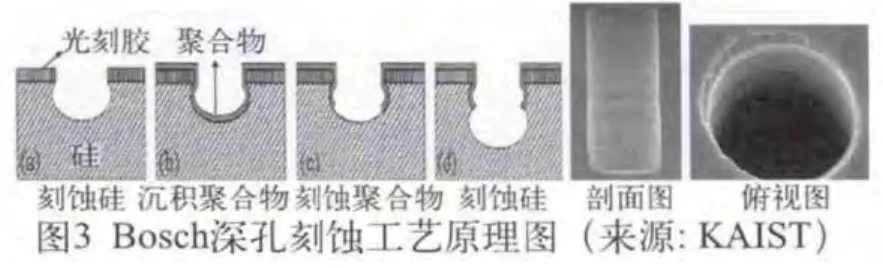

深反应离子刻蚀,采用“博世”深孔刻蚀工艺。在每个刻蚀/钝化循环周期中,暴露的硅被SF6各向同性刻蚀,再通过C4F8在通孔内壁淀积一层聚合物保护层,然后聚合物被分解去除,暴露的硅再被蚀刻,周而复始快速循环切换刻蚀和钝化,直至通孔达到工艺要求而结束。在每个刻蚀周期中都会在通孔侧壁上留下扇贝状的起伏,见图3。

深反应离子刻蚀技术必须借助厚膜光刻技术,在晶圆表面预先形成通孔图形,利用晶圆材质与掩模材料的不同刻蚀速率(刻蚀比>50:1),形成垂直通孔,其具有以下特点:(1)通孔直径≤10 μm,深宽比大于10:1;(2)通孔侧壁呈垂直或较小锥度,利于深孔金属填充;(3)通孔侧壁要足够光滑,扇贝尺寸≤100 nm,确保获得连续的金属膜层;(4)通孔侧壁无热损伤区,提高通孔可靠性。

常用填充金属铜膨胀系数远大于硅、砷化镓等材料而易导致可靠性问题。为提高可靠性,TSV通孔直径越小越好,应小于10 μm,只有深反应离子刻蚀满足此需求,将成为硅通孔制作技术的必然选择和主流技术。

3 通孔侧壁薄膜淀积技术

完成金属填充前必须淀积绝缘层,隔断填充金属和硅本体材料的电导通。接着淀积粘附/扩散阻挡层和种子层金属。粘附/扩散阻挡层阻挡填充金属向绝缘层和本体材料扩散,同时与绝缘层和种子层具有良好的粘附性。

3.1 通孔侧壁绝缘层淀积技术

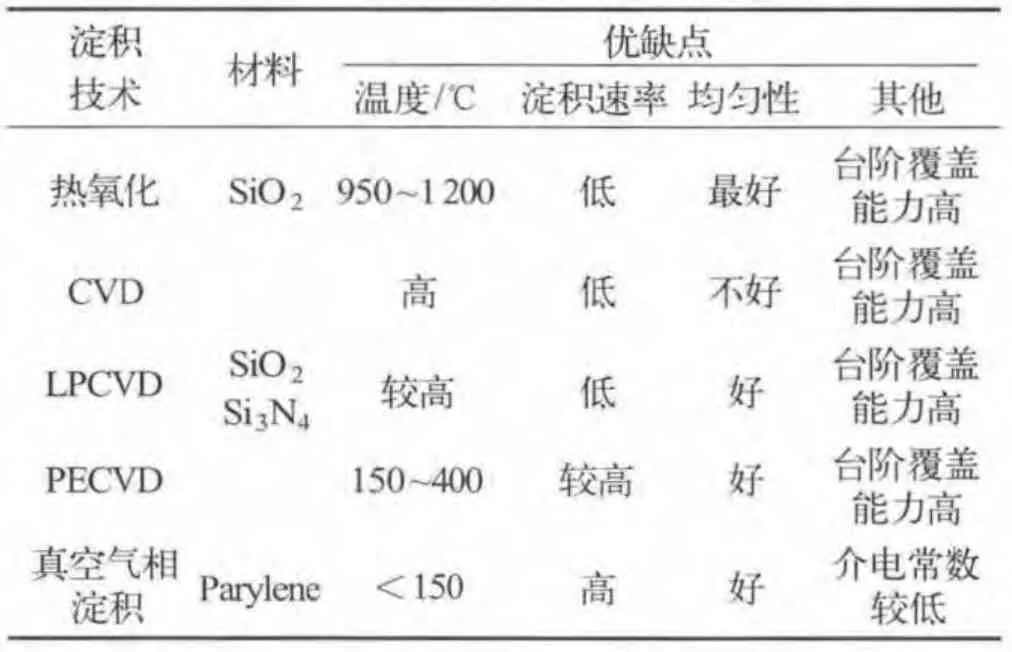

通孔内绝缘层材料有硅氧化物、硅氮化物、聚合物等。不同绝缘层,需要不同淀积技术,如表2。PECVD技术淀积速率高,工艺温度最低且膜层覆盖能力强,广泛应用于淀积SiO2、Si3N4等绝缘层材料。真空气相淀积Parylene作为硅通孔侧壁绝缘层,在TSV工艺中也获得广泛使用。

表2 通孔侧壁绝缘层淀积技术

3.2 通孔侧壁粘附/扩散阻挡层及种子层金属淀积技术

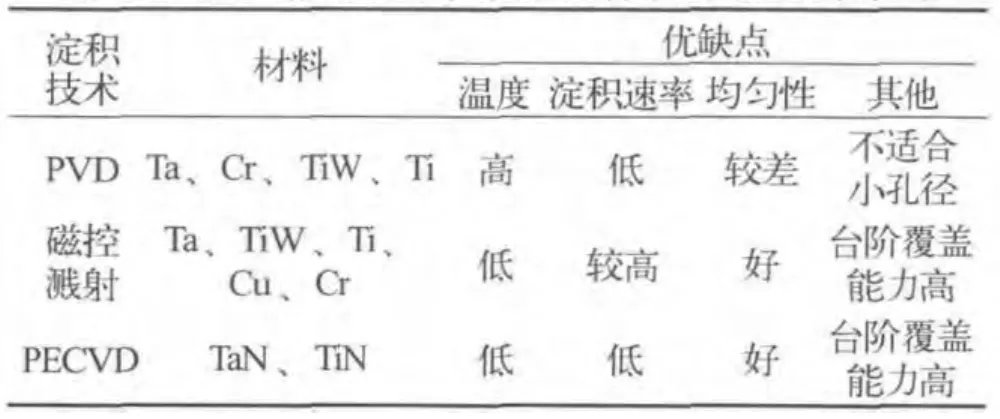

通常TSV工艺采用电镀铜工艺进行通孔填充。Cu在SiO2介质中扩散速度很快,易使其介电性能严重退化;Cu对半导体的载流子具有很强的陷阱效应,Cu扩散到半导体本体材料中将严重影响半导体器件电性特征;Cu和SiO2的粘附强度较差,必须在二者中间淀积一层Ta、TaN/Ta、TiN、TiW、Cr、Ti等扩散阻挡层,防止铜扩散并提高种子层的粘附强度。常用淀积技术见表3。

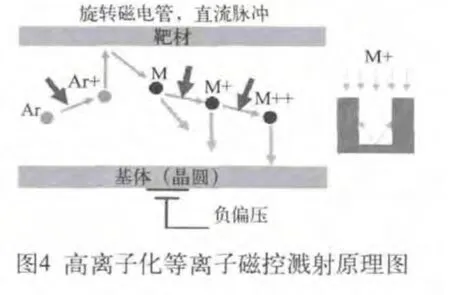

通常TSV硅通孔深宽比大于7:1,甚至达到12:1~15:1。常规磁控溅射技术难以在高深宽比通孔侧壁上淀积连续的金属层,设备厂商开发了高离子化金属等离子磁控溅射技术。

表3 通孔侧壁粘附/扩散阻挡层及种子层金属淀积技术

如图4,高离子化金属等离子磁控溅射技术,使用高峰值功率(几兆瓦)的直流脉冲功率电源能够产生比常规磁控溅射技术更高的等离子体密度、更高的淀积速率。同时晶圆被施加较高的负DC偏压,将金属离子以具有比非离子化金属更高的动量和方向性吸引到高深宽比通孔内,能够将金属从通孔底部再溅射到通孔侧壁上,将金属从扇形槽的下表面再溅射到受屏蔽的扇形槽上表面,从而产生电镀所需的致密、连续的粘附/扩散阻挡层和种子层金属[8,9]。

4 TSV通孔填充技术

Cu电阻率(1.678 μΩ·cm)较小,成为TSV通孔填充材料首选。通孔铜填充技术有磁控溅射、CVD、ALD(原子层淀积)、电镀等,由于电镀成本更低且淀积速度更快,铜电镀工艺成为TSV通孔填充首选。

均匀铜电镀技术已经被广泛应用于低成本圆片级封装,电镀时通孔侧壁和底部均匀生长,凸出位置生长速度更快。如被用于深孔填充,底部未完成填充时通孔开口可能已封闭,就会形成电镀空洞。显然均匀电镀工艺不适用于小孔径、高深宽TSV深孔填充。为满足无孔洞铜电镀,开发了“自底向上”电镀工艺。

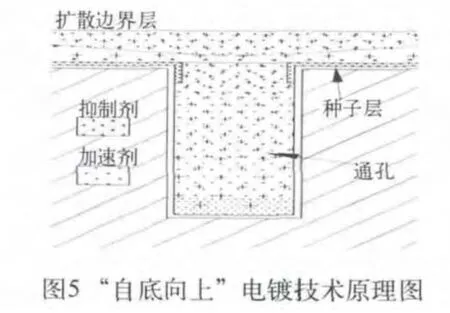

“自底向上”电镀技术,电镀时抑制通孔外表面的沉积速率而加速通孔内部的沉积,通过开发特殊电镀添加剂和电镀设备结构、电场的特殊设计等技术手段来实现[10],参见图5。

(1)强吸附力抑制剂,覆盖在铜表面的原子位置来抑制表面铜沉积;(2)加速剂成份来抵消抑制剂的作用来加速通孔底部铜的沉积速率;(3)整平剂和/或增亮剂,抑制表面曲率分布引起的高电场区域的沉积,抑制凸出表面位置的快速成核;(4)加速剂成份在通孔底部聚集来抵消抑制剂的作用来加速通孔底部铜的沉积速率;(5)优化结构、电场特殊设计减小流体边界层厚度,减小加速剂在晶圆表面的浓度,降低铜淀积速率;(6)采用周期脉冲反向电流进行电镀,抑制通孔内壁尖锐表面生长[11]。

5 铜化学机械研磨技术

TSV工艺中,完成通孔铜电镀后,晶圆表面也淀积了一层较厚的不均匀铜层,晶圆/芯片Cu-Cu等金属叠层键合凸点表面需要较好的表面粗糙度和平坦度,都需要采用CMP技术去除多余铜并平坦化。铜CMP技术主要包括两个过程:(1)碱性抛光液中的氧化剂与Cu表面进行化学反应生成CuO和Cu2O,螯合剂使Cu2+或Cu+转化为极稳定的可溶螯合物进入溶液;(2)在磨盘、抛光垫及研磨料的作用下,化学反应的产物被研磨下来并被抛光液带离抛光表面,使未反应的表面重新裸露出来。以上过程循环进行,直到平坦度及厚度满足要求。

TSV工艺需要去除更多的Cu才可达到平坦化工艺要求。提高铜去除速率、同时减小碟形坑(Dishing)和侵蚀(Erosion)效应成为铜CMP的研究重点。需要开发新的Cu抛光液、抛光垫、CMP设备来降低Dishing和Erosion效应,提高铜CMP的平整性[12,13]。

6 超薄晶圆减薄技术

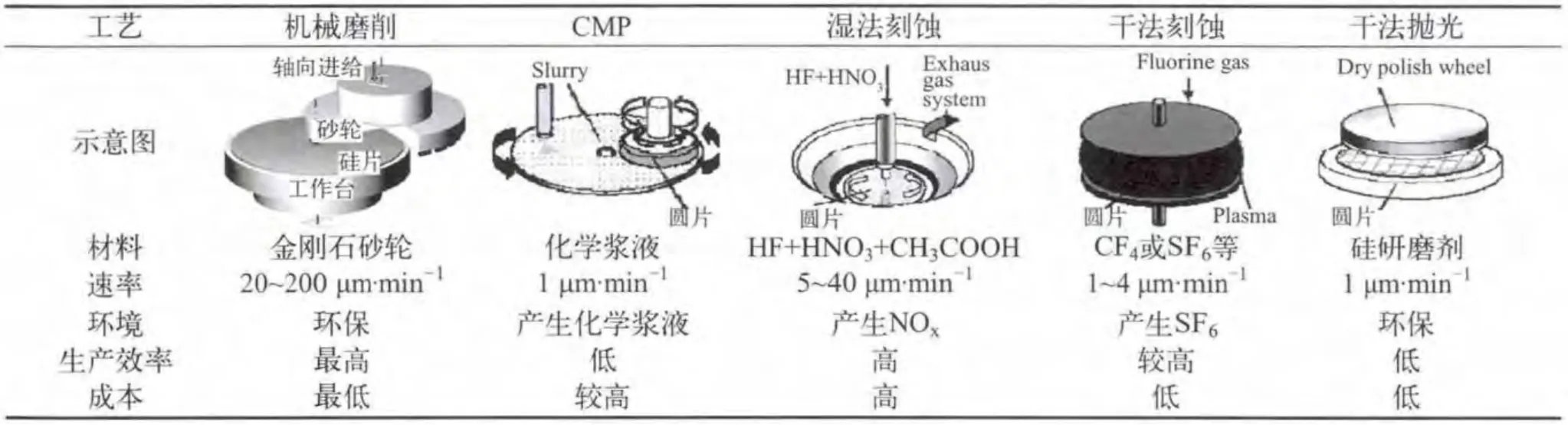

3D-TSV封装技术需要将晶圆/芯片进行多层叠层键合,同时还必须满足总封装厚度要求,必须对晶圆厚度减薄至30~100 μm。传统单一晶圆减薄技术(表4)无法满足工艺要求,需要开发超薄晶圆减薄技术。

当晶圆减薄至30 μm极限厚度时,要求表面和亚表面损伤尽可能小,一般采用机械磨削+CMP、机械磨削+湿式刻蚀、机械磨削+干法刻蚀、机械磨削+干式抛光等四种减薄工艺方案。

表4 晶圆减薄技术

150 mm、200 mm、300 mm尺寸晶圆减薄至150 μm时就会变得柔韧而容易变形或翘曲,为下步工序操作带来困难。目前业界的主流解决方案是采用一体机思路:将圆片的磨削、抛光、保护膜去除、划片膜粘贴等工序集合在一台设备内,圆片从磨片一直到粘贴划片膜为止始终被吸在真空吸盘上,始终保持平整状态,从而解决了工序间超薄晶圆搬送的难题。

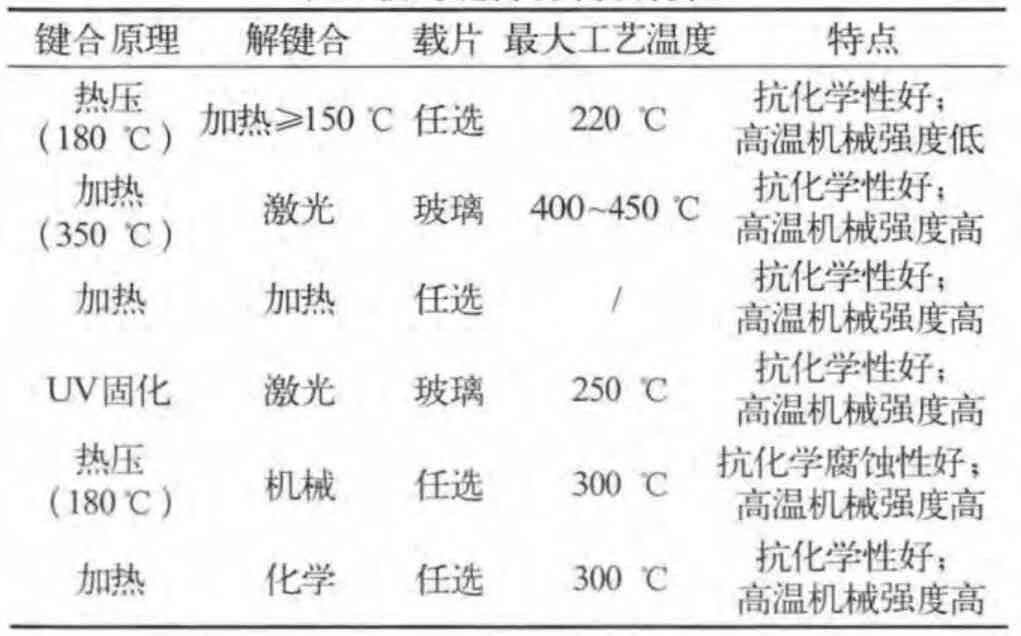

业界开发了晶圆临时键合技术,解决了厚度小于150 μm晶圆柔软而不易后续工艺操作的技术难题。晶圆临时键合技术,采用临时键合材料将晶圆预先键合到载片上,然后完成减薄或后续工序,再将减薄的晶圆与载片剥离。其关键技术是临时键合材料。目前,临时键合材料主要靠加热或UV固化进行临时键合,然后用加热、激光、化学、机械力解除键合。主要键合材料及特性参见表5[14]。

表5 临时键合材料及特性

7 芯片/晶圆叠层键合技术

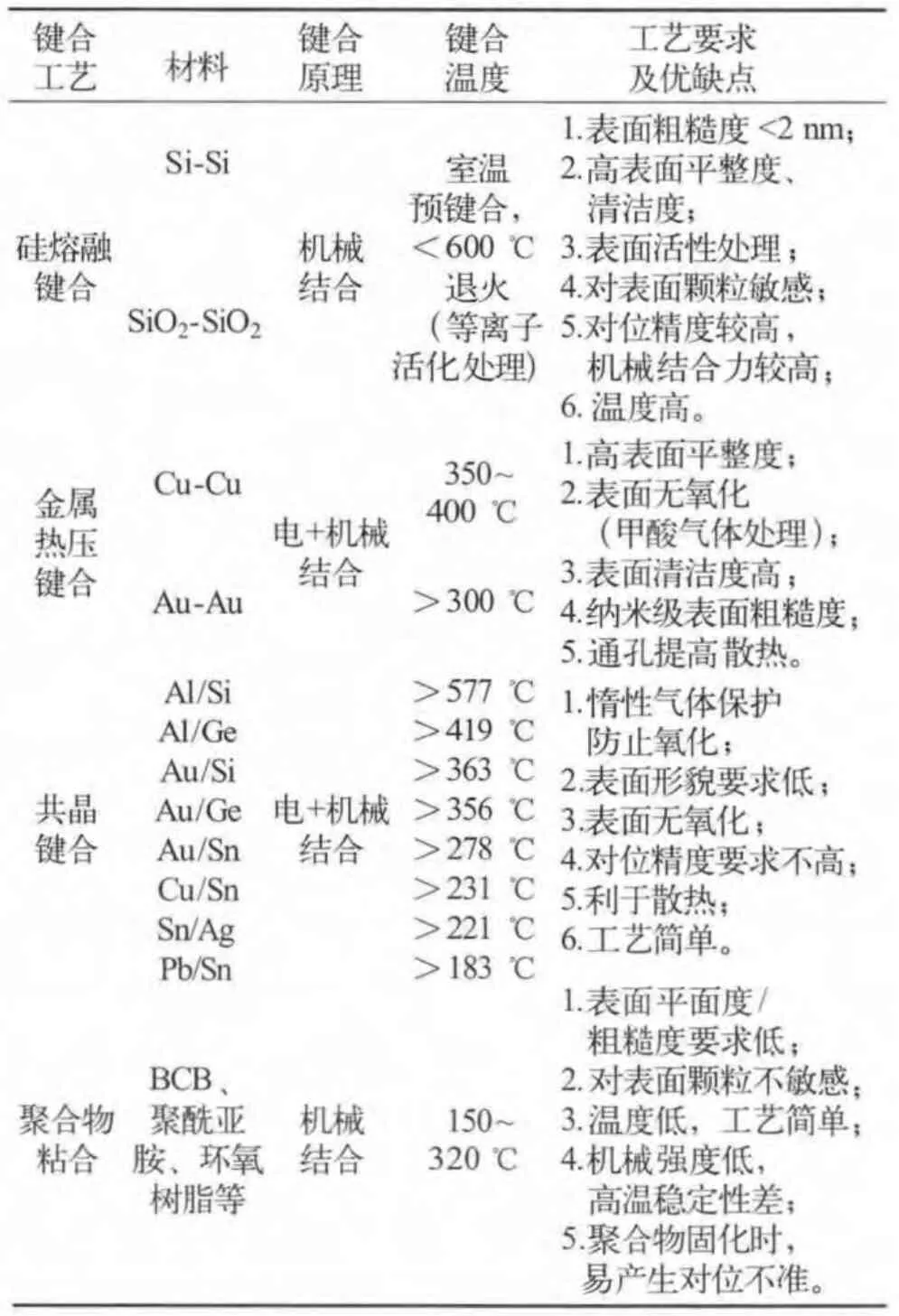

3D-TSV封装技术需要将不同材料、不同种类、不同尺寸的裸芯片在垂直方向进行叠层键合,实现机械和电气互连。

根据键合材料不同,主要有硅熔融键合、金属热压键合、共晶键合、聚合物键合等,参见表6[14~17]。硅熔融键合温度较高、工艺条件苛刻;聚合物键合热稳定性较差,较少用于3D-TSV封装,金属热压键合、共晶键合与现有半导体封装工艺设备兼容而被广泛采用。

表6 键合技术及工艺特点

8 3D-TSV封装技术应用

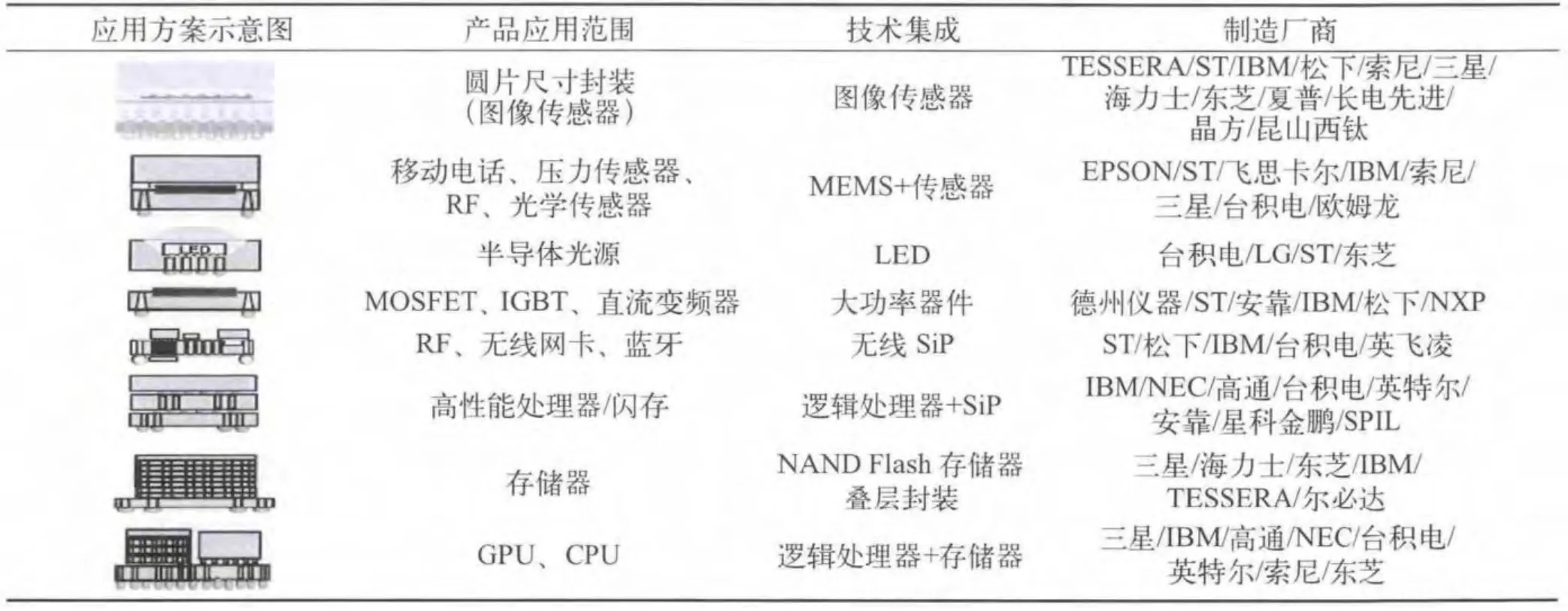

目前,3D-TSV系统封装技术主要应用于图像传感器、转接板、存储器、逻辑处理器+存储器、移动电话RF模组、MEMS晶圆级三维封装,见表7。

表7 3D-TSV封装技术典型应用案例

[1]童志义.3D IC集成与硅通孔(TSV)互连[J].电子工业专用设备,2009,170(3):27-34.

[2]赵璋,童志义.3D-TSV技术——延续摩尔定律的有效通途[J].电子工业专用设备,2011,194:27-34.

[3]Jet Propulsion Laboratory California Institute of Technology Pasadena [C].NASA 2009 Body of Knowledge(BoK):Through-Silicon Via Technology.

[4]陈海英.芯片级三维集成前景光明[J].混合微电子技术,2010,7(2-3):111-115.

[5]封国强,蔡坚,王水弟.硅通孔互连技术的开发与应用[J].中国集成电路,2007,3:5.

[6]詹印丰,颜锡鸿,许明哲.TSV制程技术整合分析[J].半导体科技,2010,5.

[7]Ralf RIESKE,René LANDGRAF,Klaus-Jürgen WOLTER.Novel Method for Crystal Defect Analysis of Laser Drilled TSVs [C].2009 Electronic Components and Technology Conference.

[8]Mohamed Elghazzali,Jürgen Weichart.Highly Ionized Sputtering for TSV-Lining [C].IMAPS 2010-43rd international Symposium on Microelectronics.

[9]Peijun Ding,Ling Chen etc.Cu Barrier/Seed Technology Development for Sub-0.10 Micron Copper Chips [J].Appied Material.

[10]Arthur Keigle,Zhen Liu,Johannes Chius.优化的填充工艺降低成本[J].封装与测试.

[11]Min Miao,Yufeng Jin,Longguang liao,etc.Research on Deep RIE-based Through-Si-Via Micromachining for 3-D System-in-package Integration [C].Proceedings of the 2009 4th IEEE international Conference on Nano/Micro Engineered and Molecular Systems January5-8,2009.

[12]李佩,汪辉,周华.铜互连CMP碟形缺陷及铜残留的研究[EB/OL].工艺与制造,维普资讯, http://www.cqvip.com

[13]赵超荣,杜寰,刘梦新,韩郑生.Cu互连及其关键工艺技术研究现状[EB/OL].趋势与展望,维普资讯,http://www.cqvip.com

[14]Shari Farrens.晶片级键合技术最新发展[EB/OL].SUSS MicroTec.www.suss.com/tec_library

[15]Stefan Pargfrieder,Paul Kettner,Mark Privett,Jack Ting.Temporary Bonding and De-Bonding Enabling TSV Formation and 3D Integration for Ultra-thin Wafers [C].2008 10th Electronics Packaging Technology Conference.

[16]Shari Farrens.用于3D集成中的晶圆和芯片键合技术[J].电子工业专用设备,2010.

[17]By Silke H,Christiansen,Rajendra Singh,Ulrich Gosele.Wafer Direct Bonding:From Advanced Substrate Engineering to Future Applications in Micro/Nanoelectronics[J].Proceedings of the IEEE,2006,94(12).