有机封装基板的芯片埋置技术研究进展

2024-03-11杨昆朱家昌吉勇李轶楠李杨

杨昆,朱家昌,吉勇,李轶楠,李杨

(无锡中微高科电子有限公司,江苏无锡 214035)

0 引言

消费电子与移动通信产品朝着轻薄短小、多功能、高可靠度与低成本化的趋势发展,要求IC 具有更多的I/O 端口、更高的密度、更优异的电和热性能、更多的功能、更高的可靠性和性价比。为了应对这些挑战,芯片级封装(CSP)、系统级封装(SiP)、晶圆级封装(WLP)以及层叠封装(PoP)等新型封装技术得到了发展[1]。封装基板埋置技术也是为应对这一挑战而提出的解决方案之一,它将有源、无源元件埋入封装基板,充分利用基板内部空间,释放更多表面空间,是减小封装体积的一种重要途径,因此元件的内埋化成为重要的发展趋势[1-2]。

根据国际半导体技术路线图[3],基板内元件埋置技术可以看作SiP 的一种高级形式。相比于器件表面组装技术(SMT),基板内元件埋置技术的优势主要表现在可以缩短信号传输的路径,减少信号串扰、噪声和电磁干扰,提高信号的传输速度,同时还可以节省线路板的面积,减轻质量,提高产品的可靠性并降低制造成本,这些优势可以更好地满足电子产品的高频应用需求以及轻、薄、短、小等需求[1,4-5]。埋入无源元件的基板可以追溯到20 世纪70 年代开发的低温共烧陶瓷基板(LTCC),LTCC 技术可以将电感、电容等埋入基板,该技术发展成熟并进入了实用化,国内外已有较多相关研究介绍[6-8]。继陶瓷基板埋置技术之后,有机基板由于不用经历烧结的高温过程,除了可以埋置电容、电感等单一元件外,还可以埋置IC 元件、模组等复杂的有源器件,同时具有可大面积加工、厚度低等优势,已得到快速发展[1-2]。近年来,玻璃基板具有优异的机械、物理和光学特性,可以实现较好的表面平整度、尺寸稳定性,有望进一步提升封装的晶体管密度上限、降低功耗,因此受到越来越多的关注[9-11]。但是玻璃基板技术距离实现量产还需要一些时间,要替代有机基板还需要突破材料制备、成本及良率等问题,目前对玻璃基板芯片埋置技术的相关研究较少[12-13]。有机封装基板在过去几十年中一直是该行业的支柱,本文主要介绍有机封装基板的芯片埋置技术,相对于电容、电感等单一元件的埋置,在有机基板内进行芯片埋置的难度更高,需要更高的精度控制、外形尺寸控制,并需要解决产品集成度、散热设计优化及信号控制等一系列问题,同时要保证埋置基板的产品良率以减少芯片损失等,本文将详细介绍封装基板的芯片埋置工艺路线以及不同的芯片埋置基板技术典型案例。

1 芯片埋置技术工艺路线

根据芯片在封装基板制造过程中的埋置先后顺序,芯片埋置技术可简单地分为芯片前置与芯片后置2 种不同的工艺路线[5]。

1.1 芯片前置

芯片前置是指先放置芯片然后在其上构建互联的过程,早期GE 公司和Intel 公司、德国弗劳恩霍夫可靠性和微结构研究所(Fraunhofer IZM)等率先提出芯片前置技术并在该技术的研发上做了大量工作[14-16]。GE 公司是最早提出将芯片埋入基板的公司,是芯片埋置技术开发的先驱者。20 世纪90 年代,GE 公司基于芯片前置方案搭建了一种基于聚酰亚胺薄膜的镀铜埋置平台,并发展出一种电源覆盖工艺技术(POL)[14]。GE 公司的POL 工艺平台通过直接镀铜连接芯片取代了焊线连接,在降低寄生互联电感和热性能方面具有很好的优势,半导体管芯被夹在管芯两侧的Cu 层之间,可以提供双面散热通道和内部电磁干扰(EMI)屏蔽。GE 公司根据后续工艺步骤的不同在POL 工艺的基础上继续开发了ePOL、WPOL、POL-MCM、POL-kW等封装类型。

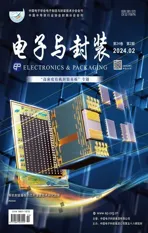

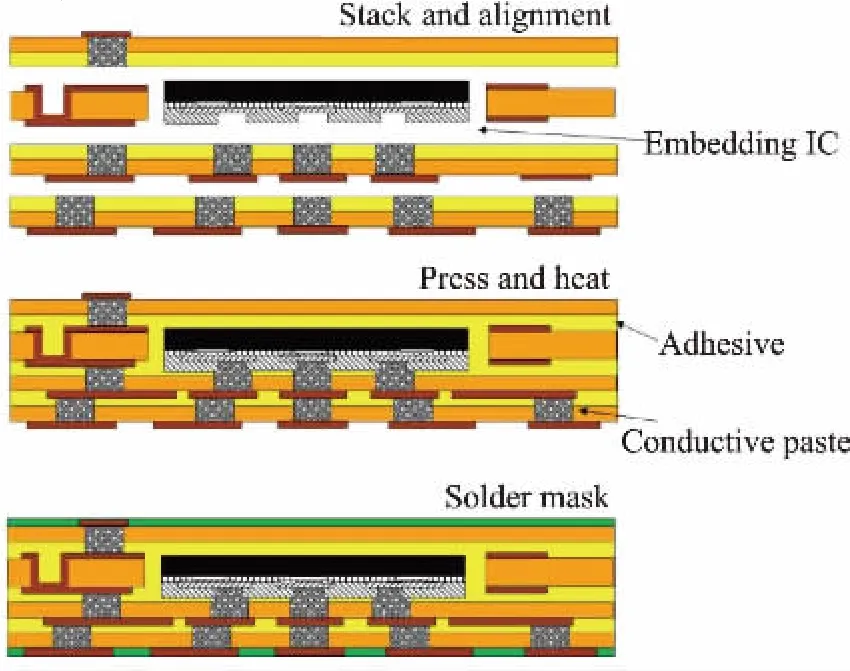

BOETTCHER 等[16]报道了一种具有2 层金属结构的层压封装埋置技术,其具体工艺流程如下。a)芯片贴装。将芯片通过装片胶或芯片黏接膜(DAF)贴装在载板上,在该步骤中,装片的精度至关重要,DAF 膜有更好的共面性,有利于对埋置后芯片上层树脂厚度的控制。b)涂树脂铜箔(RCC)层压。芯片贴装在载板上之后,用一块RCC 在真空条件下与芯片压合。c)激光钻孔。通过激光钻孔工艺使芯片PAD 露出,同时还可以在芯板上进行通孔加工;激光钻孔工艺中可以先采用UV 激光对表面铜层加工,后用CO2激光对树脂孔进行快速加工。d)金属化。金属化前需清理孔内及芯片PAD 上的树脂残渣、粗化孔壁,通过电镀铜工艺进行填孔电镀,实现芯片和外部电路连接。e)线路图案化。利用光刻等工艺实现外层线路图形化制作,最后进行阻焊层加工,进而完成基板的加工。该层压封装埋置技术工艺过程如图1 所示。

图1 层压封装埋置技术工艺过程[16]

相对于传统封装结构(芯片键合在基板上方),这种芯片前置埋置结构可以明显降低封装高度,同时芯片与基板直接金属连接的方式比引线键合、倒装焊连接方式的可靠性更高。当然,这种简单的埋置结构只适用于I/O 数量少的器件,同时芯片埋置加工也会带来额外的挑战,如芯片装片精度、层压时芯片移动以及树脂和芯片之间的热失配可能导致的分层开裂情况。

1.2 芯片后置

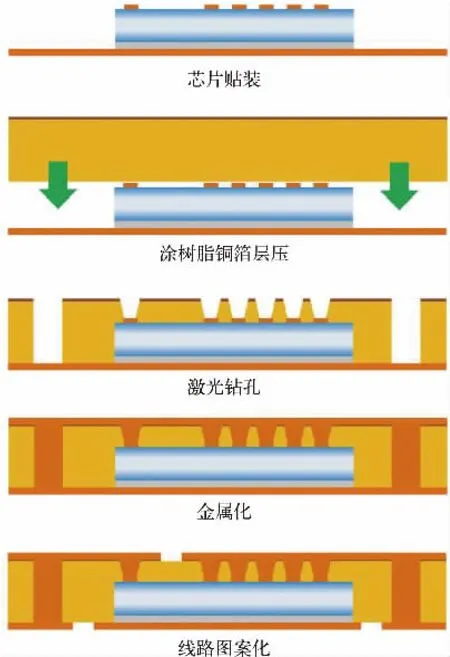

与芯片前置相对应,芯片后置是指先单独构建互联,然后将芯片装配在其顶部,率先对芯片后置技术进行开发的代表单位为乔治亚理工学院。乔治亚州理工学院于2010 年报道了一种采用有源和无源元件后置的新型有机基板埋置技术[5],在单颗封装体/模块中实现了多个有源和无源元件埋置,旨在满足高度集成系统的需求,该有机基板埋置结构如图2 所示。

图2 有机基板埋置结构[5]

该结构关键的工艺流程包括2 部分:一是构建空腔,在已知合格基板上通过等离子体、激光等技术在介质层中制造高精度空腔,清洁空腔以露出空腔内的细间距金属焊盘,采用化学镀镍浸金工艺对空腔内部和基板表面的焊盘进行保护;二是超细节距铜微凸点的芯片互联,该研究团队采用了一种新型铜微凸点低温键合工艺将硅芯片嵌入基板空腔。

相对于芯片前置技术,芯片后置的优势有很多,比如可通过不同深度的空腔实现对不同厚度或者不同材料的芯片进行埋置,可以很好地解决芯片前置技术中出现的芯片尺寸限制、层压芯片的位置稳定性问题;在埋置组装前选用已知合格芯片和预测试合格基板,可大大提升埋置基板的良率、产量,降低损失;可更容易实现返工、维修(如有必要);芯片后置的结构中芯片一般在基板最外层,更容易进行散热;工艺流程对基板加工的基础设施改动影响较小,并具有更快的交期、更短的上市时间等诸多优点[5]。

2 芯片埋置技术典型方案

经过多年的研究与发展,芯片埋置技术目前已经在封装基板市场占有一席之地,随着电子器件的小型化和高性能化,奥特斯(AT&S)、新光电气(Shinko Electric)、日月光(ASE)等公司在芯片埋置基板市场展开了激烈竞争。埋置基板产品由于自身的特殊性,在工艺技术上存在各种挑战,因此除了基板厂之外,封测厂、电子元件制造商以及专业的研发机构等也会针对不同产品直接开发相应的芯片埋置技术。

2.1 SESUB

SESUB 是TDK 公司独立开发的一种芯片埋置基板技术,该技术可实现无源和有源元件的垂直集成,并采用板级埋置加工工艺,对于SiP 模组来说是一个有吸引力的解决方案。

SIEROSHTAN 等[17]于2012 年报道了一款采用SESUB 技术加工的SiP 模组,SiP 模组样品截面如图3(a)所示,该SESUB 基板厚300 μm,包括4 层布线、3层介电层以及上下阻焊层,芯片嵌入在介电层Resin 2中,并与金属层Layer 3 连接。为了控制总厚度,埋置的芯片一般会被减薄到50~100 μm,同时嵌入的芯片可根据上下互联密度的不同选择“Face-up”或“Face-down”放置方式。芯片被埋置在基板的中间位置,采用激光开孔的方式使芯片焊盘露出,然后进行图形化以使芯片与基板连接,随后加工形成最终的基板。

图3 TDK 公司采用SESUB 技术加工的SiP 模组[17]

使用SESUB 技术前后具有相同功能的2 个SiP模组尺寸对比如图3(b)所示。很明显,采用SESUB 技术方案的模组面积几乎只有标准层压基板SiP 模组的一半。标准层压基板SiP 模组表面贴装的器件受限于表面尺寸,SESUB 技术由于可以将芯片埋置到有机基板内部,从而提高了集成度,同时小尺寸、低成本和快速上市等优势使采用SESUB 技术方案的SiP 产品更具有竞争力。目前SESUB 技术主要用于功能电路的微模块化,该技术特别适用于可穿戴设备、医疗设备或智慧家庭产品,其典型应用有智能手机的高性能电源管理单元(PMU)以及蓝牙模组等。

2.2 ChipsetT

ChipsetT 技术是由 FlipChip International 和Fujikura 公司于2011 年提出的柔性基板芯片埋置技术[18-19],该技术利用柔性聚酰亚胺层实现超薄封装,是一种SiP 解决方案,可以实现单个或多个芯片的埋置。

ChipsetT 工艺流程如下。

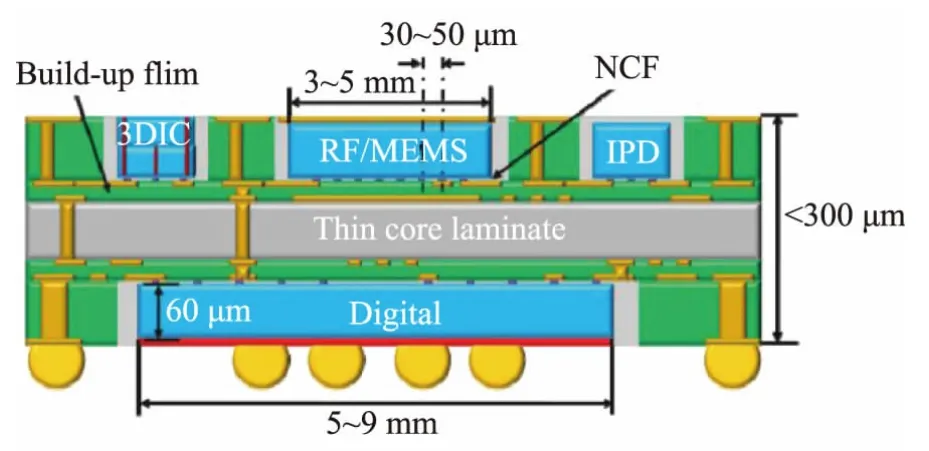

a)芯片埋置前加工。该技术在芯片埋置前需要利用重布线层(RDL)技术对芯片PAD 进行重新布局,重新布局后的芯片表面如图4 所示。

图4 重新布局后的芯片表面[19]

b)基板层压材料加工。采用柔性电路板工艺对每层单面覆铜板和双面覆铜板进行相应的线路加工、开孔、导电浆料填孔等工序,完成每层线路的加工,图5为基板层压材料加工示意图。

图5 基板层压材料加工示意图[19]

c)层压成型。采用共层压工艺将所有加工好的芯片、覆铜板材料按顺序堆层,然后加热、层压,在层压过程中导电浆料会烧结连接每层的线路和芯片的PAD,最后进行阻焊层加工、打标、切割等后端工序,完成基板加工,共层压工艺流程如图6 所示。

图6 共层压工艺流程[19]

ChipsetT 工艺具有诸多优势:有利于优化基板设计,芯片埋置前利用RDL 技术对芯片PAD 进行重新布局,可使基板有更好的布线间距及空间,在设计上具有很大的灵活性;层压前每层布线层和芯片都经过筛选,剔除不良,可以大幅度提升产品良率;可以适配成熟制程和大批量生产设备。这些优势可以保证ChipsetT 解决方案的成本效益,对于高度集成组件的应用来说是一个很好的解决方案。ChipsetT 技术主要瞄准智能手机、平板电脑、医疗诊断、汽车、安全、传感器和光伏等目标终端市场,可以为MEMS 模块、电源模块、控制模块等产品提供超薄和极低成本的芯片封装支持。

2.3 MCeP

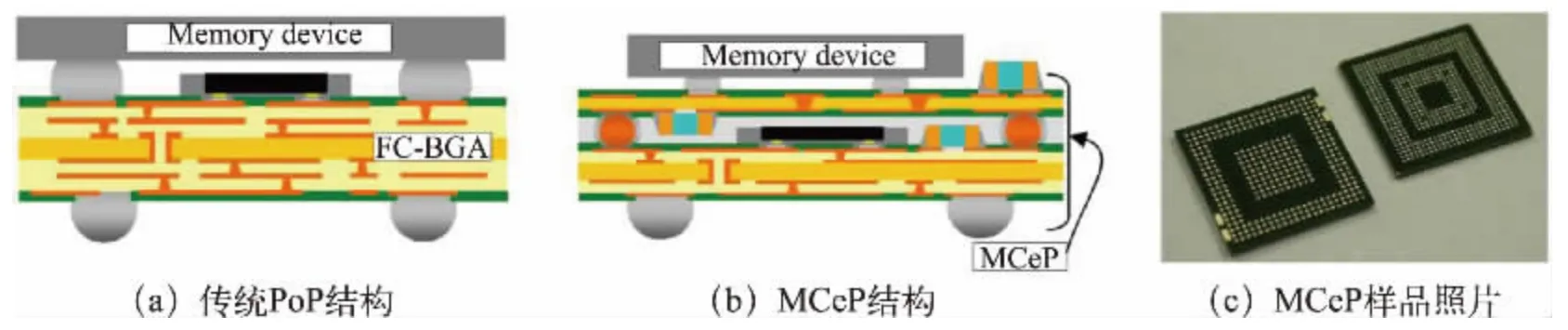

MCeP 技术是由Shinko Electric 公司于2008 年左右开发的一种埋置封装基板技术[20],该技术的开发旨在解决传统PoP 封装结构的一些问题。传统的PoP 结构如图7(a)所示,其底层封装形式通常是倒装芯片球栅阵列(FC-BGA)封装,上层通常是存储器件的封装。传统PoP 结构会存在一些问题,如封装翘曲较大,为了控制翘曲,封装时通常会使用更厚的基板,导致封装体的总高度明显增加。MCeP 由底部基板、上层基板和模封树脂组成,IC 和其他无源器件被埋置在上层基板和底部基板2 个基板内部,类似三明治结构,如图7(b)所示。正是由于其上层基板和底部基板形成的对称结构,MCeP 翘曲非常小,MCeP 样品如图7(c)所示[21]。

图7 传统PoP 结构、MCeP 结构与样品图[21]

MCeP 技术本质上是一种多基板组装工艺技术,整个MCeP 工艺流程均使用成熟的封装技术,因此具有高可靠性和高良率。MCeP 的工艺流程主要可分为以下几个部分:首先使用倒装焊将裸芯片安装在底部基板上;然后上层基板和底部基板通过铜核球进行焊接,采用铜核球主要是为了防止焊球塌陷,可以使上层基板和底部基板之间保持特定的距离,2 个基板之间的空隙采用模封树脂等进行填充;最后在底部基板进行植球,完成MCeP 封装基板结构。MCeP 用传统的组装工艺组装IC 芯片和有源/无源元件,结构稳定,在实现低翘曲的同时降低尺寸,封装体表面具有高设计灵活性,该技术主要应用于移动设备及AR/VR 的应用处理器、图像处理器、无人机应用处理器、物联网产品(如智能手表等)、天线组件、固态硬盘的内存控制器等多种类型产品。

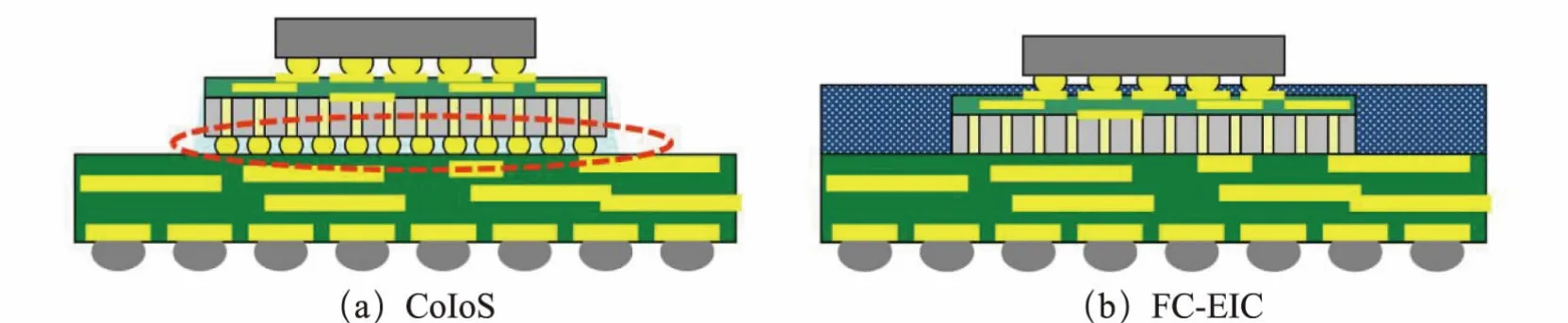

2.4 FC-EIC

CoIoS结构是一种基于硅中介层的封装结构,一般将芯片放置在包含RDL 布线层的硅中介层上实现高密度互联,硅中介层通过焊料与封装基板相连。FC-EIC是由Unimicron 公司于2013 年提出的一种封装基板技术[22]。CoIoS 与FC-EIC 结构如图8 所示。在FC-EIC 结构中,硅中介层埋置在了封装基板内形成EIC,芯片通过倒装的方式与EIC 互联。相对于CoIoS封装结构,FC-EIC 结构中的硅中介层与基板间的连接采用Cu-Cu 互连方式,减少了焊料的使用,可以实现更小的封装体积、更优异的电性能(较低的电阻和电感);FC-EIC 结构可采用更薄的硅中介层(30 μm/50 μm)埋入基板,更薄的硅中介层在孔加工和孔电镀时的难度及加工成本更低;另外,FC-EIC 结构中的硅中介层还可以用玻璃中介层进行替代,玻璃中介层具有更好的高频低损耗特性、更高平整度以及可调的热膨胀系数(CTE)[23]。

图8 CoIoS 与FC-EIC 结构[22]

EIC 的主要加工工艺流程如下:a)硅中介层临时键合,将经过RDL 加工的硅中介层临时键合在具有适当CTE 的硅片、玻璃或金属载体上;b)ABF 层压,采用ABF 膜将硅中介层覆盖层压;c)基板布线加工,通过激光钻孔在层压的ABF 膜上形成通孔,然后通过种子层、图形化、镀铜、去膜、刻蚀种子层等工艺实现线路加工,重复进行直到完成布线;d)阻焊层加工、解键合、切割等。EIC 的部分加工工艺流程如图9 所示,由于EIC 结构的不对称性,EIC 工艺面临的一个非常具有挑战性的问题是翘曲,可通过在压膜时选用具有不同CTE 的ABF 材料来控制翘曲。

图9 EIC 的部分加工工艺流程[22]

EIC 技术可以利用硅/玻璃中介层为多芯片集成提供SiP 平台,这种结构避免了中介层与基板间的焊料和底填胶的使用,可以使用板级工艺制造,在降低成本的同时兼具更薄的厚度,该封装结构在面向手机等移动终端产品时是更为有利的。

2.5 eHDF 与i-THOP

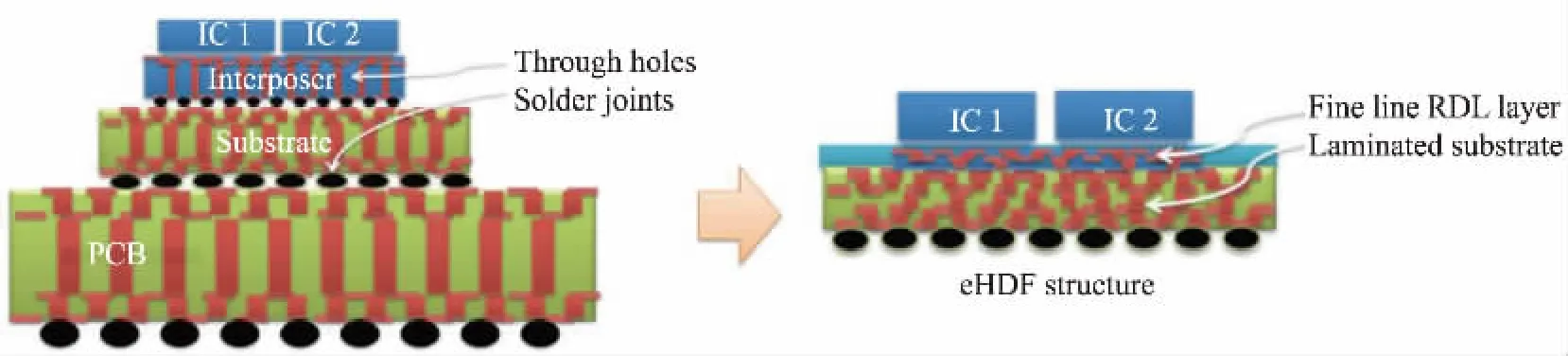

eHDF 与i-THOP 技术均属于无TXV 的高密度封装方案,主要是面对高性能计算(HPC)中的逻辑和高带宽存储器(HBM)接口互联需求不断增加而提出的解决方案。eHDF 是SiPlus 公司的一种新型无硅通孔(TSV)封装基板技术,该结构由HU 等[24]于2015 年提出,旨在满足异构集成、小尺寸、薄型化和低成本封装的要求,采用高密度膜(HDF)代替硅中介层直接与无芯基板相连。有硅中介层封装结构与eHDF 封装结构对比如图10 所示,相对于有硅中介层封装结构,eHDF基板可以减少焊接点、降低封装的高度及重量、降低整个系统组装和中间测试的成本。

图10 有硅中介层封装结构与eHDF 封装结构对比[24]

eHDF 基板的加工需要使用2 种工艺平台:半导体精细线路加工工艺平台和板级层压基板加工工艺平台。加工工艺流程如图11(a)~(c)所示,主要分2 个部分进行:一是通过半导体精细线加工技术在载体1的临时键合层顶部进行精细线路加工,一般通过3 层布线形成薄膜RDL1,完成薄膜RDL1 之后进行解键合、切割,形成RDL1 薄膜单元;二是将薄膜RDL1 重构,采用板级层压基板工艺将积层介电材料直接层压在薄膜RDL1 上进行后续RDL2 的线路加工。完成后的eHDF 基板可从载体2 上剥离,对焊盘进行表面金属化处理形成最终的eHDF 基板,如图11(d)所示。从eHDF 基板截面SEM 图可以看到eHDF 基板的双层结构,如图11(e)所示。

图11 eHDF 基板加工工艺流程及基板样品图片[25-26]

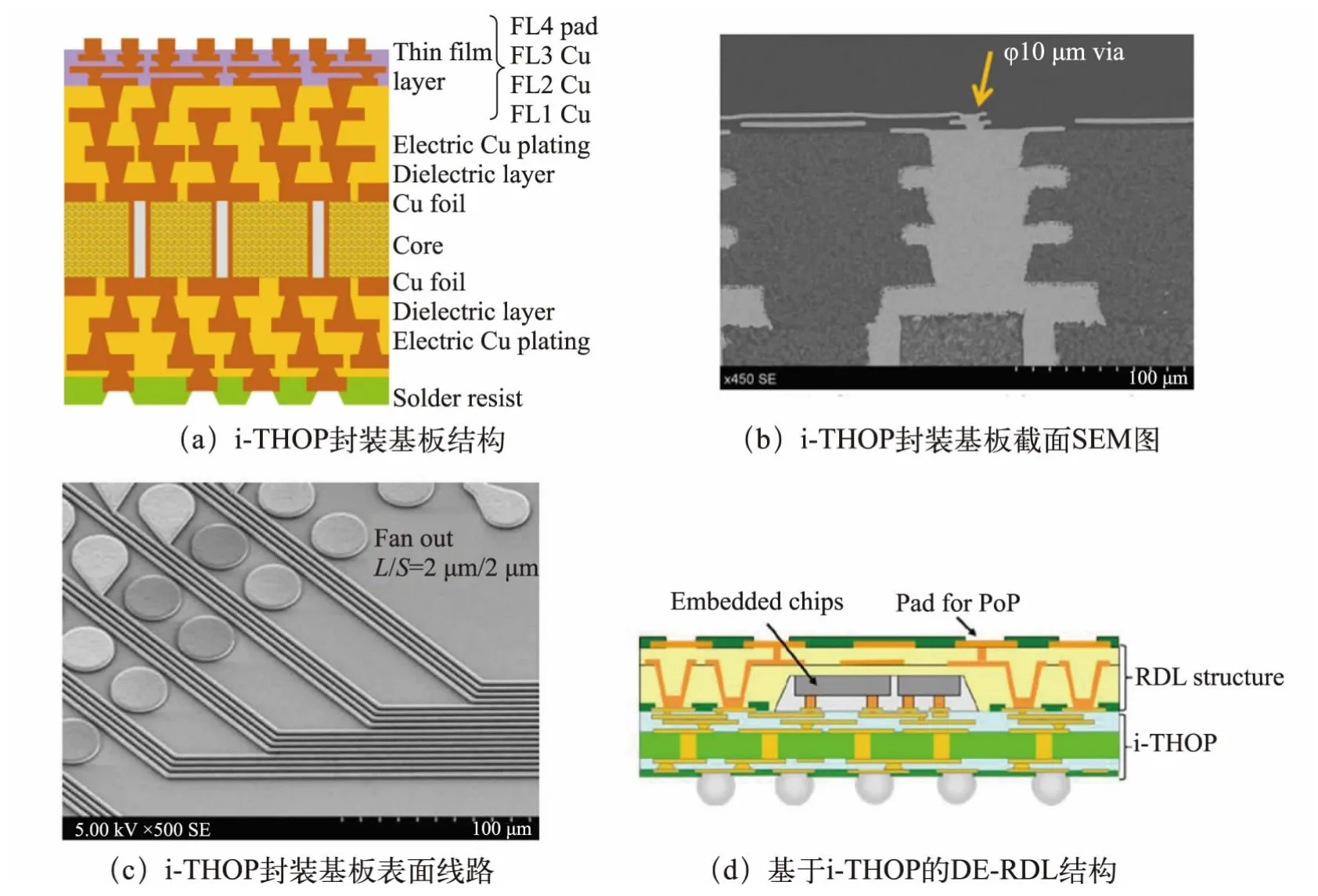

Shinko Electric 公司拥有类似的顶层细线路基板技术——i-THOP。SHIMIZU 等[27]于2013 年报道了在有芯基板的顶层表面进一步进行精细线路加工以实现基板表面芯片间高速互联,i-THOP 封装基板结构如图12(a)所示,由图12(b)(c)可知,过孔直径达10 μm,精细线路部分的最小线宽/线距L/S 达2 μm/2 μm。Shinko Electric 公司在i-THOP 技术基础上进一步提出的DE-RDL 结构如图12(d)所示,该技术将芯片嵌入到RDL 结构和基板之间,可用于移动设备中的应用处理器封装[28]。

图12 i-THOP 技术[27-28]

2.6 EMIB

嵌入式多芯片互联桥(EMIB)是由Intel 公司的MAHAJAN 等[29]于2008 年提出,并经过十余年开发、扩展,最后发展到实用化的技术[30-32]。EMIB 是一种先进、经济、高效的异构芯片高密度互联方法,该技术使用硅桥替代硅中介层用于芯片互联,实现芯片到芯片的高带宽、低延迟和低功率通信,为异构芯片集成应用开辟了新的道路。

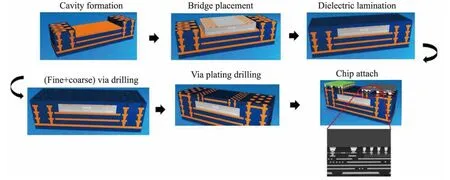

EMIB 技术通过增层技术将硅桥嵌入有机基板中,埋入基板内的硅桥通过顶部2 层叠孔并结合后道互联工艺实现与封装基板顶部倒装芯片焊盘相连。硅桥的埋入只提高了基板局部的布线密度,不会对其他芯片的封装、封装基板的整体结构造成影响。与CoWoS 等采用硅中介层的高密度多芯片封装技术相比,EMIB 技术无需使用TSV 技术即可实现多个芯片局部互联,不会对电信号传输路径产生不利的影响,其组装过程也比硅中介层的组装少一道焊接工序,具备一定的成本优势。因此,各大研究机构相继围绕硅桥探索其在高密度互联、异质集成方面的应用[33-36]。

EMIB 技术增加了封装基板制造的复杂性。EMIB基板加工的关键部分工艺流程如图13 所示,具体流程如下:a)在硅桥埋置前,有机基板可采用标准制造工艺流程进行加工,直到顶部最后2 层,随后为硅桥埋置创建一个独特的空腔;b)将硅桥通过DAF 膜固定在基板腔体铜箔上适当的位置并固化;c)使用薄膜型介电材料和薄膜层压技术在整个封装基板上层压树脂膜;d)在硅桥区域形成高精度的窄节距过孔,过孔需精准落在硅桥PAD 上,同时在基板其他非硅桥区域形成较大节距的过孔;e)采用电镀工艺对孔进行电镀填充以实现硅桥到基板的连接;f)通过布线、层压、钻孔、镀铜的方式制作顶部2 层互联结构和焊盘,完成整个基板加工。

图13 EMIB 基板加工的关键部分工艺流程[31]

硅桥采用FAB 后道工艺进行加工,硅桥减薄后的厚度小于75 μm,一般具有4 层金属布线和表面PAD层,金属布线层可用来实现信号或电源传输,金属布线层最小L/S 可达1 μm/1 μm[37]。

EMIB 技术中要实现硅桥的嵌入有很多加工上的困难和挑战[38],将硅桥准确、可靠地嵌入有机基板是EMIB 先进封装技术的核心,其中关键技术包括:1)硅桥键合前后的翘曲控制以及硅桥埋置后基板加工及封装工艺过程中用的介电材料,由于硅桥本身较薄,并且硅背面贴DAF 膜,两者CTE 不匹配,在不同的工艺条件下硅桥外形会发生变化,因此需要选择合适的DAF 材料和最佳的硅桥键合工艺条件,以控制硅桥外形变化;2)硅桥背面与空腔材料表面之间界面要求无空洞且具有一定的可靠性,界面空洞会增加硅桥分层风险以及化学品渗入风险,良好的界面还有助于减小硅桥加工过程中的移位。另外硅桥的嵌入位置精度以及过孔到硅桥PAD 的套刻对准精度等方面也存在着挑战,并直接关系到基板与硅桥的互联。

目前,EMIB 技术已被应用于Intel 公司的FPGA、GPU 以及人工智能、服务器芯片和其他以数据为中心的HPC 领域。

2.7 DBHi

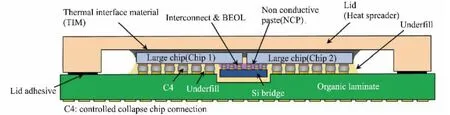

直接键合异质集成(DBHi)由IBM 于2018 年提出概念[39],与Intel 公司的EMIB 技术相似,DBHi 技术也是使用硅桥来实现异构芯片间的高带宽、低延迟和低功率通信,如CPU/GPU 和内存系统间的通信。典型的DBHi 封装结构如图14 所示[40-41]。

图14 典型的DBHi 封装结构[40]

整个DBHi 结构的封装过程如下。a)硅桥加工。硅桥进行减薄、划片加工,因为硅桥先要连接2 个主芯片,然后放置在基板的凹槽内,因此硅桥的强度和尺寸精度至关重要。b)芯片连接。采用热压键合技术(TCB)将图14 中主芯片Chip 1 与硅桥连接,键合过程中采用非导电芯片黏接胶(NCP)进行预填充,NCP材料在固化后可以很好地连接并固定主芯片Chip 1与硅桥形成的组件。然后采用TCB 技术将主芯片Chip 1 与主芯片Chip 2、硅桥形成的组件进行连接,每次键合后都需要进行NCP 固化。c)倒装底填。将形成的芯片组以表面贴装的方式与有机基板连接,然后用底填胶对芯片与基板缝隙以及硅桥下凹槽进行填充。一般凹槽底部仅靠底填胶的毛细作用很难完全填充,因此在固化时通过循环施加真空和压力的方式可以使底填胶进入凹槽并固定硅桥。d)散热片贴装。

DBHi 技术需要在基板表面加工凹槽用于芯片倒装时硅桥的埋置,封装基板凹槽一般要利用机械钻孔工艺在基板中心加工,在凹槽加工过程中要精确控制凹槽的深度,避免损失内部布线,同时需要关注基板的翘曲控制。从封装基板整体加工难易程度的角度来看,DBHi 技术中封装基板的加工难度相对于Intel 公司的EMIB 技术明显降低。

除上述介绍的封装基板芯片埋置技术之外,还有三星、AT&S 等公司或研究所开发的各种不同的芯片埋置技术[14,42-45]。AT&S 将其芯片埋置技术称为ECP 技术,并实现了ECP 技术的商业化,可用于汽车、通信、医疗和手机等领域,如可穿戴设备、MEMS、无线连接模块等便携电子设备和助听器等医疗产品;Schweizer公司是芯片埋置技术的早期进入者,其p2-PACK®工艺可以实现功率半导体的埋置,该工艺主要的应用领域在于直流电和交流电系统之间的转换,如逆变器、转换器、工业电机驱动和汽车应用产品等。

3 结束语

封装基板埋置技术的发展从陶瓷基板过渡到有机基板,从简单的电容、电感等简单元件埋入发展到多芯片、模组埋入,不断满足人们对新一代电子产品的需求。进入“后摩尔定律时代”,高端封装工艺迭代已成为新的发展趋势,异质集成正在重塑产业生态。有机封装基板芯片埋置技术正在从多芯片封装、SiP方向(如SESUB、eHDF 技术)逐步向高性能、超高密度互联接口的异质集成方向(如EMIB、DBHi 技术)发展,并成为异质集成技术的基础支撑和关键解决方案之一。

目前,随着大算力应用的迅猛发展,高性能计算、自动驾驶、人工智能、大数据等新兴应用需求开始逐渐取代手机/PC 成为新一轮半导体周期驱动力。有机基板的芯片埋置技术既可以提高芯片的集成度,又可以改善信号传输性能,为实现高集成度和高性能封装提供了有效解决方案。在高性能计算方面,有机基板的芯片埋置技术可以实现高密度芯片布局、互联和紧凑的封装结构,可提供更高的计算能力和更低的能耗,这对高性能计算应用来说至关重要;自动驾驶系统对实时数据处理和决策能力的要求极高,采用有机基板芯片埋置技术可以将传感器芯片和处理芯片紧密集成,提供更快的数据传输和更低的延迟,从而提高自动驾驶系统的响应速度和安全性。随着材料科学、制造工艺和封装设计的不断进步,有机基板芯片埋置技术将实现更高的集成度,从而提供更高的性能和更小的尺寸;通过优化芯片埋置结构和信号传输路径,实现更低能耗;通过优化材料和工艺实现更高的可靠性,满足长期稳定运行的应用需求。有机基板芯片埋置技术如EMIB 等有望为先进封装市场的新一轮成长提供动力,打开更广阔的发展空间。