一款基于45 nm SOI CMOS工艺的高功率二倍频器

2024-01-20陈奇超叶乔霞王梓任高海军

陈奇超,叶乔霞,张 超,王梓任,高海军

(杭州电子科技大学射频电路与系统教育部重点实验室,浙江 杭州 310018)

0 引 言

多年来,雷达应用的场景越来越广泛,信号源是雷达系统中的重要部分。而振荡器则是信号源的一部分。随着工作带宽的增加,具有较宽的调谐范围和较低相位噪声的压控振荡器越来越难实现。因此具有超带宽、高输出功率和有较好的基波抑制的倍频器可以大大降低前级压控振荡器的指标要求。

文献[1]采用了无源器件如肖特基二极管来实现较高的工作频率和良好的基波抑制,但是它需要更高的输入功率。文献[2]采用了分布式结构来实现宽带性能,但是分布式结构倍频器消耗了大量的直流功耗。文献[3]采用了Marchand巴伦来实现差分信号,虽然其幅度平衡和相位平衡较好,但是其转换增益为-10 dB,需要的输入功率高达11 dBm。相比较下,平衡push-push结构倍频器具有功耗低,对输入功率要求低等优势。从上述文献对比中可以看出倍频器需要在直流功耗、谐波抑制和转换增益上进行权衡,而且其巴伦的性能对于倍频器来说有着重大影响。

针对倍频增益较低,奇谐波抑制较差等问题。本文设计的倍频器采用了push-push结构,可以消除奇次谐波,避免了滤波器的使用。倍频器采用了巴伦来产生差分信号和实现阻抗变换,在巴伦中心抽头处,加电容使其交流接地、隔离直流。在其输入端加入二次谐波短路回路来提高倍频增益。

1 倍频器的设计

1.1 平衡Push-push设计

采用push-push结构的共源级倍频器原理图如图1所示,输入的单端信号通过变压器巴伦转换为差分信号,两个相位相差180°的信号分别输入到倍频管Q1、Q2。在Vg的偏置下,由于倍频管的非线性特性,MOS管漏端已经产生了各次谐波。理想情况下,两个MOS管各自产生的奇谐波信号相位相差180°,偶谐波信号相位相同。合成的信号中奇次谐波被相互抵消,偶次谐波加倍。

假设输入信号为Vin1=cos(ωt)和Vin2=cos(ωt+π),MOS管漏端电流是脉冲型余弦函数,对MOS管Q1、Q2漏端的电流进行Fourier展开得出:

(1)

式中,In是傅里叶系数,n是谐波次数,通过计算得到push-push倍频器输出电流为:

(2)

从理论上可以得出push-push倍频器对奇次谐波的抑制作用很好。但是实际上由于巴伦产生的并不是理想差分信号,有幅-相误差,奇次谐波不能完全被抵消。图1中变压器巴伦也充当着阻抗变换的作用,相比于基于传输线的马昌巴伦[3],有着更紧凑的版图面积。图中L1、C1、C2参与输入阻抗匹配。Cr、Lr组成的二次谐波短路回路常用于倍频器中,用来增大二次谐波功率。在本文中,电容Cg放在巴伦中心抽头处,使得交流接地。在不同频率下,通过对倍频器进行负载牵引,得到各个频率下牵引阻抗点,由L2、C3、C4组成的阻抗匹配网络,将阻抗值匹配至50 Ω。

图1 push-push结构二倍频器

1.2 晶体管尺寸和偏置点的选择

图2 MOS管电容

由于倍频器输入频率较低,往MOS管栅极看进去的阻抗虚部的绝对值非常大,并且还随着频率变化较大[4]。因此很难实现输入阻抗完全匹配。如图2,往MOS管栅极看进去,阻抗虚部主要由CGD、CGS组成(在漏源间的电容忽略不计)。偏置和尺寸决定了这些电容值。

当MOS管处于截止时,栅与源和漏之间的电容可以表示为:

CGS=CGD=WCOV

(3)

当MOS管在饱和区时,栅与源和漏之间的电容可以表示为:

(4)

CGD=WCOV

(5)

其中COV表示为单位宽度覆盖电容,COX为单位面积的栅氧化层电容,可见当忽略沟道调制效应和体效应时,可得出共源级电路输入阻抗的虚部为:

(6)

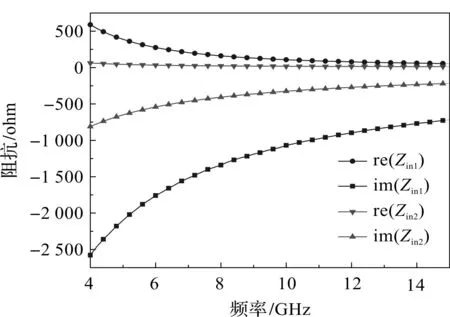

当MOS管在截止区时,相比于在饱和区,MOS管有更小的寄生电容。MOS管的输入阻抗主要由管子的栅长(L)和栅宽(W)决定。对push-push结构的倍频器进行S参数仿真,得到其输入阻抗随频率变化曲线如图3所示。

图3 push-push结构输入阻抗随频率变化曲线

图4 漏极电流形成电路图

图3中Zin1代表着2个MOS管并联时,MOS管的栅宽/栅长为10 μm/40 nm的输入阻抗,Zin2代表着2个MOS管并联时,MOS管的栅宽/栅长为40 μm/40 nm的输入阻抗。可见随着栅宽的增加,其阻抗将大幅降低。因此要想获得稍好的宽带匹配,就需要增大MOS管的尺寸。

如图4所示,当栅极交流信号的增大,MOS管从夹断区进入到饱和区,漏极电流Id1等于gmVgs。输入信号继续增大,MOS管进入三极管区。随着Vin1的减小,MOS管重新进入饱和区,进一步下降,MOS管进入夹断区。Id1>0的周期被定义为导通角(θ)[5-6]。漏极电流的谐波分量用θ可以表示为:

(7)

(8)

(9)

其中Imax为漏极电流峰值。如图5所示,各次谐波分量由Imax归一化可以看出:当导通角在90°时,二次谐波分量达到最大,奇次谐波最小。下面将分析MOS管尺寸对晶体管输出功率的影响。所仿真的是共源级电路,输入功率为0 dBm,频率为7.5 GHz,漏源电压为1 V,对MOS管的栅宽在12 μm至48 μm范围内扫描,得出不同栅宽下二次谐波输出功率和偏压的关系如下图6所示。

图5 谐波分量随漏端导通角变化曲线

图6 不同栅宽下输出功率随偏压变化

从图6可以看出,二次谐波输出功率随栅极偏压的增大呈现先增加后减小的趋势。当栅极偏压在0.1 V左右时,二次谐波功率达到最大。此时共源级电路产生了丰富的谐波,具有较大的效率和输出功率。当栅极偏压为1 V时,二次谐波很大是因为偏置点过高,直流功率很大。二次谐波输出功率随栅宽的增加而增加。但是在栅宽大于28 μm后,二次谐波功率增加缓慢。结合阻抗分析来看,增大栅宽有利于输入阻抗的匹配,因此倍频管选为2个40 μm×40 nm的MOS管并联。

1.3 二次谐波短路回路

参考图2,MOS管产生的二次谐波通过Cgd和Cgs分压反馈至栅极。这种反馈导致二次谐波电压在栅极摆动。二次谐波通过MOS管后,其漏极会产生新的二次谐波电流,但是新产生的二次谐波电流与原电流相差180°。因此,总的二次谐波输出电流会减小[7-8]。

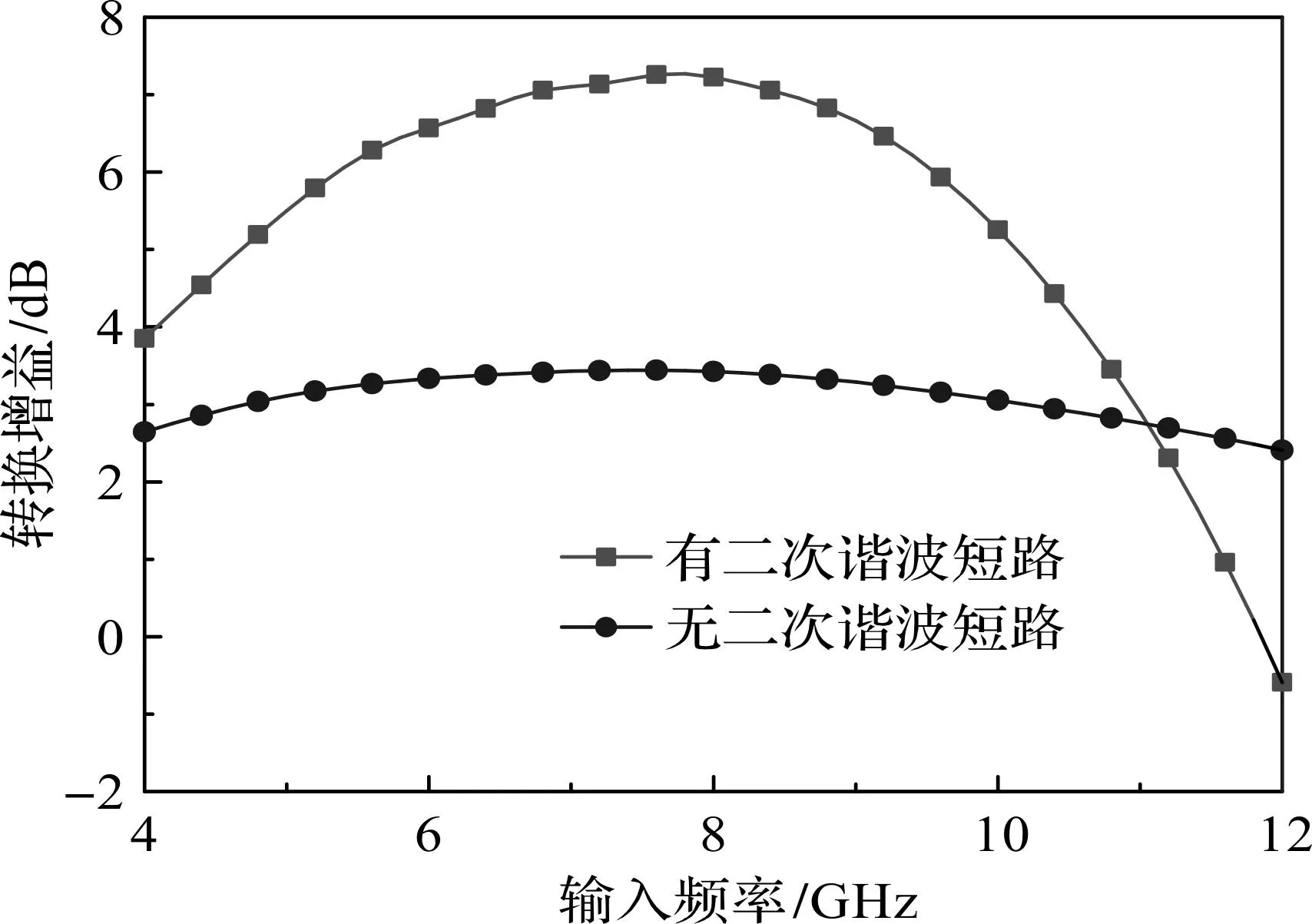

二次谐波短路回路原理图如图7所示。二次谐波短路回路电感可以等效成两个感值为2Lr的电感并联。假设在单点频率下,二次谐波短路回路两端主要考虑两种信号:一种是基波信号,输入信号经过巴伦后相位相差180°。另一种是通过栅漏电容泄漏的二次谐波信号,其相位相同。在二次谐波短路回路两端,相位相反的基波信号分别通过两个容值为Cr的电容以后,相互抵消,两个电容中心处相当于交流接地。二次谐波通过电容,无法抵消,分别通过两个等效值为2Lr的电感。二次谐波短路回路就可以等效成两个由容值为Cr的电容和感值为2Lr的电感组成的串联谐振网络。串联谐振网络谐振在二次谐波频率处。对于二次谐波来说,其阻抗值接近于0,从而滤除在栅极处的二次谐波。加入二次谐波短路回路后,二倍频器的输入阻抗变化如图8所示,二倍频器转换增益变化如图9所示。

图7 二次谐波短路回路原理图

图8 T谐振网络对输入阻抗的影响

图9 二次谐波短路回路的影响

从图8中可以看出,在输入基波信号下,加入二次谐波短路回路后,倍频器栅极相当于并联了电容,所以倍频器输入阻抗会沿导纳圆顺时针方向旋转。从图9中可以看出,在输入频率5 GHz~10 GHz范围内,有二次谐波短路回路比没有二次谐波短路回路的输出功率高了2.029 dBm以上。二倍频器输出功率得到了较大的提高。

1.4 巴伦的设计

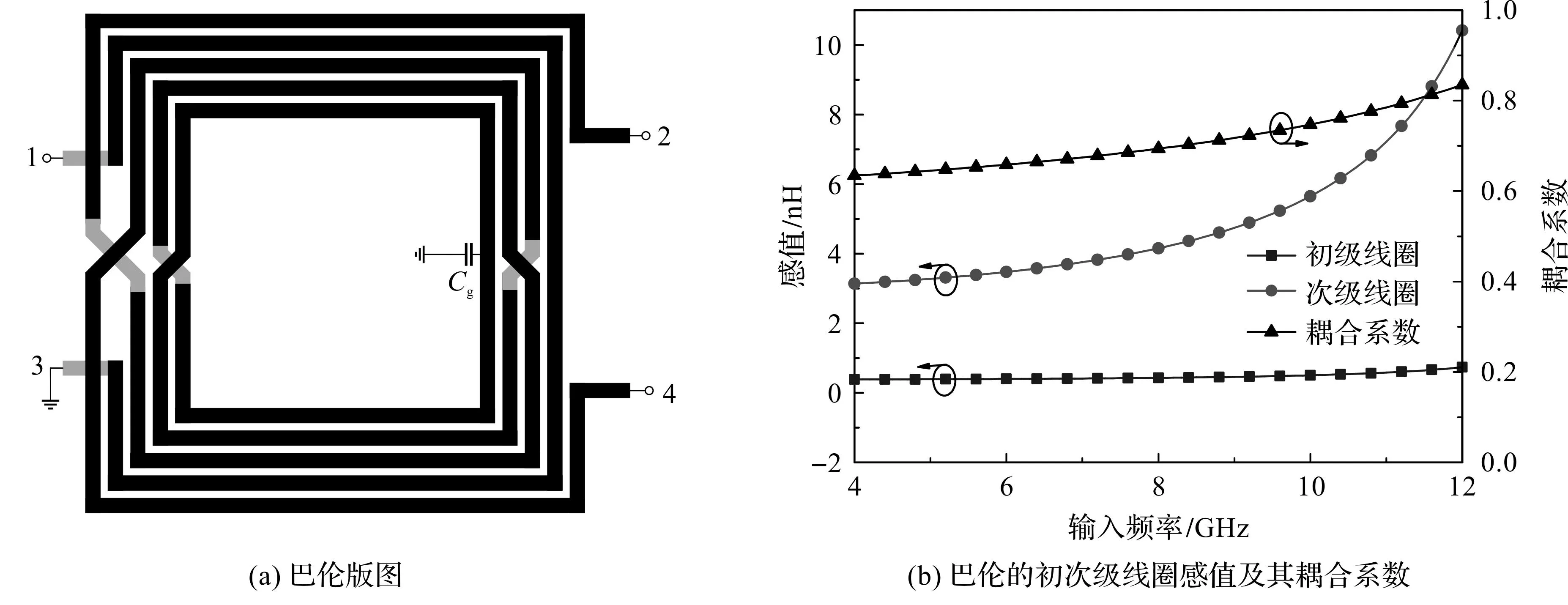

对于push-push倍频器,差分输入信号之间的幅度和相位不平衡会增加基频的输出功率,因为漏极电流中的奇谐波成分不能完全抵消。而差分信号正是由巴伦产生,因此输入差动端口的不平衡影响了倍频器的转换增益和奇次谐波抑制。根据晶体管输入阻抗,本文选用了1∶4的巴伦和一个π型匹配网络来进行阻抗匹配。结合巴伦自身损耗,用巴伦阻抗匹配至较小阻抗值,再将此阻抗通过π型网络匹配至50 Ω。本文设计的巴伦结构参数如表1所示,版图结构如图10(a)所示。该巴伦使用了中心抽头电容方案[9]匹配和平衡信号的产生。巴伦初、次级线圈及其耦合系数如图10(b)所示。

表1 巴伦结构参数

图10 本文设计的巴伦

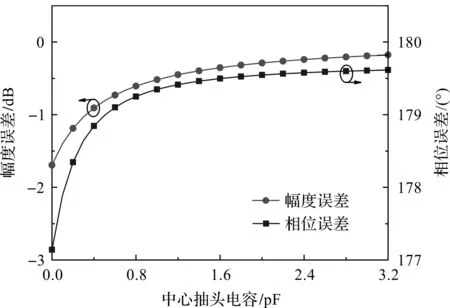

图10(a)中Cg为中心抽头电容。中心抽头电容不影响奇模信号,会改变偶模信号。也就是说会影响巴伦幅-相特性。在频率为7.5 GHz时,通过扫描中心抽头电容容值,得出其对巴伦幅-相特性影响如图11所示。可以看出中心抽头电容小于2 pF时,对巴伦幅-相特性影响很大,之后幅-相特性趋于平缓。带2 pF中心抽头电容的巴伦经过电磁仿真以后,其幅-相误差、S21、S31随输入频率变化曲线如图12所示。

图11 中心抽头电容的影响

图12 巴伦S参数和幅-相特性

从图12中可以看出,巴伦的幅度和相位误差各自稳定在-0.5 dB和-0.5°以内。在5 GHz~10 GHz范围内,S21、S31均在-7.15 dB~-10.22 dB范围内。

2 版图与后仿真结果

2.1 倍频器版图

图13 芯片版图

二倍频器采用GLOBAL FOUNDRIES 公司 45nm SOI CMOS工艺,一共有M1、M2、M3、C1、UA、OA、OB、LD八层金属层。馈电网络将M1至OA层通过通孔相连接,作为地层,将OB层作为电源层。地层和电源层由金属网格组成,布局在倍频器电路四周。OB、LD金属层较厚,具有较低的损耗,也用来设计电感、巴伦或长距离信号线。M1至M3层金属层损耗较大,故只用作MOS管自身连线。本设计只有VDD作为供电电压,并且与OB层相连接,MOS管栅极偏置电压由VDD通过电阻分压完成,漏极供电电压直接由VDD进行供电。本文设计的二倍频器通过cadence virtuoso进行仿真。由于面积的限制,版图并没有做保护环。其巴伦、线、电感之间的耦合已通过EMX进行电磁仿真。将画好的整体版图中的有源器件和电阻去除后通过EMX进行电磁仿真,生成的symbol导入原理图后将有源器件和电阻连接在一起仿真。二倍频器核心版图面积为660 μm×399 μm,如图13所示。

2.2 倍频器后仿真结果

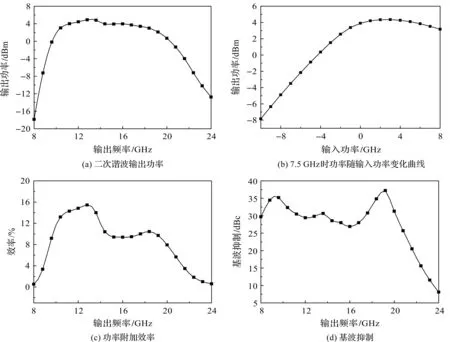

当输入功率为0 dBm时,得到二次谐波输出功率如图14(a)所示,在10 GHz~20 GHz范围内均达到了0 dBm以上。3 dB带宽范围为10.04 GHz~19.26 GHz,相对带宽为62.9%。图14(b)显示了在输入信号频率为7.5 GHz时,二倍频饱和输出功率为4.3 dBm。图14(c)显示了倍频器效率随输出频率变化曲线,可见二倍频峰值效率达到了15.45%。基波抑制是倍频器相对重要的指标,其好坏决定着波形纯度。图14(d)显示了基波抑制随输入频率变化曲线,在3 dB带宽内,基波抑制大于27 dBc。

图14 二倍频器性能

为了验证本文所设计的二倍频器的性能优势,将设计结果与文献所发表的二倍频电路作比较,如表2所列。

表2 不同设计方法的倍频器文献对比

文献[2]使用分布式技术,但其最大转换增益只有-3 dB,而且可在表中直接看出,分布式倍频器耗费了大量的直流功耗和有较大的面积换取了较大的带宽。文献[7]使用了具有二次谐波短路回路的push-push结构倍频器,它的最大转换增益达到了4.5 dB,但其带宽与本文相比略窄。文献[9]使用了push-push结构,但它的最大转换增益只有-2.5 dB。本文在push-push倍频管前加入了二次谐波短路回路后,最大转换增益达到了4.9 dB,在同类倍频器中有比较大的优势。在3 dB带宽内,其基波抑制大于27 dBc,好于文献中的二倍频器。文献[10]是基于混合正交耦合器的倍频器,最大转换增益也只有-1.6 dB。

3 结束语

本文采用45 nm SOI CMOS工艺,设计了一款基于push-push结构的高功率二倍频器。该倍频器采用了二次谐波短路回路,来滤除栅级的二次谐波,显著地提高了二次谐波输出功率。但是变压器巴伦损耗比较大,降低了倍频器的输出功率。设计出低损耗和较小幅度、相位误差的巴伦是本设计下一步优化的重点。