国产EDA平台下化合物半导体工艺PDK的开发研究

2024-01-20贾古凯陈展飞

贾古凯,游 彬,陈展飞

(杭州电子科技大学浙江省大规模集成电路设计重点实验室,浙江 杭州 310018)

0 引 言

随着5G时代大功率场景应用需求的提高,化合物半导体(GaAs、GaN、InP等)射频功率器件显露出明显优势,而芯片的成功设计也必须依靠贯穿于IC设计、制造、封装等环节的EDA工具。在全球EDA产业中,海外三巨头Synopsys、Cadence、Siemens EDA处于领先地位。国产EDA产业起步晚、历经波折,如今也出现了一些优秀的EDA厂商,其中华大九天(Empyrean)是本土领域的龙头企业。目前,国际贸易环境复杂多变,西方国家通过对我国实施EDA工具的禁用来限制我国集成电路产业的发展,因此迫切需要尽快实现国产EDA工具的替代[1-2]。

化合物半导体产业的快速发展,使得射频集成电路的设计日益复杂。如何减轻射频集成电路(RFIC)设计的难度和缩短RFIC设计周期,是EDA厂商、晶圆代工厂、IC设计公司和IC用户的共同目标[3-4],快速开发国产EDA平台配套工艺设计组件(Process Design Kit,PDK)可以解决此问题。它是联结晶圆代工厂、IC设计公司和EDA厂商之间的纽带,允许IC设计公司使用特定工艺实现电路需求并完成电路设计。PDK可以描述半导体工艺的器件性能,实现EDA工具/半导体工艺/RFIC设计环境之间的相互集成。业界常用的PDK绝大部分基于国外EDA平台,事实上,PDK的概念最初也是由Cadence公司提出,并在其设计平台Virtuoso上使用Skill语言实现[5],此外还有部分基于Keysight公司ADS平台[6]和基于Synopsys公司Laker平台[7]下的PDK等。但是,基于国产EDA平台下的PDK开发研究发展还很欠缺。不仅如此,目前大多代工厂会根据一套成熟的半导体工艺提供不同EDA工具下的PDK供客户使用,其中鲜有国产EDA工具下PDK的存在。

EDA的发展是制约我国集成电路产业的卡脖子问题,而PDK是使用EDA工具进行电路设计的基础条件。缺少PDK的使用,集成电路设计会受到严重的限制。目前,基于国产EDA平台下PDK的发展主要存在以下问题:(1)学术界对其研究较少,多数是针对于Cadence工具下PDK[8-9]的研究。(2)由于国外EDA工具下PDK是基于其平台脚本语言开发的,不具有可移植性和互操作性,如:Virtuoso下的PDK由Skill语言开发[10],ADS下的PDK由AEL语言开发[11]等。(3)不同EDA工具下的PDK架构与文件目录也不同[11]。所以,无法使用国外PDK在国产EDA工具下进行电路设计。因此,非常有必要尽快提出一种适用于国产EDA工具下的PDK架构和开发方法。

针对上述问题,基于国产EDA龙头厂商(Empyrean AetherMW)平台,研究了PDK的开发方法和PDK架构,提出了适用于该国产EDA平台的整套PDK开发流程,详细说明PDK开发中的难点,提出相应的解决方案。并使用该开发方法,根据0.15 μm GaAs pHEMT化合物半导体工艺完成了其全部器件库的开发,包括高电子迁移率晶体管、电感、电容、电阻、微带线、PAD和背孔等。

1 PDK的功能与组成部分

PDK在形式上是多种文件的集合,包含完整的器件库、模型库和半导体工艺文件,可以辅助电路设计师完成设计;PDK中包含的器件的符号、参数、电路仿真信息、器件模型文件,可以用于电路仿真;PDK包含的参数化版图单元(Pcell)可以减少版图设计过程中的任务量,通过对器件尺寸相关参数的设定,能够得到符合代工厂生产要求的版图结构;PDK中的物理验证文件可用来做后端验证,保证版图设计的准确性。

一套成熟可靠的PDK应包含以下组成部分[12-13]:

(1)Library:库是PDK的整体,包括电路设计时用到的所有器件信息。

(2)Symbol:原理图设计符号由器件的特性进行定义,通常会在符号中标识一些关键的表征器件特性的参数,如HEMT器件中的栅长(Gate Length,L)、栅宽(Gate Width,GW)、栅指数(Number of Finger,NF)等,方便电路设计者使用。

(3)CDF(Component Description Format):组件描述格式用来描述该器件的所有特征信息,定义了器件类型、器件名称、器件参数的属性和默认值、控制参数的显示/编辑状态、是否执行Callback函数等。

(4)Callback:参数回调用于表征CDF参数之间的函数关系(计算、数值范围限制等)。

(5)Spectre/hspiceD View:用来支持电路设计中的仿真需求、实现和不同EDA仿真工具之间的交互接口。用于产生仿真相关的参数,如:器件模型名称、器件端口信息、模型参数信息等。

(6)SPICE Model:器件模型是工艺器件性能的数学表征,是电路仿真的重要基础,模型文件包括物理参数和曲线拟合参数,利用数学方程、等效电路及工艺数据拟合等方法对器件电流-电压等关系进行精确描述,实现电路的精确模拟。

(7)Pcell(Parameteried cell):参数化单元是PDK中的核心部分,由特定编程语言编写生成的参数化版图单元可以实现原理图驱动版图的设计流程,在调用Pcell时定义器件的结构和尺寸参数值,就可以自动生成相应尺寸的器件版图结构,可以显著提高RFIC的版图设计效率。

(8)TechFile(Technology File):技术文件用来描述工艺特点,也是参数化版图的必需文件,包含GDSII的设计数据和工艺层的连接关系、映射关系、属性定义、在线设计规则、电气规则、显示色彩定义和图形的形状定义等。

(9)PV Rule(Physical Verification Rule):物理验证包括DRC/LVS/PEX等规则文件。设计规则检查(Design Rule Check,DRC):版图布局受基本规则的控制,Foundry无法实现违反设计规则的版图制造;原理图版图一致性检查(Layout Versus Schematic,LVS):确保电路版图与原理图设计相匹配,识别版图中器件之间的连接关系是否符合设计预期;寄生参数提取(Parasitic Extraction,PEX):提取RFIC设计中的寄生分布网络参数。

(10)Manual:包括设计规则手册、模型手册、PDK使用手册等。

2 基于国产EDA平台的PDK开发

为了实现国产EDA工具下PDK的使用以及在各EDA工具之间的互操作性,提出一种新的PDK开发方法,即使用开源的Tcl和Python语言进行PDK的开发:其中CDF参数由图形化编辑器(GTE)实现,Callback由Tcl语言实现,Layout由Python语言实现。该方法可以容易地对PDK进行维护和更新,缩短了开发周期,还可以使用较少的编码实现功能更复杂的参数化版图单元,并且符合开放数据库(OA)和互操作PDK库的标准,适配于多种基于开放数据库标准的EDA平台。

2.1 基于国产EDA工具下PDK开发方法

开发方法如图1所示,首先创建PDK所必需的库文件,根据该化合物半导体工艺特征依次创建器件的视图(原理图视图symbol view、仿真视图spectre view)、CDF参数属性、仿真信息等,确保Callback逻辑正确,并且能正确调用模型文件进行仿真后,去编写后端设计部分(包括技术文件和参数化版图单元的开发),再根据正确的版图结构和工艺需求编写验证规则文件,完成对PDK的质量检查(Qualification Assurance,QA)之后即可释放PDK。

使用本文所提出的PDK开发方式并基于0.15 μm GaAs pHEMT工艺,在华大九天EDA工具AetherMW平台上实现了PDK全套开发流程。

2.2 基于国产EDA工具下PDK开发难点及解决方案

Pcell和设计规则检查文件(DRC)是PDK中的关键部分,国产PDK下可将Pcell分为两部分,分别是CDF和参数化版图单元,下面分别对以上三部分的开发难点进行描述并提出合适的解决方案。

(1)CDF、Callback的开发

图2 ePDK(Empyrean PDK)中CDF/Callback开发方法

目前业界通用的PDK开发方法中,所有组成部分均由编程语言实现,当代工厂的半导体工艺更新后,PDK也要随之更新,这样工程师就必须面对大量的代码修改任务,无疑增加了PDK的维护难度。对此,提出一种新的CDF/Callback开发方式,即使用GTE方式开发CDF和器件的仿真信息与使用编程语言开发Callback函数相结合。开发方法如图2所示,首先使用图形化界面编辑各器件的CDF参数,可以轻松地设置参数的属性,如,默认值、描述、是否可编辑/显示、是否调用Callback函数、字符类型等,使用GTE方式而无需调用编程语言即可将参数属性信息以文档形式保存到PDK中;Callback函数通过Tcl语言表达式实现,在参数更改时进行计算并触发CDF参数回调,其变化值会被Callback函数文件所获取,并执行相应逻辑操作,在开发的过程中,根据Debug窗口判断代码逻辑是否正确,同时显示出错误信息。

(2)Pcell的开发

在集成电路的后端设计中,工程师会花费大量的精力绘制版图结构,但使用PDK中的参数化版图单元可以避免重复劳动。参数化版图单元必须由脚本语言进行编译,并在布局中被实例化。开发参数化版图结构是一项复杂的编码任务,PDK开发工程师需要大量的时间去实现。因此开发的难点在于如何使用少量易读的代码去实现复杂的版图结构。

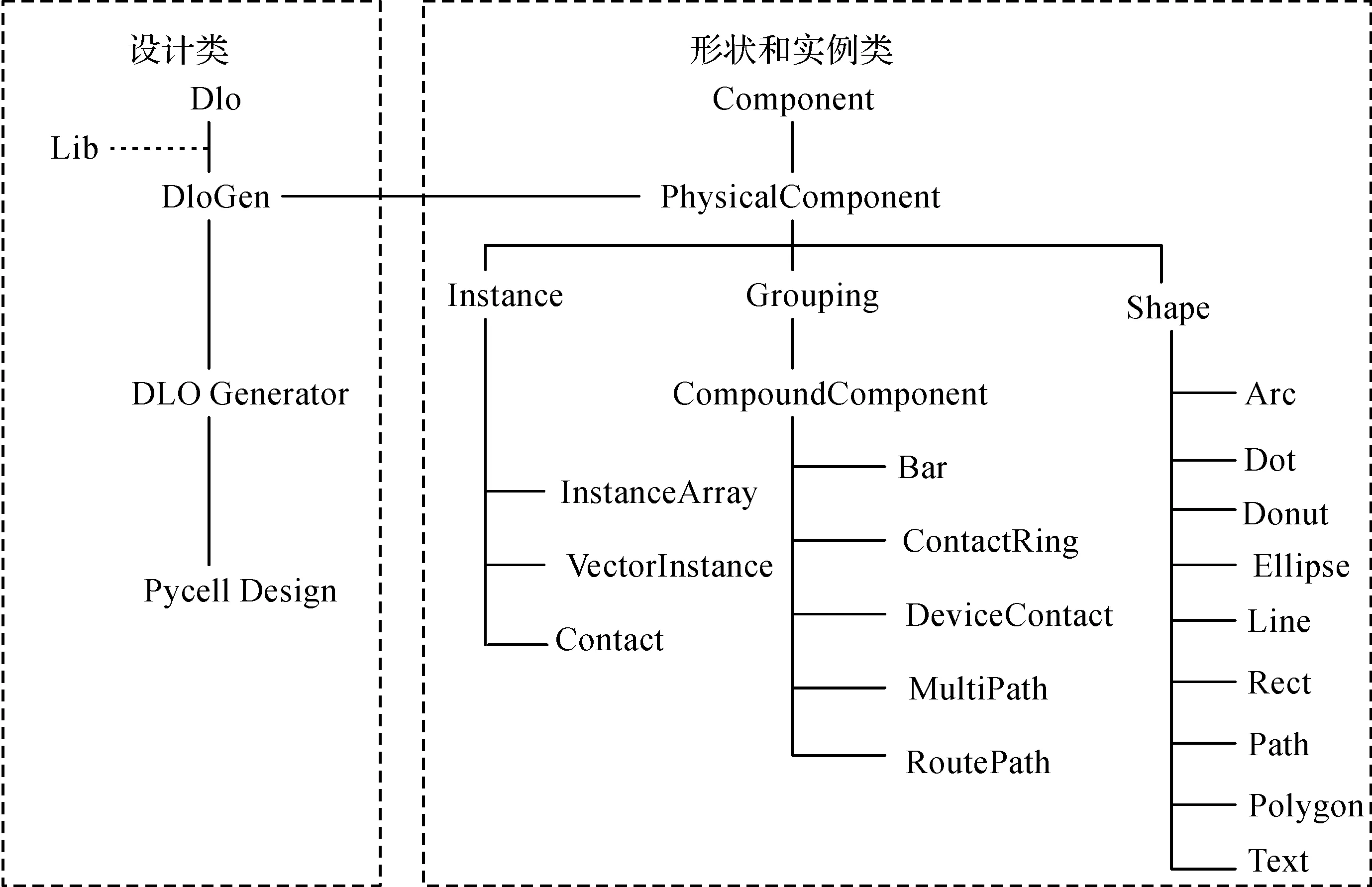

由于Python语言具有语法简单、开源、具有众多的标准库和第三方库、可扩展性强等优点,故提出使用Python语言实现国产EDA平台下参数化单元的开发。根据化合物半导体工艺实际需求,在PBQ中使用Python对版图结构进行代码编写,图3为Pcell code的基本结构,调用AetherMW观察版图的实现效果。当Pcell被成功编译后,它就会以Python程序的形式存储在OA数据库中,每次调用版图时,特征参数就会被赋予默认值或指定值,并在布局设计环境中执行绘图操作,简化了参数化版图几何结构的创建工作。

图3 Pcell code基本结构

(3)DRC的开发与QA

DRC基本规则包括工艺层/派生层的宽度(Width)、长度(Length)、面积(Area)、间距(Spacing)、跨越(Straddle)、重叠(Overlap)、包含(Enclose)等,首先需要完成DRC标题栏和规格模块,用于包含规则文件的说明、版本信息以及验证工具运行检查的方式;之后完成各工艺层的操作模块,用于将版图设计中的工艺层映射到规则文件中以及指定由工艺层之间运算产生的派生层;最后便是器件的连接和提取模块,用于定义工艺层之间的连接方式和版图网表的提取。

语法格式如下,以关键字Rule为开始:

Rule ISO_01 {

;(ISO.01) Minimum space -- 4.0um

space( ISO <4 adjacent <90 point_touch region ) }

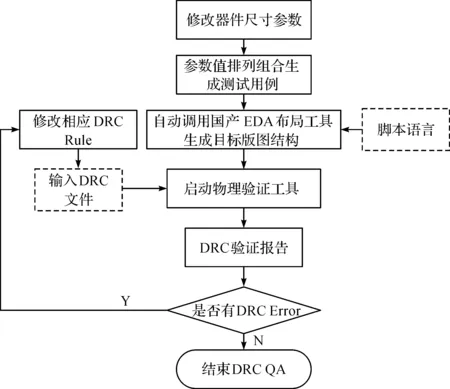

随着器件特征尺寸不断缩小,设计规则检查的内容也逐渐复杂,对每条规则分别进行QA显然是不可取的。提出一种新的DRC QA方法,可以较轻松地对DRC文件进行检查修改,方法如图4所示,通过修改器件版图尺寸相关的参数生成一组测试用例,如:

topCell, mline_verify

Cells, Device_mline

param,W,10u,20u,30u,35u

param,L,115u,124u,150u,160u

参数值之间排列组合可以生成16个pattern,由脚本语言编程自动调用布图工具并依据参数值生成16种器件的版图结构,再由这些版图结合物理验证工具去验证DRC文件的正确性,修改错误规则直至没有DRC错误产生。

图4 DRC QA方法

3 PDK的实现与验证

3.1 国产EDA平台下PDK的实现

开发完成的ePDK由多组文件夹和文件集合而组成,表1为本次所开发的0.15μm GaAs pHEMT ePDK的主要内容。相对于使用Skill语言开发的cPDK(Cadence PDK),该方式不仅开发简单,还大大降低了后续PDK维护和版本迭代的任务量,也弥补了国产EDA平台下PDK的空白。

表1 ePDK架构

通过本文所提出的开发方法,完成了0.15μm GaAs pHEMT工艺中所有器件的开发,包括HEMT、HEMT_BV、Diode、MIM_Cap、Round_Ind、Square_Ind、TFR_Res、ISO_Res、TLine、Step_Line、Cross_Line、Curve_Line、Taper_Line、Tee_Line、PAD、Bvia等。

3.2 PDK验证

为了证明使用本文所提出的开发方式所开发PDK具有正确性和实用性,需要对该PDK的内容进行仿真验证,确保其可以在国产EDA工具中(华大九天AetherMW)完成射频集成电路仿真设计。

(1)使用PDK中的耗尽型HEMT器件进行直流和S参数仿真。图5(a)表征该器件的直流特性,参数设置为NF=2,GW=25 μm;仿真条件为VGS:-1.5~0 V,步长为0.1 V;VDS:0~6 V,步长为0.1 V。图5(b)表征该器件的射频特性,参数设置为NF=6,GW=25 μm;仿真条件为Freq:0.2~50 G,步长为0.2 G;VGS:-1.5~0 V,步长为0.1 V;VDS:0~6 V,步长为2 V。将仿真结果与器件测试数据进行对比(蓝色线为仿真结果,红色线为器件实测数据),可以看出仿真与测试结果误差较小,符合电路设计要求。

图5 HEMT仿真与测试结果对比

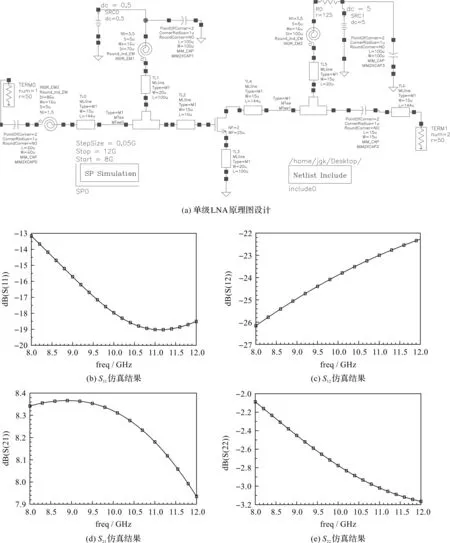

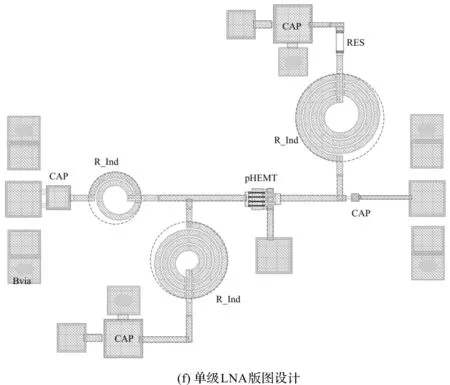

(2)在AetherMW中使用该PDK中的部分器件设计单级低噪声放大电路。图6(a)为原理图设计;S参数仿真结果如图6(b-e)所示,横坐标为扫描频率,纵坐标为用dB形式表示的S参数,其中S11/S22分别表示输入/输出回波损耗,S21表示增益和平坦度,S12表示隔离度;由图可得,使用本次开发的PDK所设计的电路在X波段具有良好的输入回波损耗,增益平坦度正负0.2 dB;根据电路原理图,调用参数化版图单元完成版图绘制,如图6(f)所示,并且已经通过了PDK中DRC文件检查。

图6 单级LNA电路设计与仿真

以上验证结果表明,基于国产EDA平台开发的化合物半导体工艺PDK可在华大九天AetherMW软件中正常使用,满足电路需求,支持射频集成电路的设计。

4 结束语

本文提出了一种适用于国产EDA工具下PDK的开发方式和结构,并以华大九天EDA工具为平台实现了某化合物半导体工艺PDK的全套开发流程,详细分析了国产PDK开发设计中的难点,提出解决方案。与传统的PDK开发方式相比,本文提出的方法具有可移植性、代码简单、便于更新维护且开发周期短等特点。最后验证该PDK的正确性,将其应用于实际电路,结果表明具有一定的可靠性,可以在国产EDA平台下完成射频集成电路的设计。后续将完成国产EDA下其它化合物半导体工艺PDK的开发设计。