基于基板塑封工艺的小型化宽带电调衰减器

2023-11-13贾玉伟唐中强蔡道民薛梅李展

贾玉伟,唐中强,蔡道民,薛梅,李展

(中国电子科技集团公司第十三研究所,石家庄 050051)

1 引言

自动增益控制(AGC)电路是一种闭环负反馈电路,它可以依据接收信号幅度的大小实现对通道增益的自动控制,保证输出功率在预设范围以内。AGC 电路一般应用于接收机的中间级,通过AGC 电路实现接收机放大系数的自动调整。在接收机灵敏度处于一定范围内的前提下,输出信号幅度保持在一个合理的范围内[1-2]。

电调衰减器是AGC 电路的核心器件。它可以根据微波信号的预设值,实现对信号衰减的精确控制,从而给后级电路提供合适的输入信号。同时其具有一定程度的插入损耗,应用到阻抗失配的电路之间可以抵消部分阻抗变化的影响。电调衰减器具有广泛的应用场景,比如应用在功率传输控制、信号电平幅度调整、辐射干扰抵消等系统中。

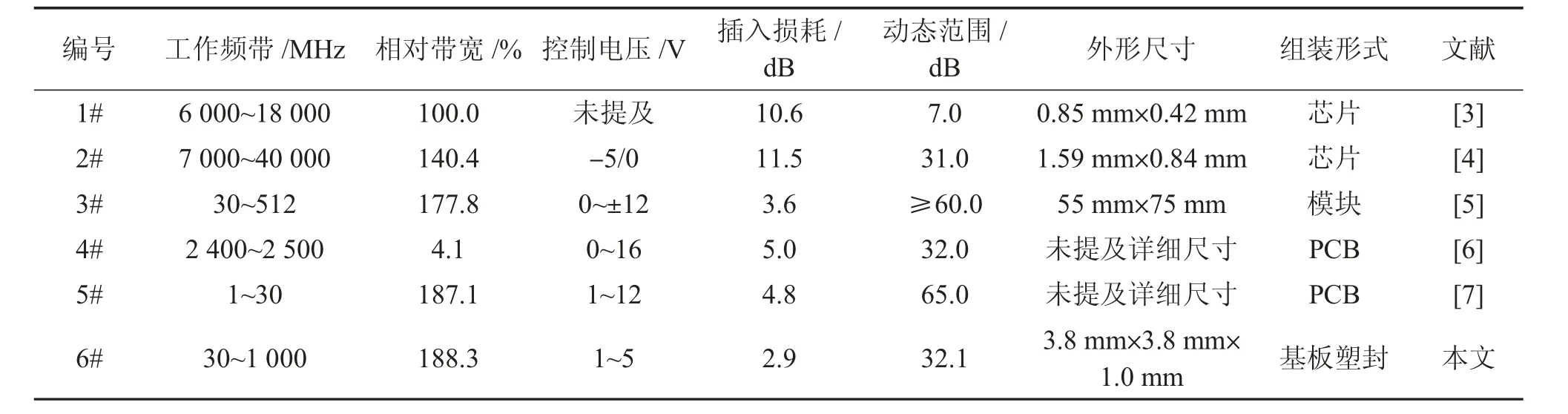

文献[3] 提出采用八边形锗硅P 型-本征-N 型(PIN)二极管,设计并实现了一款宽带衰减器芯片。该芯片的工作频带为6~18 GHz,衰减器的动态范围为7 dB,在工作频率为6 GHz、12 GHz、18 GHz 时的插入损耗分别为7.9 dB、9.4 dB、10.6 dB。该芯片的尺寸为0.85 mm×0.42 mm。文献[4]提出采用InGaAs PIN 二极管,设计并实现了一款宽带衰减器芯片,该芯片的工作频带为7~40 GHz,衰减器的插入损耗不大于11.5 dB,该芯片的尺寸为1.59 mm×0.84 mm。文献[5]提出采用双极性结构实现了一个适用于米波、分米波波段的电调衰减器,其工作频带为30~512 MHz,衰减动态范围超过60 dB,将衰减器电路封装于金属壳体内,其封装外形尺寸为55 mm×75 mm,控制电压为0~±12 V。文献[6]提出了一款调谐电压为0~16 V、衰减变化量为32 dB 的电调衰减器。由于PIN 二极管具有电流与电阻成反比的特点,文献[7]提出了一种工作频带为1~30 MHz、衰减动态范围为65 dB 的衰减网络,且在整个衰减范围内,衰减平坦度可以达到0.5 dB。

微波单片电路形式的电调衰减器优点为尺寸小,但一般适用于在微波频段工作,在甚高频(VHF)频段的低端(约为30 MHz)工作时性能差,同时片上一般无法集成隔直电容。采用PCB 形式或金属盒体制作的电路模块形式的电调衰减器可在VHF 频段的低端工作,且射频端口可集成隔直电容,但由于受分立元件的寄生参数影响,这类衰减器的工作频带宽度受限,同时其外形尺寸较大(厘米量级)导致集成度不高。因此,既可在VHF 频段的低端工作又能满足PCB 表贴应用的小型化宽带电调衰减器具有研发价值。

本文从基板小型化和元器件小型化着手,采用对称式Π 型衰减网络,基于基板塑封工艺研制了一种可工作于VHF 频段、可满足PCB 表贴应用的小型化宽带电调衰减器。

2 电路结构与工作原理

电调衰减器的电路主要由衰减网络和偏置网络构成。常用的衰减网络结构主要有Π 型、T 型、桥T 型3 种。这3 种结构各有优缺点:T 型衰减网络可以实现较大的衰减动态范围,能承受功率容量较大,但是其端口发射系数差,端口不易匹配;Π 型衰减网络的带内相对平坦,且端口易于匹配,但是功率容量较低;桥T 型衰减网络可以实现较低的插入损耗,端口易于匹配,但是却对二极管的功率容量性能要求极高,且两级级联后优点不突出。针对本文选用的Π 型衰减网络,设系统的特征阻抗为Z0,衰减网络的衰减量为A,Π 型衰减网络中并联电阻为R1、R2,串联电阻为R3,考虑R1=R2的同阻模式,则R1、R2、R3的计算方式如式(1)(2)所示[10-11]。各类衰减网络的衰减值与电阻值的关系可参考文献[8-9]。

在衰减网络中加入可变电阻元件,就可以控制衰减值。目前可用的元件主要是场效应晶体管(FET)和PIN 二极管。相比于GaAs FET,PIN 二极管是一种电流控制器件,具有承受功率大、导通插入损耗低、寄生参数小的特点。PIN 二极管的电性能特点为:当直流信号使其反偏时,PIN 二极管的等效电阻极大,等效于断路;当直流信号使其正偏时,其等效电阻较小,且随着输入电流的变化而变化,即等效电阻随着偏置电流而变化。由于以上特性,PIN 二极管被广泛应用于射频开关、衰减器和限幅器[8]。因此,本文选用PIN 二极管进行方案设计。

电调衰减器的主要技术指标包括最小衰减量(也称为零态插入损耗)、最大衰减量、端口回波损耗(或驻波比)等。衰减动态范围是指最大衰减量和最小衰减量之差。电调衰减器一般要求插入损耗小、衰减动态范围大、驻波比小、衰减线性度高[10]。

本文设计的衰减器工作频带为30~1 000 MHz,其相对带宽较宽。根据前文所述各类衰减网络的优缺点,本文设计的衰减器电路选择Π 型PIN 二极管衰减网络结构。通常情况下,Π 型衰减网络包含3 个PIN 二极管,这种网络在结构上不具备对称性,从而使得偏置电路较为复杂,不利于器件的小型化。为解决此结构的缺点,本文优化设计了Π 型衰减网络。即在原电路结构的串联支路上增加一个反向二极管,使电路结构具有对称性。改进后的衰减网络具备如下3 个优势:1)在直通链路中,使用了两个串联PIN 二极管,使衰减量增加了一倍;2)直通链路中的两个PIN 二极管是反接的,其在工作过程中,偶数阶的非线性分量将会大大减少,从而提升了频谱纯净度;3)改进后的衰减网络采用完全的中间对称结构,可以大大简化器件的偏置电路[11-12]。

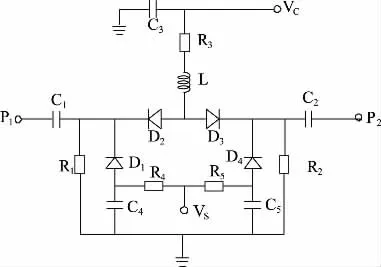

该衰减器电路将偏置网络、隔直电容与衰减网络组合在一起。图1 为电调衰减器的电路原理图。

图1 电调衰减器的电路原理图

衰减网络由D1、D2、D3、D44 个二极管芯片组成,D2、D3为串联结构,D1、D4为并联结构。偏置网络由电阻R1、R2、R3、R4、R5、电感L、滤波电容C3组成。其中电感L 主要起射频扼流作用,抑制射频信号从加电端口泄漏。将电容C3设计在控制电压端口,使其并联到地,该电容在控制电压端口起滤波作用,以减少供电电源上的纹波、噪声及杂波对器件的干扰。隔直电容有4 个,分别为C1、C2、C4、C5,可实现“隔直通交”的功能。

P1、P2端口为射频信号输入、输出端口。由于电路采用对称设计,P1、P2端口可互易。VS端口为电源端口,VC端口为控制电压端口,R1、R2、R3、R4、R5共5 个电阻与电源端口、控制电压端口、地共同形成加电回路,为4 个二极管芯片提供偏置电压。在VS端口施加固定的正电压V1,在VC端口施加可调电压V2。当V2>V1时,D2、D3正向偏置,D1、D4反向偏置;当V2<V1时,D2、D3反向偏置,D1、D4正向偏置。通过合理地设计网络中的电阻,可以实现预期的电调衰减功能。

3 元件初值计算与基板设计

3.1 元件初值计算

PIN 二极管的截止频率fc=1/ (2πτ),τ 为载流子的最小渡越时间。当电调衰减器的工作频率远高于fc时,即工作频率不小于10fc时,PIN 二极管可用作可控纯电阻[13]。为了得到较宽的频带,应尽量选用fc较低的PIN 二极管。本设计选用国产某型号PIN 二极管,其I层厚度为50 μm,τ 为1 400 ns,计算得到其fc为114 kHz,理论上可用于工作频率大于1 MHz 的电调衰减器。

电感和电容主要考虑器件工作时的最低工作频率。根据电容的容抗公式计算电容值C[14],容抗公式为

其中,f 为器件的最低工作频率,XC为器件所需的最小容抗。

根据电感的感抗公式计算得到器件的电感值L[14]。电感的感抗公式为

其中,XL为器件所需的最小感抗。

经过计算和仿真,为使器件的最低工作频率可达30 MHz,同时兼顾器件小型化的需求,将电容值设计为4700 pF,电感值设计为1.0 μH。

电阻值可影响器件的插入损耗、衰减动态范围和端口反射系数。通过设计软件的参数调谐功能可以取得电路中各个元件的初值,设定设计目标进行优化,最终得到各个元件的设计值。在VS端口施加正电压为2.7 V,器件在5.0 V 偏置时处于最小衰减状态,在1.0 V 偏置时处于最大衰减状态。由于采用了对称的电路结构,两个射频端口的回波损耗理论上应当相同。

3.2 基板的设计

本文设计选用的是树脂基板,需要关注的材料参数主要有基板厚度H、基板材料的介电常数Dk和介质损耗Df等。器件射频端口匹配到50 Ω 的阻抗系统。

为了提高封装的集成度,实现器件的小型化,主要采用两项措施。一是选用小尺寸的元件,选用裸芯片形式的二极管,其芯片尺寸为500 μm×500 μm,电阻和电容采用0201 封装尺寸,电感采用0402 封装尺寸。二是采用4 层基板,利用多层布线实现基板小型化,基板的叠层结构参数如表1 所示。为了实现信号的最优传输,基板各信号线层从上至下分别为射频信号线层(顶层)、射频地线层(中间层1)、电源信号线层(中间层2)、引出端口层(底层)。基板的总厚度H 为358 μm,其中顶层与中间层1 之间的介质层厚度H1为80 μm,正面布版射频线需要按50 Ω 的阻抗进行设计。将介质层厚度H1(80 μm)、基板介电常数Dk(4.5)、特征阻抗Z0(50 Ω)和工作中心频率f0(500 MHz)等参数代入微带线阻抗计算软件进行计算,可得50 Ω 阻抗的微带线宽度为136 μm。其余走线按电路原理图布置,完成偏置网络的互联,层间通过过孔连通。

表1 基板的叠层结构参数

在基板底层设计各引出端口,中间设计大面积覆铜用于射频和直流接地。在器件背面通过在覆铜板上切45°斜角的方式提供方向识别标识。由于该器件预定在电路板上焊接使用,在各引出端口表面镀镍钯金。同时,为降低组装时出现焊接短路的风险,在背面非焊接部位涂覆阻焊材料。

4 工艺流程及测试结果

器件的组装采用混合集成工艺和注塑封装工艺。组装时的基板为阵列拼版形式。采用自动回流焊机将电阻、电容、电感焊接在基板上。PIN 二极管芯片的正面凸点为阳极,背面区域为阴极,将芯片背面通过导电胶粘接/烧结到基板上,通过金丝键合将阳极连接到电路的网络中,采用注塑封装工艺进行器件封装。

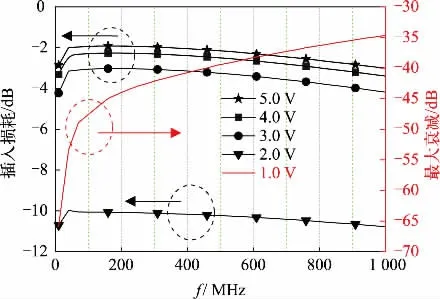

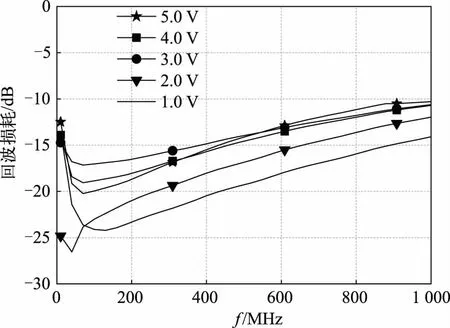

利用自动化测试程序,调节控制电压为1.0~5.0 V,以1.0 V 为升压级差进行测试,衰减器的插入损耗连续可控,表明衰减器的电调功能正常。不同偏置条件下插入损耗和最大衰减的测试曲线如图2所示。回波损耗的测试曲线如图3 所示。图3 中测试曲线的控制电压升压级差设为1.0 V。所研制的电调衰减器的外形尺寸为3.8 mm×3.8 mm×1.0 mm。使用电子秤测量,单只器件的质量约为38 mg。

图2 插入损耗和最大衰减的测试曲线

图3 回波损耗的测试曲线

从图2 可以看出,所研制的电调衰减器在30~1 000 MHz 工作频带内的插入损耗随控制电压变化。控制电压为5.0 V 时插入损耗绝对值最小,控制电压为1.0 V 时产生最大衰减。当控制电压为5.0 V 时,插入损耗绝对值小于2.9 dB,最大衰减绝对值大于35.0 dB,衰减动态范围大于32.1 dB。实测性能随频率升高而下降,插入损耗绝对值的带内平坦度约为1.0 dB。从图3 可以看出,在工作频带内回波损耗小于-10 dB。这主要由以下因素造成:1)自谐振频率效应电感L 的射频扼流效果随频率升高而下降;2)二极管管芯阳极焊点的尺寸较小,只能在其上键合一根直径为25 μm 的金丝,且由于布局原因,键合线的长度大于500 μm,键合线引入的寄生参数影响随频率升高而增大。本文设计的电调衰减器与相似产品的性能对比如表2 所示。

表2 本文设计的电调衰减器与相似产品的性能对比

本文设计的6# 电调衰减器的相对带宽达到188.3%,略高于3#和5#电调衰减器的相对带宽,显著高于1#、2#、4#电调衰减器的相对带宽。3#电调衰减器采用双极性控制,4#、5#电调衰减器采用单极性控制,控制电压分别为0~16 V、1~12 V。6#电调衰减器采用单极性控制,最高控制电压仅为5 V,因此,其控制更加简单方便。1#、2#电调衰减器的封装形式为高频率宽带芯片形式,6#电调衰减器可工作于VHF 频段。6#电调衰减器的插入损耗比1#低7.7 dB,比2#低8.6 dB。在3#、4#、5#电调衰减器中,插入损耗最低的为3#。6#电调衰减器的插入损耗比3#电调衰减器低0.7 dB,具有低插损的优势。

4#、5#电调衰减器的组装形式均为PCB 形式,所设计的电调衰减器作为部件装入组件中。与3#、4#、5#电调衰减器相比,本文设计的电调衰减器在小型化、高集成方面优势明显。

综上,与相似产品对比,本文设计的电调衰减器具有外围加电易、控制电压低、工作频带宽、外形尺寸小等特点,在自动化生产及实际应用方面具有更明显的优势。

5 结论

本文采用PIN 二极管芯片作为可变电阻元件的对称式4 元件Π 型衰减网络,选用4 层树脂基板,实现了一种小型化宽带电调衰减器。该电调衰减器采用2.7 V 电源供电,采用1.0~5.0 V 控制电压。测试结果表明,在工作频带为30~1 000 MHz 时,最小插入损耗绝对值小于2.9 dB,最大衰减绝对值大于35.0 dB,回波损耗小于-10 dB。该设计满足宽频带、低插损的要求,具有小型化、高集成、轻量化的特点,在AGC 等电路中有广泛的应用前景。