用于X波段相控阵系统的高线性度低附加相移数字衰减器设计

2017-04-24汪粲星万川川

邓 青,汪粲星,万川川,张 浩

(南京电子技术研究所,江苏南京 210039)

用于X波段相控阵系统的高线性度低附加相移数字衰减器设计

邓 青,汪粲星,万川川,张 浩

(南京电子技术研究所,江苏南京 210039)

设计了一款应用于X波段相控阵系统的6位数字衰减器,该衰减器具有高线性度和低附加相移的特点。对常规开关Pi型衰减器的附加相移和线性度进行了分析,通过电感和电容补偿技术,实现了在宽带频率范围和不同衰减状态下都具有低的附加相移。此外,利用浮动衬底技术来实现较高的线性度。该衰减器基于0.13μm的BiCMOS工艺设计。仿真结果显示该衰减器的插入损耗为6.67 dB,10 GHz下在最小衰减和最大衰减处的1 dB压缩点输入功率分别为15.5 dBm和10 dBm。

X波段;衰减器;相位校正;高线性度;相控阵;TSV;BiCMOS

1 引言

衰减器是现代通信系统和雷达系统的关键部件之一,广泛应用于自动控制环路、调制器和相控阵系统中[1]。在相控阵系统中,衰减器在不同衰减状态下必须具有非常低的相位误差[2]。此外,到达衰减器处的信号通常非常大,因此衰减器必须具有足够高的线性度来处理大信号[3]。

大多数数字衰减器基于两种基础的拓扑结构:Pi型衰减器和T型衰减器,由开关和电阻组成,因此衰减器的性能高度依赖于开关性能[4,5]。由于微波频率下晶体管的开关性能很差,开关难以通过标准的CMOS工艺实现。电路中的开关主要是由III-V族半导体器件构成,例如具有低导通电阻和截止电容的GaAs HEMT或PIN二极管。但是GaAs工艺产量低,需要外部控制电路,并且价格昂贵。

2 电路设计

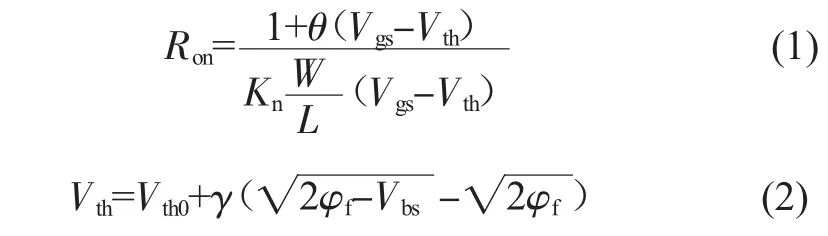

本文采用的衰减器的结构如图1所示。6位数字衰减器采用了电感和电容补偿结构,具有31.5 dB的高衰减范围,衰减步径为0.5 dB,由0.13 μm的BiCMOS工艺制备。0.5 dB衰减器采用T型网络,其他衰减器采用Pi型网络。16 dB衰减器由两个8 dB衰减器串联级联,可在最大衰减状态下获得良好的线性度。在每两级衰减器之间,使用小值电感来谐振寄生电容以获得良好的端口阻抗匹配,进而实现良好的幅度步进误差。电感和电容补偿也用于实现低相位误差和低幅度步进误差。从负载效应和功率处理能力两方面考虑,来选择适当比特排序以获得最佳性能。

图1 衰减器的结构示意图

通过高值电阻对开关的栅极和衬底施加偏压。该结构在RF频率下呈现高阻抗,并且开关的栅极和衬底的输入电压由单个MOSFET的漏极和源极电压控制,可获得良好的功率处理能力和高线性度[6]。

2.1 幅度和相位补偿

图2是Pi型衰减器的拓扑结构及其等效电路。从图2(a)可以看出,MOSFET是数字步进衰减器的关键元件。为简化分析,开关模型可以由如图2(b)和图2(c)所示的导通电阻Ron和截止电容Coff近似,该模型忽略了体寄生电容和串联寄生电感。从图2(c)可以看出,输入信号可以直接通过Coff输出,这可能导致衰减不够。为了增大高频下的衰减,增加了与电阻Rp并联的电容Cp,当频率增加时,并联阻抗变小,从而补偿衰减值。

图2 Pi型衰减器的拓扑结构及其等效电路

从图2可以看出,截止状态的传输函数为高通特性,导致衰减态的相位比参考相位超前。为了压缩该相,并联了一个低通特性电路。因此,电路中增加了改变相位的电感Ls和电容Cp[7]。原理图和等效电路如图3所示。

图3 压缩相位的Pi型电路原理图及等效电路

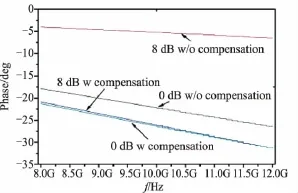

通过选择合适的Ls和Cp,衰减态的传输相位可以近似于期望频率处的非衰减相位。在低衰减状态下,由于相位偏差较小,所以不需要补偿电感。并联的电容Cp和电阻Rp可以形成低通滤波器,并实现相位补偿。为了避免并联网络影响衰减程度,将电阻Rc与电感Ls串联。图4为常规结构和补偿结构的8 dB衰减器的相位特性。

图4 常规结构和补偿结构的衰减器相位特性

2.2 高线性度设计

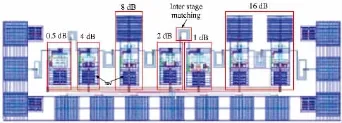

从T型和Pi型这两种基本类型的衰减器可以看出,数字衰减器由MOSFET和电阻组成。CMOS数字衰减器的非线性响应(如输入压缩点)主要是由于阻抗变化导致的[8,9]。通常,电阻的线性度非常好,非线性度主要来自有源器件,即MOSFET。在衰减器中,开关是工作在三极管区的单个NMOS晶体管,其导通电阻可以由下式给出:

其中Kn由工艺决定,Vgs是栅极和源极之间的电压。Vth是MOSFET的阈值电压,θ是和一阶源串联电阻、垂直电场引起的迁移率退化和短沟道器件中横向电场引起的速率饱和等效应相关的系数。Vth0是当Vbs=0时的阈值电压,γ是体阈值参数,φf是体费米电势,Vbs是体和源之间的电压。

从公式(1)和(2)可以看出,导通电阻是MOSFET的Vgs和Vbs的函数。较小的电压摆动导致小的阻抗变化。当输入信号非常大时,Vgs和Vbs变化很大,会导致巨大的非线性度。为了获取固定阻抗,希望Vgs和Vbs不随输入信号变化而变化。常规的RF MOSFET开关如图5(a)所示。

图5 MOSFET开关

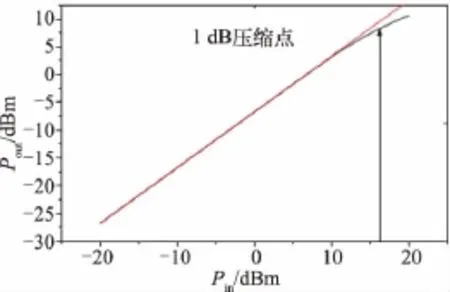

从图5(a)可以看出,栅极电压由于寄生电容Cgs和高值电阻Rg而随源极电压Vin变化,这仅实现了Vgs保持近似恒定。当输入信号Vin改变时,电压Vbs仍然会随之变化。因而采用了如图5(b)所示的浮动衬底技术,MOSFET的衬底不是直接接地,而是通过高值电阻Rb接地。与栅极类似,当Vin改变时,由于寄生电容Cbs和电阻Rb,衬底电压随之改变,从而维持Vgs和Vbs几乎不变。要实现浮动的NMOSFET衬底,需要采用深阱工艺以隔离各个晶体管。通常,电阻Rg和Rb越大越好,但是大的Rg将会降低开关速度。因此,Rb的阻值可以非常大,甚至可以将晶体管衬底网络开路。图6是相同尺寸下的两种拓扑结构MOSFET开关的仿真结果。可以看出,浮体开关的输入1 dB压缩点(P1dB)比常规开关高6 dB。

图6 4 dB的Pi型衰减器的P1dB

2.3 版图设计

基于IBM的8HP 0.13 μm BiCMOS工艺设计了图1所提出的6位衰减器。衰减器的版图如图7所示,包括所有焊盘和旁路电容在内的芯片面积为400 μm× 1400 μm。

为了获得低幅度步进误差,必须实现阻抗匹配。多晶硅电阻的绝对精度非常差。此外,各级衰减器的参考地被隔离开,每级衰减器的参考地通过TSV直接接地。TSV的电感非常小,仅为约50 pH,小的寄生电感有利于提高高频特性。

图7 衰减器版图

3 仿真结果

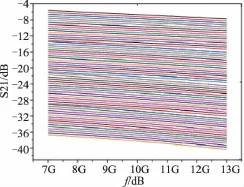

图8(a)和(b)分别显示了在7~13 GHz范围内的输入和输出匹配性能的仿真结果。在此频段内,S11和S22都低于-20 dB。良好的端口回波损耗可以避免连接到其他设备时由于端口阻抗引起的衰减步径误差恶化。

图8 7~13 GHz范围内输入和输出匹配性能仿真结果

图9不同增益模式下的衰减器损耗

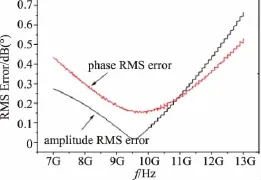

图9 显示了在不同增益模式下衰减器的损耗。从图9可以看出,10 GHz时插入损耗约为6.67 dB。图10显示了不同衰减等级下的插入相移,在X波段内插入相移低至-1°~0.5°。衰减器的幅度和相位的均方根误差参见图11。图12展示了衰减器的线性度,10 GHz下非衰减的1 dB压缩点的输入功率约为15.5 dBm。

图10 不同衰减等级下的插入相移

图11 衰减器的幅度和相位RMS误差

图12 输入1 dB压缩点

表1是本文和国内外数控GaAs衰减芯片的性能对比。从表1中可以看出,本文中设计的衰减器的附加相移显著低于其他GaAs衰减器,并且回波损耗低,端口匹配好,其他性能也可以与各类GaAs衰减器相媲美。

4 结论

本文提出了一种具有高线性度和低附加相移的6位数控衰减器。该衰减器基于IBM 0.13 μm BiCMOS工艺,其最大衰减量为31.5 dB,步进0.5 dB,插入损耗<6.67 dB,回波损耗<-20 dB,10 GHz下输入l dB压缩点值为15.5 dBm,附加相移低至-1°~0.5°。仿真结果表明该衰减器性能可与现有各类GaAs衰减器相媲美。

表1 本论文中的设计与其他GaAs衰减器的性能对比

参考文献: