可变容量的高可靠Flash 型FPGA 配置存储器设计

2023-11-13曹正州查锡文

曹正州,查锡文

(1.无锡中微亿芯有限公司,江苏无锡 214072;2.无锡华普微电子有限公司,江苏无锡 214072)

1 引言

SRAM 型FPGA 由于其灵活可编程、逻辑资源丰富、集成度高和开发周期短的优点,广泛应用在数据处理、卫星通信、航天航空等领域[1]。其核心电路通过可编程逻辑块(CLB)和可编程布线开关矩阵(CSBM)来实现不同的用户逻辑功能[2]。这些可编程的功能是通过配置SRAM 来实现的,通过电子设计自动化(EDA)软件,对代码进行逻辑综合、布局布线后生成实现用户逻辑功能的码流[3]。在FPGA 上电时将码流加载到配置SRAM 中,配置成功后FPGA 即开始运行用户逻辑功能。但SRAM 型FPGA 也有着明显的缺点,由于SRAM 掉电后数据会丢失,所以FPGA 外围需要配置非易失性存储器(NVM)[4]来存储配置码流信息,该类配置存储器电路称为FPGA 配置存储器。根据实现的技术,FPGA 配置存储器分为紫外光擦除电编程只读存储器(UV-EPROM)[5]、电擦除、电编程只读存储器(E2PROM)[6]、反熔丝只读存储器(Anti-Fuse PROM)[7]和快闪只读存储器(Flash PROM)。其中UV-EPROM 和Anti-Fuse PROM 为一次可编程器件,影响电路的上机率;E2PROM 为多次可编程器件,但存储单元占用面积比较大,并且需要专门的编程器。随着FPGA 在现代通信、人工智能领域可重构[8]的应用需求,配置存储器中的码流需要在线更新,显然采用UV-EPROM、E2PROM 和Anti-Fuse PROM 设计的FPGA 配置存储器并不能满足新的技术需求。目前国内研制Flash 型FPGA 配置存储器的公司有复旦微电子、成都华微、紫光国微和中科芯等,已开发出的几款FPGA 配置存储器由于存储容量固定,对SRAM 型FPGA 的适用范围较小。

基于FPGA 配置存储器的上述缺点,本文提出了基于Flash 存储技术的可变容量的FPGA 配置存储器,同时通过双模的上电复位电路和存储器内建自测试(MBIST)设计,使该FPGA 配置存储器具有适用范围广、可靠性高的优点。

2 FPGA 配置存储器设计

本文设计的FPGA 配置存储器基于0.18 μm 2P6M Flash 工艺,支持4 Mbit、16 Mbit 和32 Mbit 可配置,可实现配置存储器电路一款多用;最高工作频率为50 MHz,内核工作电压为2.5 V,端口工作电压为2.5~3.3 V,可适应多种电平标准[9];支持从串、从并等多种接口工作方式,可满足多种FPGA 配置模式的需求[10]。

2.1 功能和整体电路结构

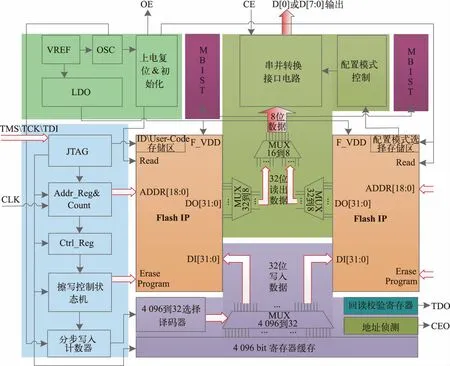

设计的FPGA 配置存储器整体架构如图1 所示,主要由联合测试工作组(JTAG)接口、低压差线性稳压器(LDO)、上电复位与初始化电路、Flash 存储阵列、擦写控制状态机、地址侦测电路、串并转换接口电路和MBIST 电路组成。

图1 FPGA 配置存储器整体架构

采用标准商业线提供的Flash IP 作为存储配置码流的存储单元,每个单元的容量为16 Mbit, 整个32 Mbit 的存储空间由2 个对称的Flash IP 组成。Flash IP 的工作电压为1.8 V,最大工作电流为30 mA,而该配置存储器的电源工作电压为2.5 V,所以为了给Flash IP 提供工作电压,设计了一款基于零极点追踪的片上无电容型的LDO[11],最大负载能力为100 mA,为2 个Flash IP 提供了高质量的稳定电源。

通过JTAG 接口将配置码流写入Flash IP 中,而FPGA 加载数据同样是通过JTAG 接口,所以基于Flash 技术的FPGA 配置芯片支持在线可编程(ISP)功能。JTAG 是业界标准,使用IEEE Standard 1149.1 协议规定的TMS、TCK、TDI、TDO 4 个引脚实现芯片的测试、配置和下载功能。该电路的数据校验同样使用JTAG 协议,通过回读校验寄存器将数据从TDO 端口读出,从而完成写入数据的回读验证。

上电复位与初始化电路为配置存储器提供2 个功能:1)RC 和电压侦测的双模复位电路支持宽范围的上电时间,从而为配置存储器内部逻辑提供可靠的复位;2)初始化脉冲序列电路产生初始化脉冲,将Flash IP 特定区域的数据读出并加载到配置模式控制寄存器中,该数据控制着配置存储器的容量以及同FPGA的配置模式,同时从Flash 存储阵列读出第1 组数据并存储到输出寄存器中。之后,上电复位与初始化电路输出初始化完成标志信号OE(该信号同FPGA 的INIT 端相连)并完成握手协议。

本设计中的FPGA 配置存储器采用商用工艺线提供的标准Flash IP,通常Flash IP 的数据接口位宽为32 bit,每次只能写入32 bit 的数据。为了兼容XILINX公司的ISE 软件(每次写入的数据为4 096 bit),在该配置存储器中设计了4096bit 的寄存器缓存,将4 096 bit数据分64 次写入。配置存储器的接口电路主要包括并转串电路和配置模式控制电路,可实现1 bit 的串行输出或者8 bit 并行数据。

为了提高该配置芯片存储空间的可靠性和缩短测试时间,设计了MBIST 电路。在传统的March C 的基础上提出了一种更全面的改进型测试算法,有效提高了故障覆盖率。

2.2 存储器电路的上电复位与初始化

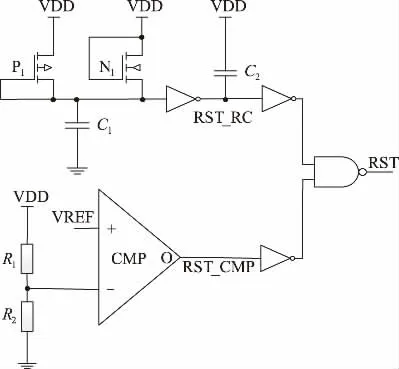

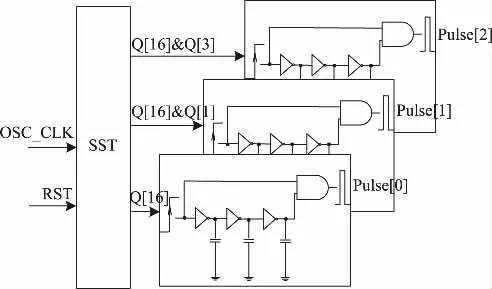

FPGA 配置存储器的上电启动由上电复位与初始化电路实现,该电路主要由带隙基准(VREF)、上电复位(PWR)、振荡器(OSC)、系统稳定时间计数(SST)和初始化脉冲产生(OPG)子电路组成,其中PWR 和OPG 电路原理如图2、3 所示。

图2 PWR 电路

图2 中的RST_RC 信号为基于电阻和电容、利用电容两端电压不能突变的特性而产生的复位信号,该类型的复位适合电源快上电的应用,当电源上电斜率比较小时,RST_RC 信号在电源电压很低时便失效。基于电压检测的复位信号RST_CMP 在电源上电斜率比较小时有效,反而在电源上电较快时由于VREF 信号未能及时建立而失效,所以将RST_RC 和RST_CMP结合起来可以有效解决复杂电源环境的复位问题。

图3 中SST 计数器输出Q[16]、Q[3]和Q[1]的组合信号,进而触发形成Pulse[2]、Pulse[1]和Pulse[0]脉冲信号,利用这3 个脉冲信号进行配置模式的控制和第1 组配置数据的读取并加载到输出寄存器中,等待FPGA 接收数据。

图3 OPG 电路

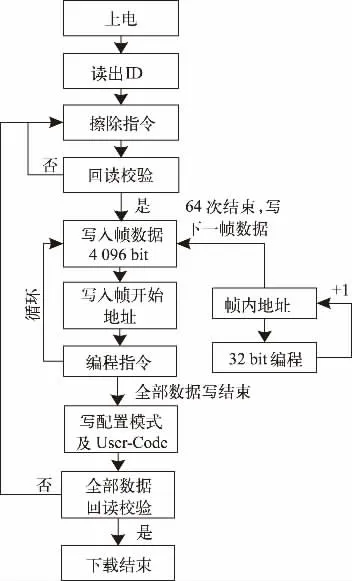

2.3 码流的写入

码流的写入是将ISE 或者VIVDO 软件生成的配置码流通过JTAG 端口写入到配置存储器的存储空间即Flash IP 中。不同于反熔丝型存储器的编程[12],此处首先需要对Flash IP 进行擦除操作,回读校验全为“0”后再进行写入的循环流程。每个写入的循环流程的数据为4 096 bit,因为Flash IP 的数据接口位宽为32 bit,所以设计了数据寄存器缓存,通过写入控制电路将4 096 bit 分64 次写入。最后一帧数据写结束后会向Flash IP 的特定存储空间写入配置模式控制和用户的User-Code 等信息。最后进行全部数据的回读校验,回读校验通过,对FPGA 配置存储器的下载完成。码流的写入、下载流程如图4 所示。

图4 码流的写入、下载流程

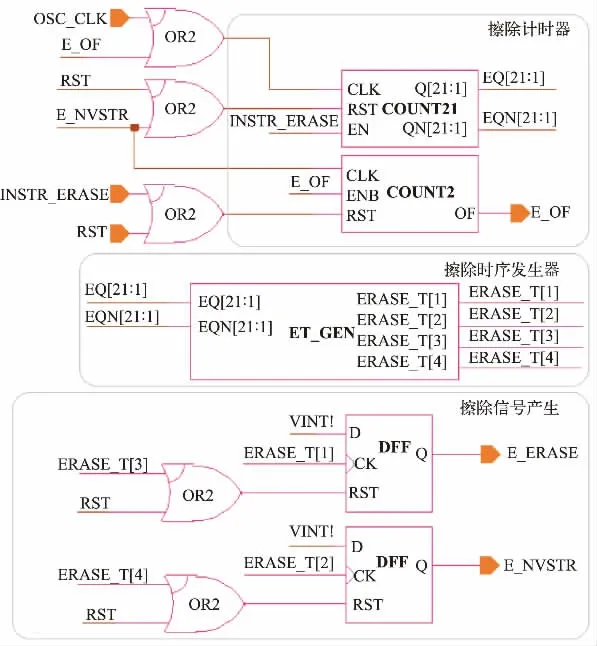

擦除控制电路如图5 所示,主要由擦除计时器、擦除时序发生器和擦除信号产生电路组成,其中计时器COUNT21 收到擦除指令后对OSC_CLK 时钟进行计数,计数结果EQ[21:1]和EQN[21:1]被送给擦除时序发生器,经过逻辑组合和毛刺消除后产生ERASE_T[1:4]信号,该信号用于擦除信号产生电路的时钟输入,将“1”写入DFF,从而产生E_NVSTR 和E_ERASE 信号。其中E_ERASE 为进入擦除状态信号,开启内部的电荷泵电路,E_NVSTR 为有效擦除信号,开始15 ms的Flash 存储空间擦除。

图5 擦除控制电路

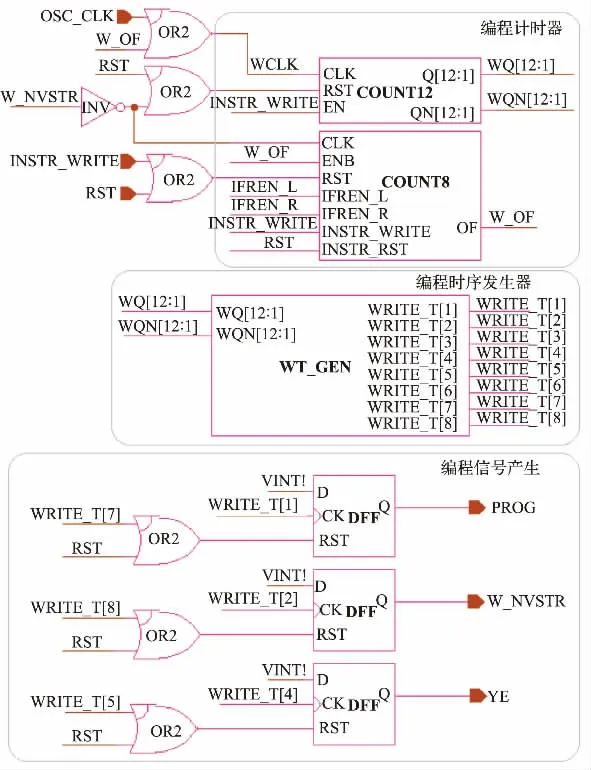

写入(编程)控制电路如图6 所示,主要由编程计时器、编程时序产生器和编程信号产生电路组成。PROG 为进入编程状态信号,启动内部的电荷泵电路,YE 为数据和地址的锁定信号,W_NVSTR 为有效的编程信号,对Flash 地址选中的存储单元开启20 ms 的编程。

图6 写入(编程)控制电路

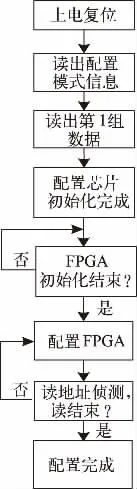

2.4 码流的读出

码流的读出是将Flash 存储阵列中的数据读出[13],并通过串行或者并行的方式加载到FPGA 中。码流的读出加载流程如图7 所示,首先上电复位,接着从Flash IP 特定存储空间读出配置模式控制信息并加载到配置模式控制寄存器中,再从Flash IP 常规存储空间读出第1 组配置数据并加载到输出缓存器中,初始化完成,等待FPGA 初始化结束,完成握手后开始向FPGA 中加载码流。

图7 码流的读出加载流程

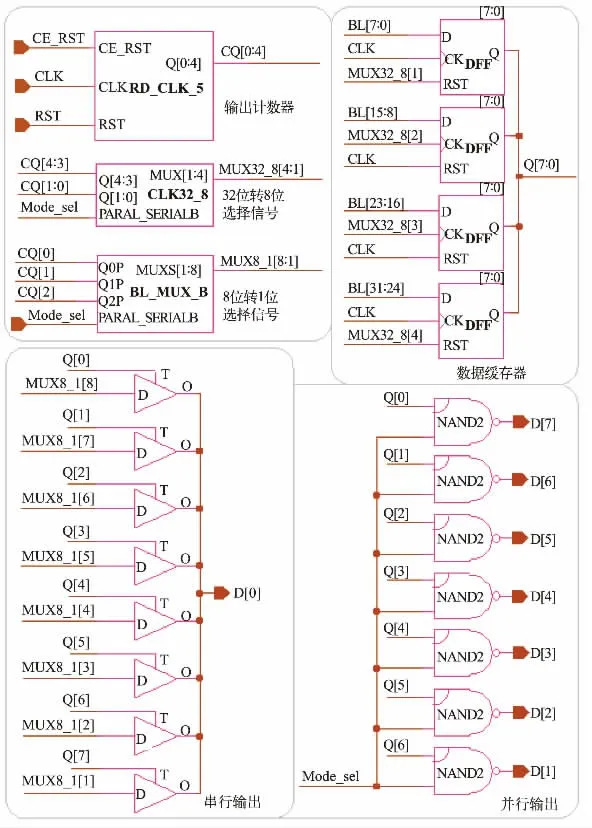

码流读出加载的主要控制电路如图8 所示,主要由输出控制电路(输出计数器、32 位转8 位信号选择电路、8 位转1 位信号选择电路)、输出缓存器、串行输出电路和并行输出电路组成。数据缓存器中的数据会在输出控制电路的控制下从D[0]端口串行输出或是从D[7:0]端口并行输出。

图8 码流读出加载的主要控制电路

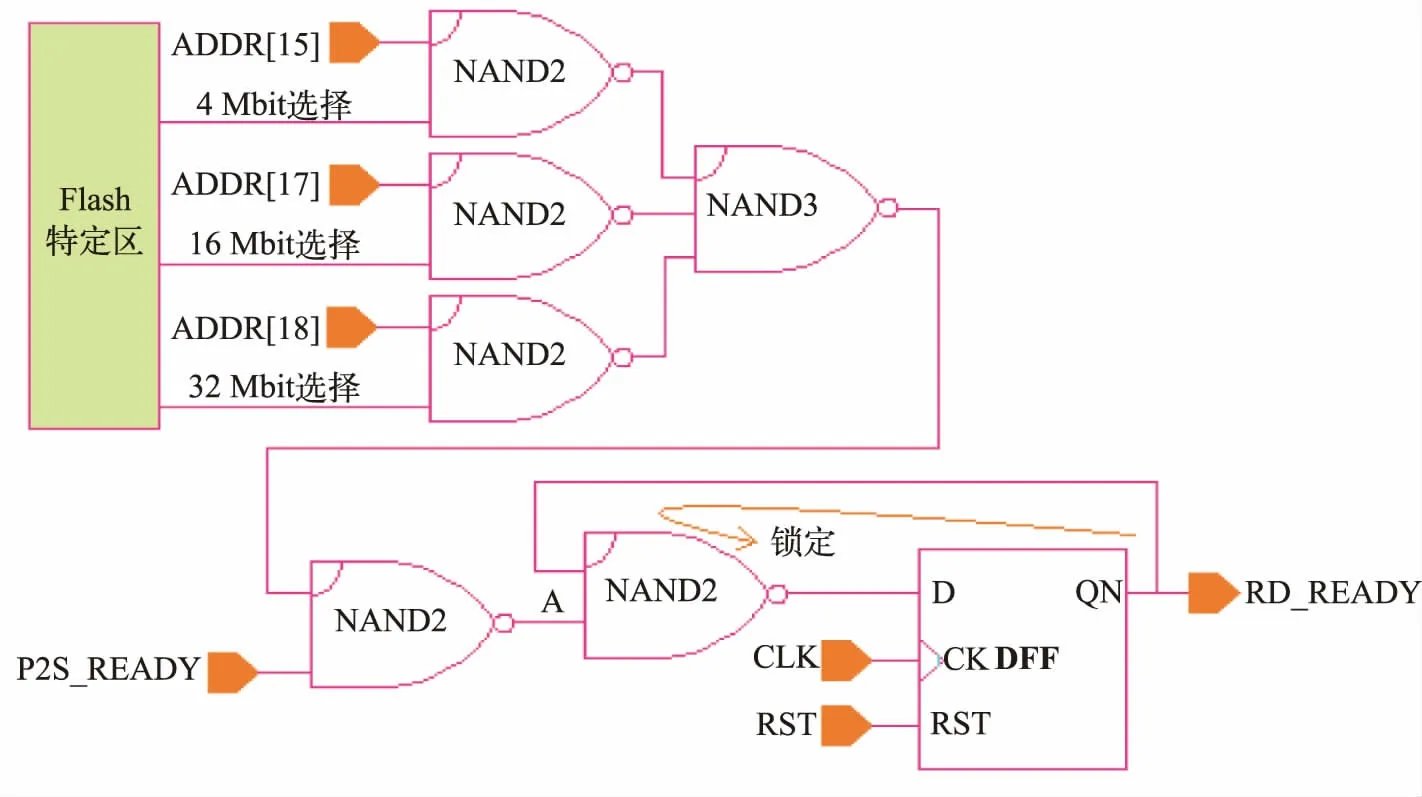

地址侦测电路实现了该FPGA 配置存储器容量的可变性。因为FPGA 同FPGA 配置存储器相连的端口D[7:0]为共用端口,FPGA 配置存储器在完成向FPGA 加载数据后必须将数据输出端口D[7:0]置为高阻抗状态,否则会影响FPGA 的功能,在FPGA 配置完成后该端口可以作为普通的用户I/O 端口来使用。所以作为一款多用的可变存储容量的FPGA 配置存储器,它需要在以非最大存储容量使用时必须及时关闭数据输出端口,使其处于高阻抗状态,该功能由地址侦测电路来完成,地址侦测电路如图9 所示。

图9 地址侦测电路

地址侦测电路通过DFF 的输出端QN 到输入端D 的反馈实现锁定功能,锁定后DFF 的值无法改变。在初始化过程中,从Flash 特定区读出的信息作为存储容量的控制信号,按容量大小选择相应的最高位地址线,当最后一组32 位数据输出完成后,P2S_READY为高电平,图9 中的A 点即为逻辑“0”,从而将逻辑“1”写入到DFF 中,QN 从逻辑“1”变成逻辑“0”,这时即使A 点的值发生变化,DFF 值也无法改变。输出的RD_READY 信号会将输出端口D[7:0]置为高阻抗状态,并且CEO 端口输出高电平。

2.5 Flash 的MBIST

MBIST 模块主要实现Flash 的内建自测试功能。按照Flash 厂商提供的测试向量,先对Flash 进行擦除后写入测试向量,再读取做比对。通过MBIST 模块,可大大减少芯片的测试时间,以4 Mbit 容量的Flash测试为例,使用J750 机台对未采用MBIST 的一颗电路在一个温度下完成全地址“00”、“FF”、“55”和“AA”测试需要约2 min,而对采用了MBIST 的一颗电路在同一温度下完成上述测试仅需约0.5 min,节约了约75%的测试时间。

Flash 的MBIST 对存储空间包括MAIN 区、NVR2 区、冗余区都进行擦除、写、读操作,如果读操作的返回数据与写入数据不一致,即认为Flash 存储出现坏点,输出相应错误标志。

3 仿真及结果分析

采用HSIM10.12 搭建混合仿真平台,对该FPGA配置存储器上电复位及初始化功能、整体写功能和读功能进行仿真,仿真条件为TT、25 ℃、2.5 V。

10 μs 上电时间的快上电复位波形如图10 (a)所示,在快上电过程中,基于电压检测的复位信号RST_CMP 失效而基于电阻电容的复位信号RST_RC有效。100 ms 上电时间的慢上电复位波形如图10(b)所示,在缓慢的电源电压上电过程中,RST_RC 信号失效而RST_CMP 信号有效。所以采用电阻电容复位和电压检测复位相结合的双模复位电路可以使电路适应复杂的电源环境,在10 μs~100 ms 的上电时间内均能为电路提供有效的复位信号。

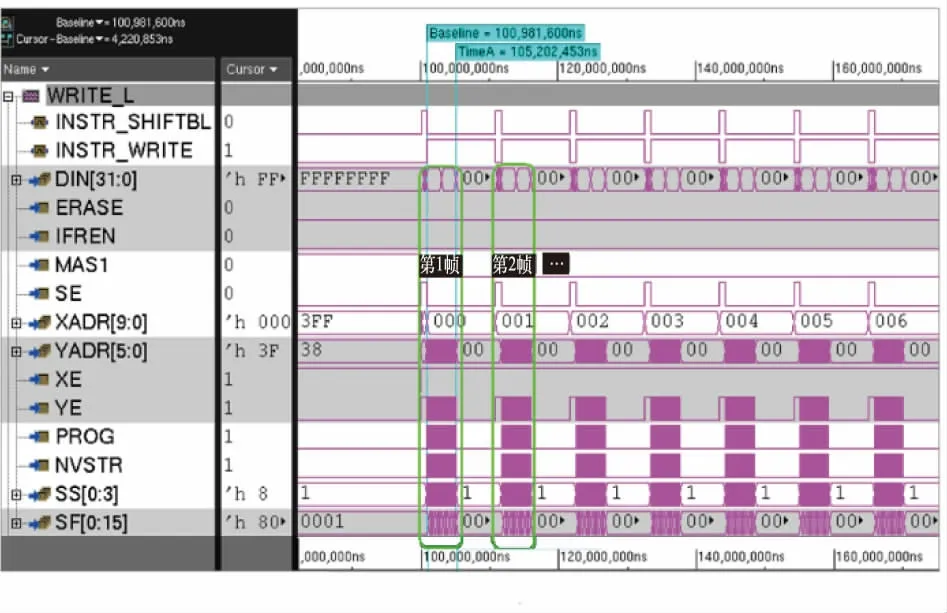

FPGA 配置存储器的写数据波形如图11 所示,在每帧4 096 bit 的写入过程中,YADR[5:0]遍历1遍共64 次,2 个Flash IP 同时写,每次共写入64 bit的数据。

图11 FPGA 配置存储器的写数据波形

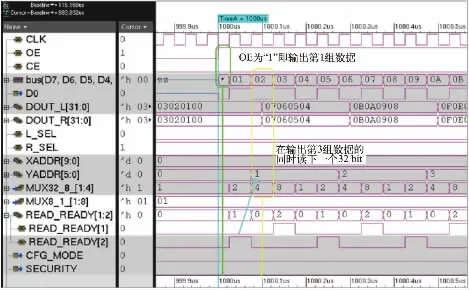

以并行数据输出为例,FPGA 配置存储器的读出数据波形如图12 所示。OE 为高(初始化完成)即输出第1 组数据,将从Flash 存储器中读出的32 bit 数据转化为8 bit 数据并从D[7:0]端口输出。在每个32 bit 数据转8 bit 数据的过程中,输出第3 组数据的同时从Flash 存储空间中开始读下一地址位的32 bit 数据。

图12 FPGA 配置存储器的读出数据波形

本文设计的可变容量的高可靠性FPGA 配置存储器解决了FPGA 配置存储器的国产化问题,可以替换XINLIX 公司的XC18V04、XC17V16 和XCF32P 3款电路,流片后电路的实测结果表明,本设计在工作电流、静态电流和数据输出延迟方面与国外电路相当,工作频率稍优于国外电路(最大40 MHz)。

4 结论

本文设计了一种可变容量的高可靠性FPGA 配置存储器,它支持4 Mbit、16 Mbit 或者32 Mbit 可配置。该FPGA 配置存储器采用业界标准的JTAG 接口和商用工艺线提供的Flash IP,支持串行和并行数据输出。通过设计的地址侦测电路、双模上电复位电路,使Flash 型FPGA 配置存储器在原有的面积小、支持ISP特点的基础上增加了存储容量可变、可靠性高的特点,从而可以适用于多款SRAM 型FPGA 和更复杂的电源环境。该配置芯片中的MBIST 电路可以完成对整个存储空间的全地址覆盖测试,减少了约75%的测试时间,并且有效剔除了存储单元失效的电路,相当于提高了FPGA 配置存储器存储空间的可靠性。