基于陶瓷衬底的薄膜再布线工艺及组装可靠性研究

2023-11-13朱喆黄陈欢李林森刘俊夫

朱喆,黄陈欢,李林森,刘俊夫

(1.中国电子科技集团公司第四十三研究所微系统安徽省重点实验室,合肥 230088;2.中国电子科技集团公司第四十三研究所,合肥 230088)

1 引言

随着微系统集成技术的发展,武器装备导引系统在体积微缩的前提下,仍然要提升其信息处理能力。高算力、大容量计算芯片在武器装备导引系统中必不可少,这类芯片通常具有相当数量的I/O 引脚和高的引脚密度,这使其封装技术遇到了挑战。基于陶瓷封装技术的薄膜陶瓷多芯片组件(MCM-C/D),通过在陶瓷外壳上制备高精度的薄膜布线,为内部电路元器件提供气密环境[1]。该封装技术可满足航天等领域对器件高可靠封装的需求。而使用该技术对计算类芯片进行封装时,在满足组装可靠性要求的同时,其封装载板布线的制备工艺也遇到了高密度细线条的调整等难题。

常规薄膜布线工艺可以在陶瓷、金属等表面实现数μm 到数十μm 级别的布线,常规的陶瓷布线能力大于100 μm。而常见计算芯片多以球栅阵列封装(BGA)形式引出,焊盘节距为200 μm 左右,球径在100 μm 左右。由于其I/O 数量较多,若要将引脚互连散出,直至达到陶瓷布线120 μm/120 μm 的密度,需要一层50~120 μm 线密度的布线层作为过渡,因此至少需要两层薄膜布线。多层薄膜布线结构在硅转接板、玻璃转接板等领域有较多研究,以陶瓷为衬底的薄膜再布线工艺业内多见于基于低温共烧陶瓷的MCM-C/D 研究,应用于微波射频领域。相比而言,高温共烧陶瓷(HTCC)在机械强度、热导率、气密性上均有优势,有望形成高气密性、高可靠的MCM-C/D 载板[2-5]。在高温共烧陶瓷衬底上制备两层薄膜布线,需要合理设计复合膜层结构、处理层间工艺界面,使薄膜图形仍然具有高精度、高密度的优势。因此,有必要对陶瓷衬底上的薄膜多层布线技术进行研究。针对以上问题,本文进行了再布线层结构与工艺设计及膜层附着力、可焊接性等相关研究。

2 陶瓷衬底上的再布线层设计

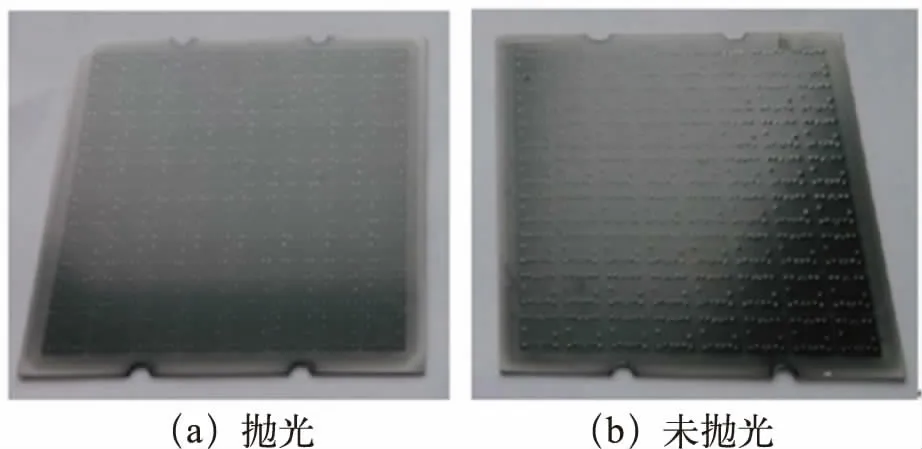

计算芯片对封装布线载板的布线能力要求高,所使用的陶瓷衬底为多层叠烧的共烧陶瓷,共烧陶瓷层间通过金属钨浆料填充的通孔互连。在共烧过程中,生瓷带与金属浆料发生不同程度的收缩,由于生瓷带的收缩程度大于金属浆料,在陶瓷烧结整平后,表层的通孔位置存在钨柱凸起现象,需要通过研磨抛光,消除钨柱凸起,为薄膜布线提供平整、致密的工艺平面[6]。图1 为共烧陶瓷衬底表面钨柱凸起示意图,抛光与未抛光的共烧陶瓷衬底表面状态如图2 所示。

图1 共烧陶瓷衬底表面钨柱凸起示意图

图2 抛光与未抛光的共烧陶瓷衬底表面状态

在研磨抛光处理的陶瓷衬底上制备薄膜再布线层需要综合考虑薄膜与陶瓷附着力、薄膜再布线层层间附着力以及与封装芯片I/O 管脚的组装适配性。因此,设计了如图3 所示的基于共烧陶瓷衬底的薄膜多层再布线结构,整体结构为HTCC-2M2P 结构。

图3 基于共烧陶瓷衬底的薄膜多层再布线结构剖面

采用光敏聚酰亚胺作为薄膜再布线介质层。金属膜层导体为Cu,为了增强金属导体与陶瓷衬底的结合,同时防止Cu 向介质层中扩散,造成可靠性问题,需要在导体Cu 下设计过渡层[7]。M2 层起元器件组装和互连功能,为了提升布线密度,降低因层数增加和工艺界面增加带来的可靠性风险,M2 层采用可焊接的膜层结构。将P2 层制备在M2 层上,形成表层焊盘开窗。金属层间的绝缘与通孔互连,采用光敏聚酰亚胺材料制备介质层实现,该材料介电常数低(<3.5),有利于降低高速信号传输的延迟时间,提高传输速率。基于陶瓷衬底的薄膜再布线结构参数如表1 所示。

表1 基于陶瓷衬底的薄膜再布线结构参数

3 薄膜再布线层制备

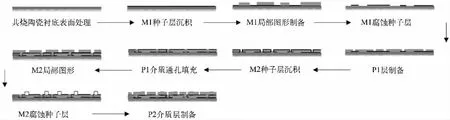

薄膜再布线结构的工序流程如图4 所示,通过逐层制备实现多层结构。首先对研磨抛光过的陶瓷衬底进行高温烘烤、化学试剂清洗等处理,然后使用真空溅射工艺沉积M1 层的金属种子层。为了提升金属与陶瓷的结合力,在金属Cu 之前沉积一层黏附层[8],M1层图形使用局部生长的加法工艺制备。M1 层种子层腐蚀去除后,开始制作P1 层。P1 层使用光敏聚酰亚胺,通过旋涂、曝光、显影,在M1 层金属图形上制备出具有通孔的P1 层图形。介质通孔的填充与M2 层金属生长同步完成,通过种子层沉积、光刻掩模、局部生长,然后腐蚀去除种子层,完成M2 层金属的制备。为了减少布线层数和提升再布线结构的可靠性,将M2 层金属设计成可焊膜层,不单独制备焊盘下金属层。M2层作为可组装平面,其图形间的阻焊通过制备P2 层实现。

图4 薄膜再布线结构的工序流程

本文所述的陶瓷基薄膜再布线结构应用于计算芯片封装领域,布线线宽/间距在40 μm/40 μm 及以下[9],并且具有大量平行的差分信号线。若采用整面镀覆再蚀刻的减法工艺制备图形,湿法腐蚀液的钻蚀难以保证细线条图形的完整度,并且干法刻蚀4 μm 的金属Cu 对于光刻掩模的抗性将是巨大的挑战。因此本文采用加法工艺制备金属图形,通过光刻胶形成围坝来约束密线条生长的形貌,然后去除光刻胶围坝,蚀刻掉较薄的种子层来获得金属线条。经此工艺制备的M1 和M2 层金属图形照片如图5 所示,图6 为陶瓷基薄膜再布线结构剖面图。

图5 M1 和M2 层金属图形照片

图6 共烧陶瓷基薄膜再布线结构剖面

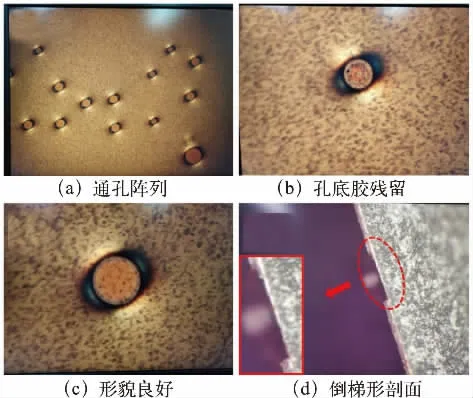

薄膜再布线的介质层采用光敏聚酰亚胺材料制备,介质层通孔的质量影响层间金属互连,进而影响电信号在多层结构中的传输,是再布线技术的核心。通过调整曝光、显影、固化参数,可以获得形貌良好的介质通孔,为金属填孔提供有利条件[10]。图7 给出了几种典型的光敏聚酰亚胺介质层通孔形貌。经实验可知,剖面呈倒梯形且孔底无胶残留的通孔最有利于金属化填充。

图7 光敏聚酰亚胺介质层通孔形貌

4 测试与评价

4.1 结构测试

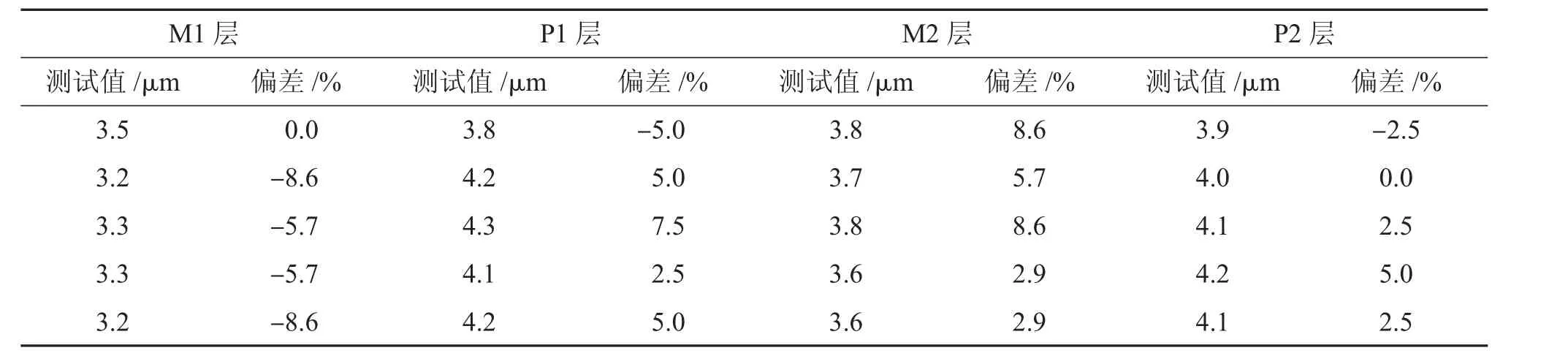

参考标准GJB548C 方法2032.1 中平面薄膜元件检查条目对金属化突出和多层薄膜缺陷的判定标准:1)金属化突出与相邻工作金属化之间的初始间隔减小了50%以上,不得接收;2)绝缘材料扩展超出金属化的宽度未达到8 μm,不得接收。由于本研究在膜层结构设计时考虑到了金属绝缘和多层薄膜介质层图形与金属图形匹配的问题,因此参考GJB548 判定标准,在本文所述的结构下,金属线条宽度在15~45 μm和50~150 μm、介质层通孔孔径在42~58 μm 视为合格,介质层厚度的设计值为4 μm,偏差需在±20%以内。金属膜层厚度设计在2.8~4.2 μm。

金属膜层的形成由真空沉积工艺沉积种子层和电镀工艺生长共同完成,造成厚度偏差的主要因素是电镀过程中的药水状态、工艺参数等。本研究在样品研制过程中,通过添加辅助阴极、增强药水搅拌等方式,提升镀覆过程中电力线分布的均匀性,从而获得比较均匀的膜层生长速率。而介质层厚度主要受旋涂参数、显影参数的影响,本研究在样品研制过程中,通过优化滴胶量、旋涂速率、显影时间等参数,将聚酰亚胺介质胶的厚度损失量与现场设备能力进行了匹配,从而获得了比较稳定的光刻工艺参数。

分别使用德国Fischer 公司的X 射线荧光仪、美国KLA 公司的台阶仪、日本Keyence 公司的光学测量显微镜,使用5 点测试法对制备的样品进行膜层厚度和图形形貌测量,多层薄膜再布线结构的膜层厚度测量结果如表2 所示,多层薄膜再布线结构的线条宽度/通孔直径测量结果如表3 所示。从表2、3 可以看出,膜层厚度、线条宽度和通孔直径偏差均满足设计要求。

表2 多层薄膜再布线结构的膜层厚度测量结果

表3 多层薄膜再布线结构的线条宽度/通孔直径测量结果

4.2 可靠性评价

为了进一步考核薄膜再布线膜层的可组装性,设计了如表4 所示的可靠性评价分组实验。其中A 组样品5 只,在再布线层表面焊接0201 端头电容,按顺序经历表4 中的实验项目后,抽取3 只样品进行剪切评价。B 组样品5 只,在再布线层表面键合25 μm 金丝,按顺序经历表4 中的烘烤条件后,抽取3 只样品依次进行拉力和球剪切力评价。

表4 可靠性评价分组实验

4.2.1 A 组实验结果

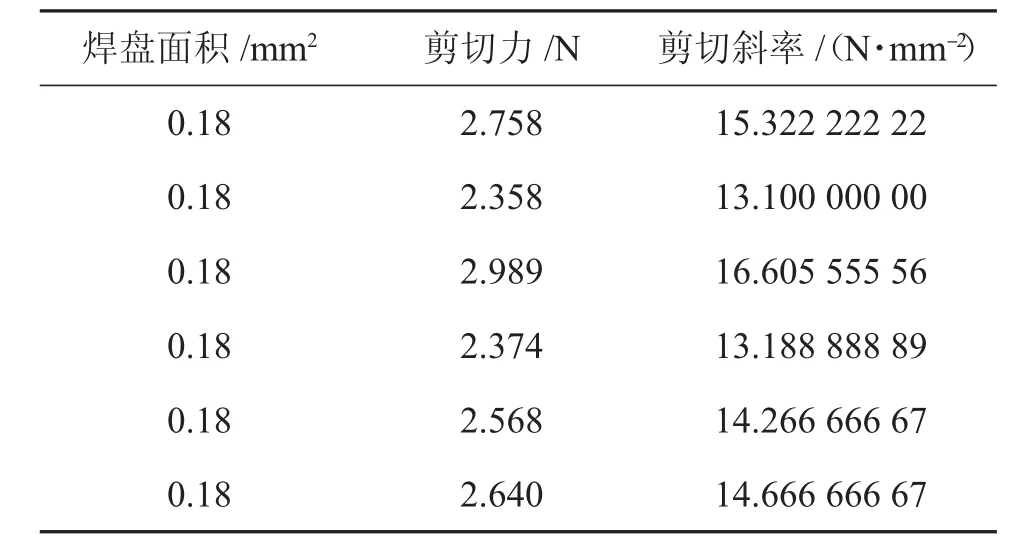

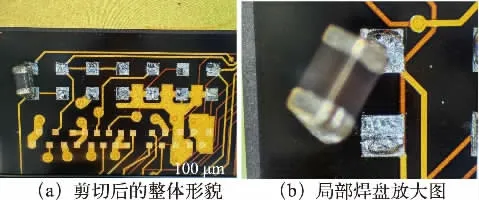

为了摸底再布线层的可焊接性和焊接可靠性,对A 组实验后的样品进行目检和剪切力评价。经过A 组实验项目后,参考GJB548C 方法2019.3 进行电容的剪切强度评价,电容端头的焊料未产生可见裂纹或脱落。A 组检验的电容剪切数据如表5 所示。根据有效焊接面积(焊盘尺寸)换算得到剪切斜率,剪切斜率为被剪切器件单位面积内的剪切力,代表了芯片剪切强度。从表5 可知,样品的芯片剪切强度在13.1 N·mm-2以上,满足方法2019.3 中附着区面积小于4.13 mm2的被试件最小剪切强度为12.2 N·mm-2的合格判据,且剪切后的焊接面完整,未发生膜层脱落现象,再布线层剪切后的样品照片见图8。

表5 A 组检验的电容剪切数据

图8 再布线层剪切后的样品照片

4.2.2 B 组实验结果

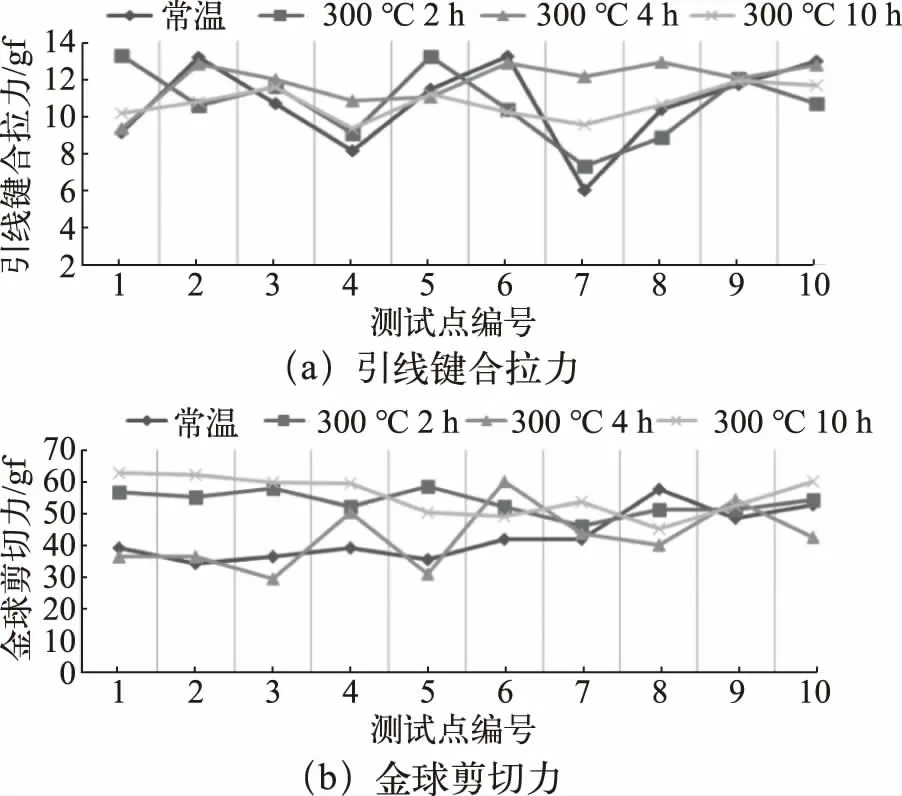

为了摸底再布线层表层的附着力,对B 组实验后的样品进行拉力和球剪切力评价。评价方法与判据分别参照GJB548C 方法2011.2 与方法2011 附录A 中的评价方法与判据。本文使用25 μm 金丝,考虑到有两个键合球,因此拉力应≥6 gf,单个键合球剪切力应≥22.8 gf。

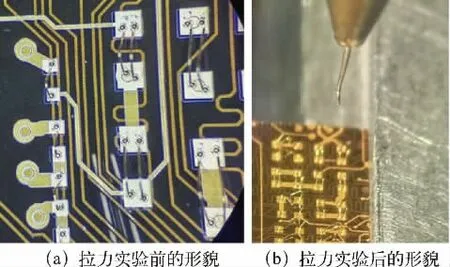

图9 为不同温度存储条件下的引线键合拉力和金球剪切力数据点线图。10 h 之内高温烘烤后,拉力数据仍能满足GJB548 的合格要求。键合丝断裂位置为第一点丝颈部断裂,未发生膜层剥离现象,图10 为B 组样品实验前后的照片。对比不同高温烘烤时间下的金球剪切数据,可以发现剪切力满足GJB548 规定的合格判定要求。剪切失效模式为焊球部分脱落,焊盘完整。

图9 不同温度存储条件下的引线键合拉力和金球剪切力

图10 B 组样品实验前后的照片

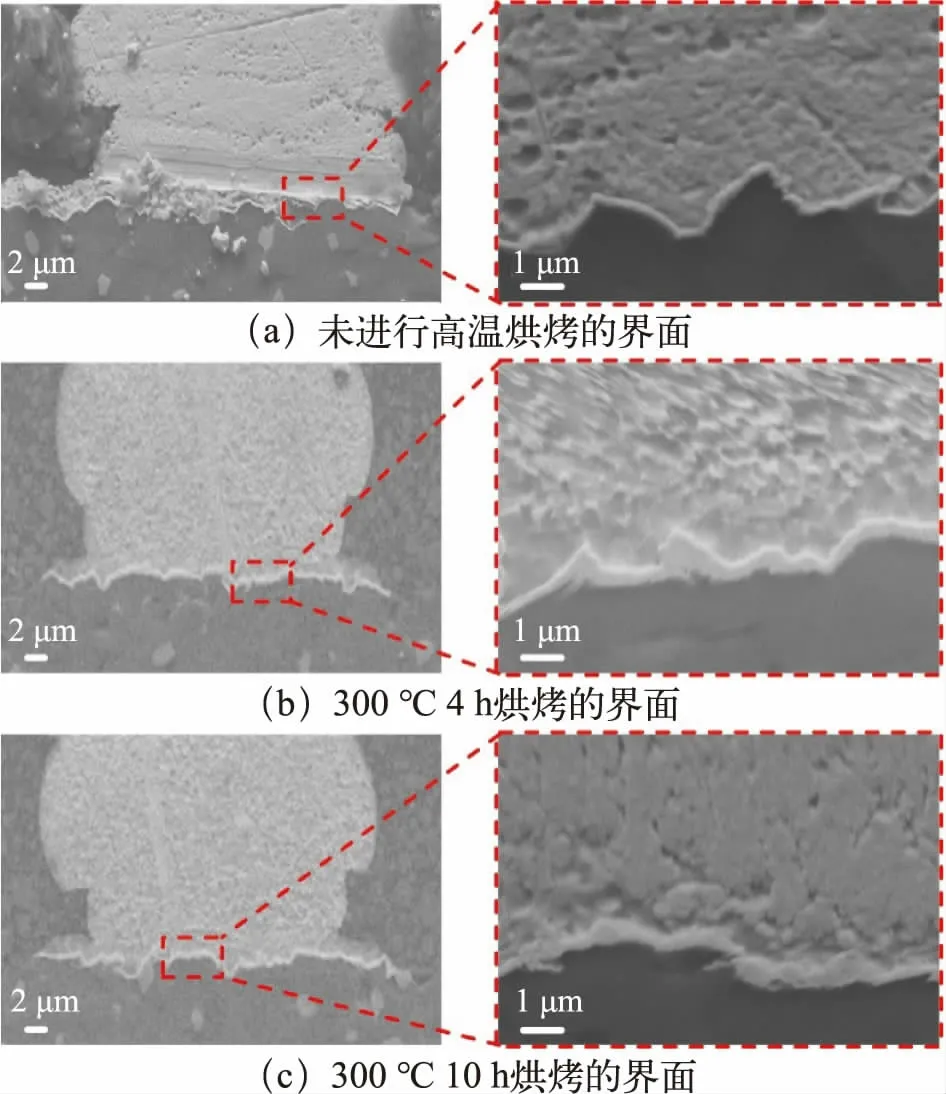

为了进一步研究B 组样品在引线键合拉力和金球剪切评价中呈现的现象,对该组样品进行了扫描电子显微镜分析。通过制备剖面样品,观察到了金球与薄膜再布线层的结合界面,照片如图11 所示。界面处的结合情况是影响键合球与再布线层结构结合力的关键因素,因此采用扫描电子显微镜观测了键合界面处的金-金结合界面,从图中可以看出,随着高温烘烤时间的延长,结合界面的边界变得模糊,表明两者的结合更加紧密。

图11 薄膜再布线层上金球焊接界面剖面扫描电镜照片

5 结果和讨论

薄膜再布线样品在实验条件下未发生剥离、破损等失效现象,数值满足GJB548 中的合格判据。在本检验条件下,再布线层的膜层附着力满足要求,具体表现为:引线键合拉力在经历过不同时间的高温(300 ℃)烘烤后,均表现为键合丝颈部断裂,且未观察到明显的变化趋势,表明在本实验条件下,键合金丝与薄膜再布线层的结合力相对较强,在竖直拉力下,断裂位置发生在金丝颈部而未破坏膜层。

样品表面存在键合金球与薄膜布线表层金的金-金同质界面,引线键合结束后,该界面处存在较薄的互扩散层,随着高温烘烤的进行,结合界面处位错、缺陷逐渐析出和消除,界面处两侧金属结合更加致密,表现为金球经历高温烘烤后剪切强度增加。从扫描电镜照片可以看到比较清晰的金球与薄膜金层的界面,随着高温存储时间的延长,该界面渐渐变得模糊,表明两者结合更加紧密。

6 结论

本文设计并研制了一种基于高温共烧陶瓷衬底的多层薄膜再布线结构,布线密度(线宽/ 间距)≤40 μm/40 μm。对制备出的HTCC-2M2P 结构的样品进行了外观测量和可靠性评价。其线条宽度偏差、通孔直径偏差、复合膜层厚度偏差均满足设计要求。

本文成功制备的以共烧陶瓷为衬底的薄膜多层再布线结构,可以应用于高密度集成的计算领域,作为MCM-C/D 封装的高密度载板。未来需要继续解决该类结构的长期可靠性问题,并进一步提升其集成密度(如线条密度、层数等),并需要与微系统电路进行协同设计,优化载板的膜层结构,以满足Chiplet 生态系统下高密度、高可靠系统集成的需求。