基于信号完整性的万兆通信系统的优化设计

2023-11-13李宇飞马秀碧冉万宁

李宇飞,马秀碧,冉万宁

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

随着电子技术的快速发展,通信速率急剧增大。光纤通信技术以其极快的传输速率、极强的抗干扰能力和更低的建设成本,短短数年间在大部分国家被广泛推广和普及,并成为了主流的通信传输技术[1-2]。其中,高速PCB 的设计成了影响光纤通信产品性能以及稳定性的关键因素。

在高速PCB 设计当中,PCB 走线、器件布局、叠层设置等都会造成信号完整性问题[3-5]。相较于传统的只凭仪表仪器待制版后进行测量的方法,基于信号完整性的设计在布线过程中增加了仿真的验证,大大提高了设计的效率与成功率。

本文针对一款成熟的光纤通信产品在实际使用过程中提出的改进需求,在不改变原有器件选型和整体布局的情况下,重新对高速链路的布线进行设计以满足改进需求,设计过程中进行了仿真验证,经最终投板测试达到了改进目标。

2 万兆以太网卡

本文使用的万兆以太网卡是本公司设计生产的一款光纤通信产品,该板卡用于万兆网络数据的处理与传输。万兆以太网卡基于FPGA 中间层板卡(FMC),引脚定义符合高引脚计数(HPC)标准。单板集成了1 片XC7K325T 最小系统以及2 个单路光收发一体模块(最多可支持4 个光模块),数据传输速率高达10 Gbit/s[6],外围硬件资源还有PRO_CLK 时钟模块、调试JTAG、调试串口RS232、FPGA 配置芯片QSPI Flash 和配置存储EEPROM 等。该网卡以其稳定、高速的传输速率和较低的误码率(BER)受到用户的肯定,目前已实现小批量生产。

3 万兆以太网卡改进设计

万兆以太网卡遵循FMC 标准而设计,可作为一款通用产品供有大数据量通信要求的用户使用。在市场调研中得知有些用户有光纤通信需求,但该用户载板FMC 连接器高度较网卡设计值小1 mm,这就造成网卡光模块与用户载板干涉,无法安装。解决干涉问题有两种方案:一是选用性能参数相同、高度小1 mm的光模块;二是将光模块处的PCB 做薄1 mm,同时优化周围线路。考虑到改进周期、物料成本等因素,最终决定采用第二种方案。

改进后的网卡需要将光模块周围的PCB 减薄,而原PCB 仅为1.6 mm,叠层数仅有10 层。因此,需要先增加PCB 板的厚度和叠层数量,以方便后续布线工作。改进方案中,将PCB 叠层数量从10 层增加到16层,将PCB 板厚度从1.6 mm 增加到2.2 mm。在此基础上,将光模块周围的部分PCB 减薄1 mm,并将叠层数量减少到8 层,以达到改进目标。同时,针对光模块周围电路做适应性更改,其中包括速度最快的光纤通信链路,其最大速率高达10 Gbit/s,奈奎斯特频率为5.16 GHz。由于光模块周围减薄,去耦电容需重新布局,考虑到高速电路信号完整性涉及的衰减、反射、振铃、码间干扰等问题,改进后的链路应最大限度地保持原链路状态。

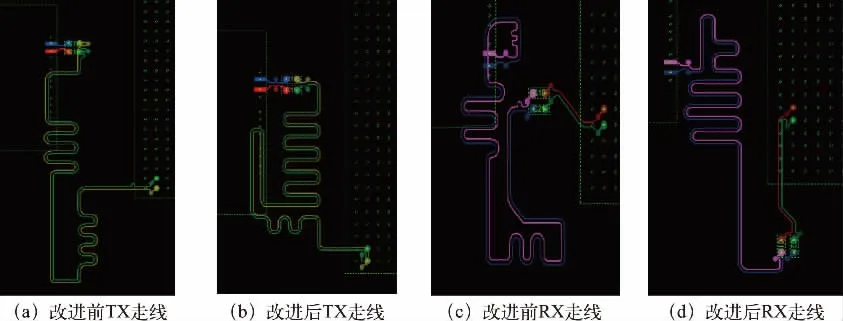

改进前后走线对比如图1 所示,对于TX 信号,改进前的走线长度为68.300 6 mm,连接关系为:FPGA→过孔→第8 层传输线→过孔→去耦电容→光模块。改进后的走线长度为71.526 4 mm,连接关系为:FPGA→过孔→第14 层传输线→过孔→去耦电容→过孔→光模块。对于RX 信号,改进前走线长度为71.323 2 mm,连接关系为:光模块→过孔→第6 层传输线→过孔→去耦电容→过孔→第6 层传输线→过孔→FPGA。改进后的走线长度为71.501 mm,连接关系为:光模块→过孔→第12 层传输线→过孔→去耦电容→过孔→底层传输线→过孔→FPGA。改进后高速链路焊盘大小、过孔大小、阻抗都与改进前的链路保持一致。

图1 改进前后走线对比

4 信号完整性仿真分析

万兆以太网卡改进设计需解决高速链路的信号完整性问题,本文通过仿真工具在制版前对关键信号进行仿真分析,力求将设计风险降到最低,缩短改进设计周期。在仿真正式实施之前,需要准备各种参数准确的电路模型。目前针对板级各元素的模型种类有很多,包括以IBIS 为代表的电工学特性模型,以SPICE 为代表的工作原理模型、以S 参数为代表的频域模型。IBIS 模型的优点是建模方便,节约资源,适用范围广泛;SPICE 模型则在计算精度方面有较大优势,但模型复杂,计算时间长;S 参数模型通常用于描述无源线性网络[7]。本文对仿真模型的建模采用的是分而治之的方式,对高速链路上的芯片、传输线、电容等分别建立等效的电路模型,最终将各部分进行级联。XC7K325T 采用Xilinx 官方网站下载的IBIS 模型,去耦电容模型采用村田公司提供的S 参数模型。由于光模块厂家无法提供相应的模型,且万兆以太网卡改进前后光模块未做更换,本文在仿真时准备了多个连接器的模型,通过对比仿真结果与实测眼图,选取仿真结果最为接近的连接器的模型替代光模块模型。通过PCB 走线、提取相应的过孔S 参数,建立万兆以太网卡高速串行链路仿真模型,结果如图2 所示,信号由FPGA 发出,经PCB 上的TX 走线至光模块的TX 端,进行光/电转换后,又从光模块的RX 端进入PCB 板的RX 走线,最后进入FPGA。

图2 万兆以太网卡高速串行链路仿真模型

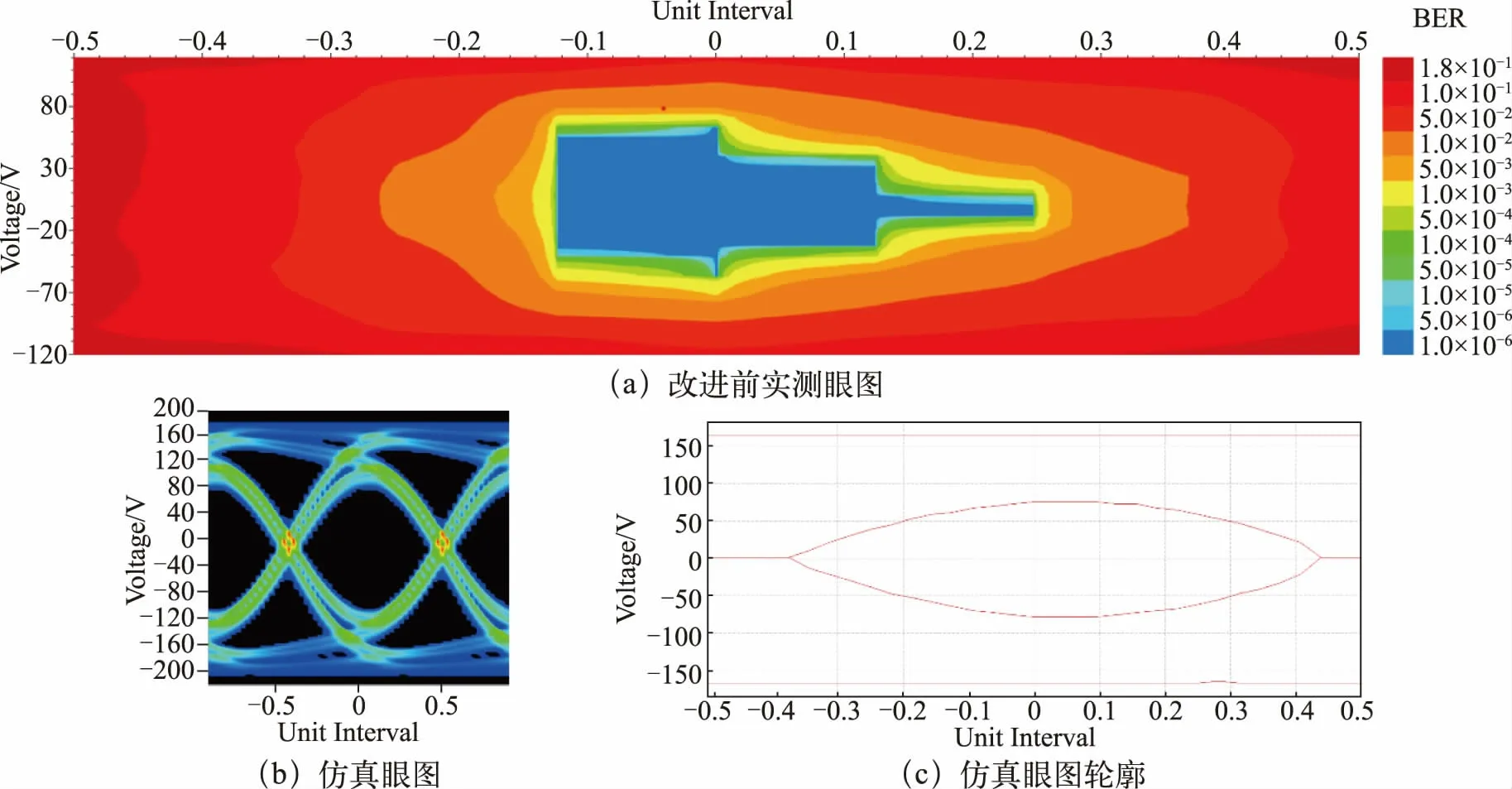

根据万兆以太网卡实际使用情况设置激励特性,速率为10 Gbit/s,数据模式为随机,编码类型为8 B/10 B。改进前实测眼图与仿真眼图对比结果如图3 所示,从图3 可以看出,改进前实测眼图与仿真眼图的眼高相当,仿真眼图眼宽略宽于实测眼图,两者眼图的张开程度相当,信号质量相当。从仿真结果来看,模型的精度满足仿真分析的要求,可以用于万兆以太网卡的改进仿真。

图3 改进前实测眼图与仿真眼图对比结果

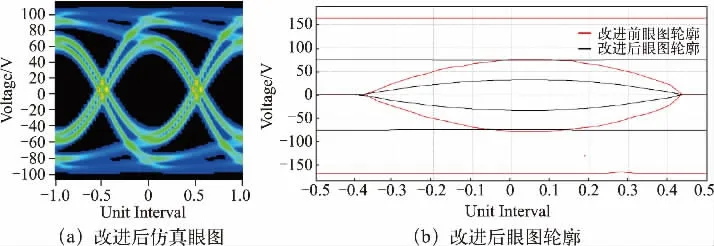

按照改进后的方案建立仿真模型,改进后仿真眼图如图4 所示。从图4 可以看出,改进后眼图眼宽与改进前相当,眼高较改进前低,改进后眼图的张开程度较小,信号质量较差,PCB 改进方案需优化。

图4 改进后仿真眼图

5 改进方案的优化设计

由信号完整性理论可知,一条链路的好坏是由主链路的插入损耗、回波损耗和周围信号对主链路的串扰决定的。所以本次优化的目标是减少链路插入损耗、回波损耗,减少周围链路对主链路的串扰。

全链路的插入损耗由走线、过孔、连接器和电容等造成,改进方案的信号走线以最短原则为准,且与原方案长度相当,无优化空间;连接器、电容为链路必需且未更换,无优化空间;过孔数量、层叠与原方案不同,有优化空间。

过孔是PCB 上的一个重要的阻抗不连续点[8]。它的存在会对高速信号的传输产生影响,包括信号上升时间延长、传播速度减慢等。这是由过孔的寄生电容和电感所导致的。

过孔的寄生电容C 可以通过式(1)进行估算,

其中:K 为常数,与电路板的厚度和介电常数相关;D1为焊盘直径;D2为反焊盘直径。

过孔的寄生电感L 可以通过式(2)进行估算,

其中:h 为过孔长度;d 为过孔直径[8]。

通过式(1)(2)可以看出,过孔的寄生电容与反焊盘直径、焊盘直径、印刷板参数相关;过孔的寄生电感与过孔长度和过孔直径相关,可以通过优化过孔结构来降低过孔长度和过孔直径对寄生电感的影响。同时,过孔残桩(为过孔中不用于连接信号线的部分)会增加过孔的寄生效应,使得阻抗突变更为明显,信号的衰减增大[9-10]。因此,在高速PCB 设计中,为保证信号传输质量,应尽量减少使用不必要的过孔。选择过孔时,应尽量使孔径较小、焊盘尺寸较小、反焊盘尺寸较大,同时去掉非功能焊盘,选择不带过孔残桩或使过孔残桩尽可能短。

基于以上思路对改进方案进行优化:RX 链路去耦电容放置在顶层,导致增加一个过孔,因此将去耦电容放置于底层以减少过孔;减小TX、RX 链路过孔的孔径,由0.254 mm 减小到0.203 2 mm;减小焊盘尺寸,增大反焊盘尺寸;采用背钻技术(背钻孔径为0.304 8 mm)将过孔残桩钻除。

串扰主要受周围通道的信号特别是高频信号的影响[11]。光模块周围仅存在高速链路及I2C 低速信号。为减少串扰,增大了高速链路与I2C 信号的距离,在高速链路的重合处尽量采用十字交叉的形式。

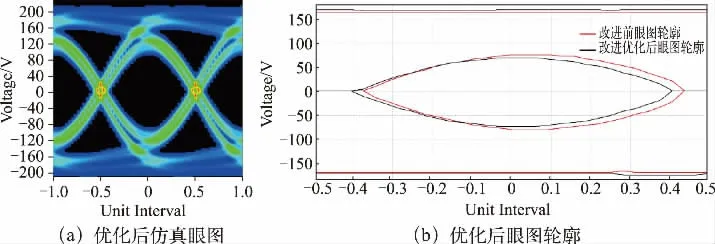

经过上述针对信号完整性的分析及优化后重新进行仿真,改进优化后的眼图仿真结果如图5 所示。从图5 可以看出,信号质量较初步改进方案得到改善,眼高及眼宽与改进前相当,可以根据该改进优化后的PCB 设计方案进行生产。

图5 改进优化后的眼图仿真结果

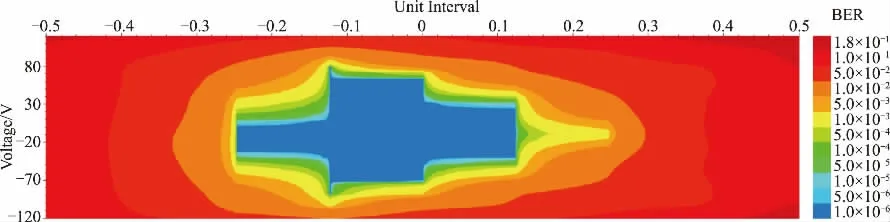

万兆以太网卡改进优化后,对高速链路进行测试,改进优化后万兆以太网卡实测眼图如图6 所示。从图6 可以看出,方案优化后眼图眼高及眼宽与改进前相当,信号质量与改进前相当。结果表明,本次改进在符合用户需求的前提下,使关键链路信号质量、误码率达到了设计要求。

图6 改进优化后万兆以太网卡实测眼图

6 结论

信号完整性在高速PCB 板的设计中非常重要,高速链路的走线、过孔、PCB 叠层设置等都会影响信号质量,设计难度很大,传统设计方法往往需要改进数次才能达到要求指标。本文在万兆以太网卡改进过程中,建立了高速链路的仿真模型,基于该模型对改进方案进行优化设计,实测眼图结果证明改进一次成功,从提出改进需求至改进测试完成,周期仅为3 个月。本文的设计改进方法提升了改进效率,提高了产品的市场竞争力,对高速PCB 的设计优化具有一定的参考意义。