基于漏电流补偿技术的超低漏电模拟开关

2023-01-02唐毓尚

唐毓尚,王 瑶,刘 俊,李 平

(贵州振华风光半导体股份有限公司,贵阳 550018)

1 引言

现有模拟开关[1-3]的实现中常用互补开关电路,即CMOS互补模拟开关[4],该开关由2部分晶体管构成,一个PMOS晶体管(P1)和一个NMOS晶体管(N1)。互补模拟开关中,P1、N1的栅极控制信号通常是互补反相信号,其电位的高、低决定了模拟开关的开启和关断。

常用模拟开关电路PMOS晶体管衬底为N阱,一般情况下,其接最高电位VDD,NMOS晶体管衬底为P-sub,其始终接最低电位VSS。在实际电路设计中,CMOS模拟开关电路衬底和源、漏端存在寄生PN结二极管,从而存在PN结二极管反向漏电流,过大的漏电流会使得输出保持信号随着时间而衰减,使信号保持精度降低,从而影响现代控制系统采样电路的采样精度。基于以上问题,本文开展了漏电流补偿技术的研究,采用漏电流补偿电路技术,实现了超低漏电流的模拟开关,提高了输出信号保持精度。

2 超低漏电模拟开关的设计

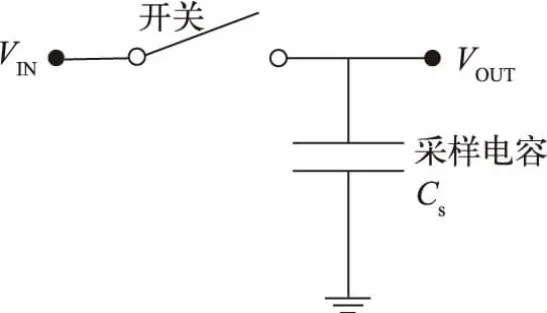

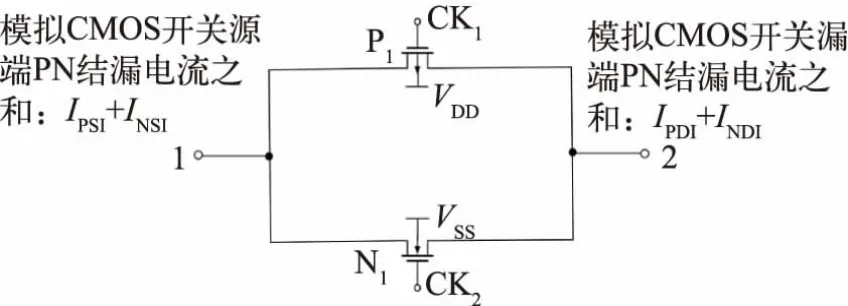

模拟开关的漏电流会影响信号输出端的信号保持精度,采样原理如图1所示,当输出信号VOUT应用于信号采样电路时,过大的漏电流会使得输出保持信号随着时间而衰减,使信号保持精度降低,从而影响现代控制系统采样电路的采样精度,因此互补模拟开关的漏电流问题亟待解决。设计的CMOS互补模拟开关电路如图2所示。

图1 采样原理电路

图2 CMOS互补模拟开关电路

该模拟开关采用PMOS和NMOS晶体管互补开关结构,包含互补开关PMOS晶体管P1和NMOS晶体管N1,P1的源端和N1的源端相连接且作为模拟开关的模拟输入端1,P1的漏端和N1的漏端相连接且作为模拟开关的模拟输出端2,P1的栅端接时钟控制信号CK1,N1的栅端接时钟控制信号CK2,CK1和CK2互为反相时钟信号,用于控制模拟开关的开启和关断,P1的衬底接最高电位VDD,N1的衬底接最低电位VSS,保证开关电路在整个动态传输范围内P1、N1源端和衬底不会正向导通,且保证动态信号的全范围传输,图2中电流IPS1为晶体管P1衬底到源端的PN结漏电流,电流INS1为晶体管N1源端到衬底的PN结漏电流,电流IPD1为晶体管P1衬底到漏端的PN结漏电流,电流IND1为晶体管N1漏端到衬底的PN结漏电流。端口1输入电流I1=IPS1+INS1,端口2输入电流I2=IPD1+IND1。

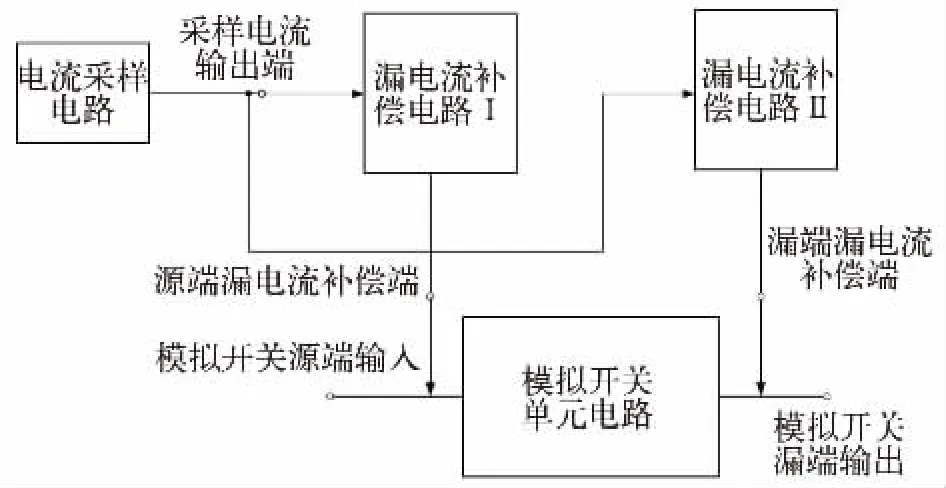

本文采用漏电流补偿电路补偿P1、N1的源漏PN结漏电,实现超低漏电流的模拟开关,提高输出信号的保持精度。漏电补偿设计原理如图3所示,将电流采样电路所采样的衬底到源漏端的漏电流输出到漏电流补偿电路,按采样电流与模拟开关电路开关管衬底到源漏端PN结漏电流的比例进行电流补偿,从而实现漏电流补偿,提高输出信号保持精度。

图3 漏电补偿设计原理

根据图3所示的设计原理实现的超低漏电模拟开关电路如图4所示。其电流采样电路由电流采样PMOS晶体管P2和电流采样NMOS晶体管N2构成,P2晶体管的栅极连接源极与漏极,并与N2晶体管的对应极(栅极、源极与漏极)连接,图4中,VEE为负电源,漏电采样电流为晶体管P2衬底到源、漏端的PN结漏电流IP2和晶体管N2源、漏端到衬底的PN结漏电流IN2之和IC。

图4 超低漏电模拟开关电路

漏电采样电流经过由晶体管P3、P4和P5组成的镜像电路,按比例β放大IC到端口1和端口2,补偿CMOS开关漏电流。镜像放大倍数β计算方式如下:

通过电流比例得到放大倍数β,从而可以得到漏电流补偿电路中P3和P4的晶体管尺寸比例,具体比例关系见式(2):

其中,W为MOS晶体管的沟道宽度,L为MOS晶体管的沟道长度。

图4中P1、P2、P3、P4、P5使用相同类型的PMOS晶体管,N1与N2采用相同类型的NMOS晶体管,通过匹配的晶体管尺寸比例,理论上可以在CMOS模拟开关1、2端头实现零电流漏电。

该款超低漏电模拟开关整体电路包括2路单刀双掷模拟开关,通道电路除了上述的互补CMOS开关电路、漏电流补偿电路外,还包括电平转换电路和开关驱动电路[5]。

3 仿真与测试验证

电路采用国内40 V高压CMOS工艺,能够提供高压PMOS晶体管、高压NMOS晶体管、高压隔离NMOS晶体管,可以满足本设计集成器件的需求。基于该工艺平台,利用业内EDA软件对本设计进行仿真验证,无漏电补偿和有漏电补偿2种情况下CMOS开关端口1、端口2输入漏电流与温度之间的仿真曲线如图5所示,其中VS为正电源。仿真结果显示,高温下无漏电补偿时CMOS开关本征漏电呈指数性增大,125℃时漏电达到22.5 nA;采用漏电补偿之后,端口输入漏电流得到极大改善,降低到1.5 nA以下。从图5中还可以看到,在全温度范围内,补偿后端口输入漏电流平缓稳定,漏电温漂降低到大约6 pA/℃,极大地提高了温度稳定性。

由图5可见,模拟开关端口漏电流并未达到100%补偿。常温及低温下,PN结漏电流非常小,为pA级,因此,漏电补偿电路主要用于补偿高温下模拟开关产生的漏电。采样电路所采样的电流通过漏电补偿电路进行等比例补偿,按照理论分析,补偿精度应达到100%,但漏电补偿电路本身带有额外的漏电流,因此按比例β补偿的电流加上额外的漏电流,与模拟开关端口的漏电流相比存在一定的误差。高温下,漏电补偿电路的漏电补偿仿真误差见表1。

图5 V S分别为-10 V、0 V、10 V时漏电流与温度仿真曲线

表1 漏电流补偿仿真误差

由表1可知,补偿电路按比例β补偿到漏电补偿端的电流偏大,从而导致补偿电流比理论值稍大,但相对于模拟开关端口漏电流,额外的漏电流所占比例较小,对补偿结果影响较小,可以忽略。

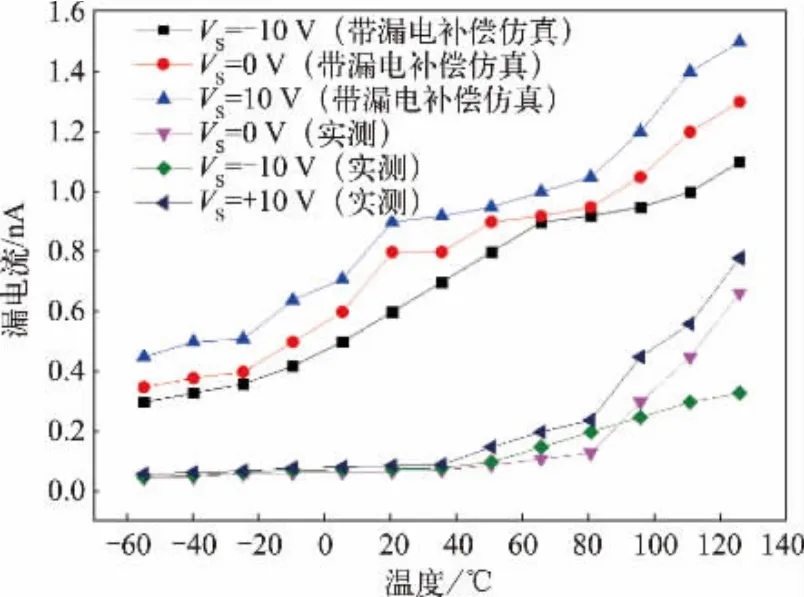

CMOS开关端口1、端口2输入漏电流与温度之间的实测和仿真曲线如图6所示,代表了该款电路采用补偿电路后漏电流与温度的关系。由图6可见,漏电实测数据明显优于仿真数据,实测高温漏电流值下降到0.75 nA,低温区漏电更小,为50 pA左右。可见,相对于无漏电补偿的CMOS开关,该电路可提升信号采集精度,有效提高了信号采集系统的信号采样保持精度,进而提升了现代设备控制系统的精度。

图6 V S分别为-10 V、0 V、10 V时漏电流与温度之间的实测和仿真曲线

图6中,实测与仿真数据不一致的主要原因是仿真验证模型不准确,对比实测数据,对模型文件进行分析并确定模型存在2个缺点。一是PN结漏电模型参数与晶体管PN结上施加的反偏电压有强作用关系,由于图4中漏电采样晶体管P2和N2的反偏电压不一致且相差数十倍,而CMOS模拟开关的PN结反偏电压呈动态变化,导致仿真漏电值偏大且离散较大。实际PN结漏电为IS[exp(VPN/VT)-1][6],其中VPN是正向PN压降,反偏情况下为负值,VT为温度电压,常温下为26 mV,因此反偏电压只要大于200 mV,PN结漏电流近似为-IS,在雪崩击穿之前,PN结漏电流基本上恒定不变,导致实测数据优于仿真。二是MOS器件模型中的指状因子在高温下能够识别,而在低温下不识别,仿真时在高温下能够很好地补偿漏电,而在低温下不能进行补偿,因此在仿真时出现低温漏电偏高的现象。经过模型优化和改进,以上缺陷可以得到解决。

4 版图

设计的超低漏电模拟开关版图和实物图见图7,其包括2路单刀双掷模拟开关[7],其中,互补CMOS开关电路采用40 V高压MOS隔离器件,实现衬底浮动并跟随源级输入变化,从而减少衬偏效应,提高导通电阻在整个输入范围内的扁平度。电路采用了漏电流补偿技术,极大地降低了模拟开关的漏电流,并且版图上通道间有隔离带及隔离层,确保通道间的隔离满足设计要求[8],电路版图总尺寸为1.98 mm×1.82 mm。

图7 超低漏电模拟开关版图和芯片实物图

5 结论

本文采用40 V CMOS工艺设计了一种超低漏电模拟开关,并采用一种创新型PN结漏电补偿技术和电路,对CMOS模拟开关输入、输出漏电流进行全温区漏电补偿,大幅度降低输入、输出端口的漏电流,实现亚纳安级端口漏电流,在-55~125℃,漏电不大于0.75 nA,并大幅提高了温度稳定性,温漂大约为6 pA/℃。本设计可提高信号采集系统的信号采样保持精度,提升现代设备控制系统的精度。