一种改进型可配置逻辑块的结构设计

2022-12-03蔡宏瑞范继聪徐彦峰陈波寅

蔡宏瑞,范继聪,徐彦峰,陈波寅

(无锡中微亿芯有限公司,江苏无锡 214072)

1 引言

FPGA 电路具有可重复配置、响应时间短、可定制、维护性强、使用领域广等优点。随着近20 年的发展,FPGA 的规模从几十万门到如今的亿门级,集成度逐渐提升,规模随之增大,结构更复杂,以实现更丰富的功能。与此同时,业界对于FPGA 的面积和延时提出了更高的要求。

可配置逻辑块(CLB)是FPGA 的重要组成部分,分布在整个芯片上。不同厂家、不同系列的芯片中CLB 的数量或结构都是不同的。CLB 的优劣将对整个FPGA 芯片的性能产生巨大影响。VPR(Versatile Place and Route) 平台是由多伦多大学开发的一个用于FPGA 结构设计的计算机辅助工具软件, 它可以对FPGA 的结构进行评估。VPR 团队提出了一种经典的学术CLB 结构[1]。商用领域中CLB 在实现特定功能时有优秀的表现,但也占用了更大的面积。针对CLB 的设计与建模层面的问题,本文提出了一种改进型的CLB 方案,选用基准测试集的部分电路进行实验,测试了该CLB 的性能。

2 可配置逻辑块结构

2.1 学术界的经典CLB

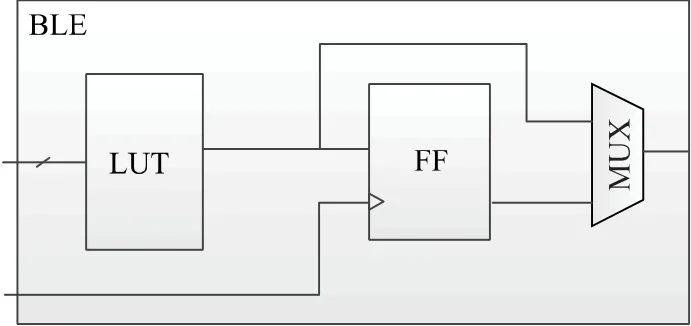

学术界的CLB 由多个相同的基本逻辑单元(BLE)连接组成,BLE 的结构如图1 所示,其包含查找表(LUT)、多路选择器(MUX)和带有时钟端的触发器(FF)各一个,以及3 部分之间的连接线。随着技术的发展,CLB 加入了进位链,可以实现快速进位功能,提高了运算效率。LUT 的SRAM 也可作为存储器使用,用于实现随机存储或移位寄存等。LUT 可直接输出,也可经过触发器之后再输出。这意味着BLE 结构允许实现时序逻辑或组合逻辑,但两者互斥,原因在于MUX 端的选择来源于配置位,不允许同时进行多选。VPR 工具的基准架构中提供了此类最基本CLB 的文档介绍和建模代码[1]。

图1 BLE 的结构

2.2 改进型的CLB 简介

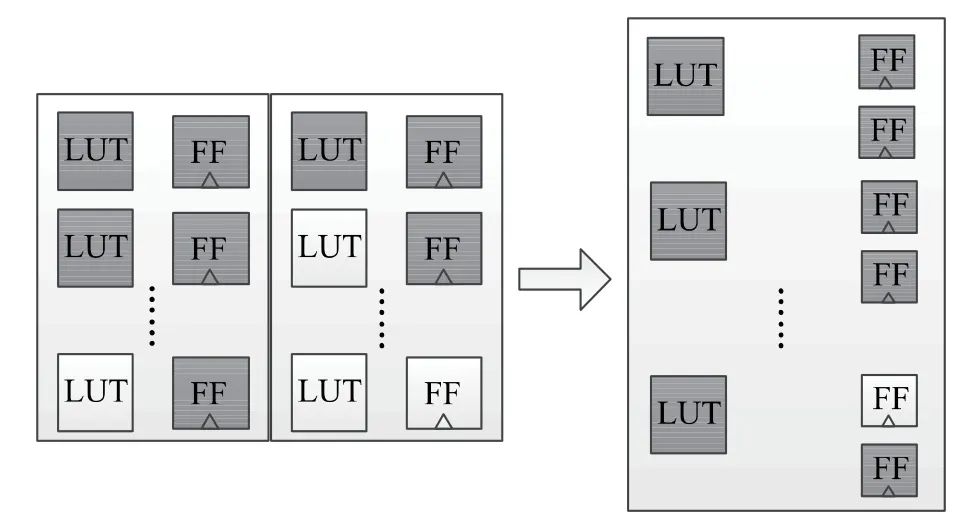

对于传统模块,每个LUT 可以选择组合逻辑或时序逻辑。目前更多的电路设计采用同步时钟,这就导致映射在FPGA 时CLB 的利用率不高,造成资源浪费。改进前后CLB 的利用率如图2 所示,深色部分为打包后用到的子模块。在箭头左侧的结构中,由于寄存器数量不足,故必须映射到2 个CLB 里,且能够看出第2 个CLB 的利用率较低;而在右侧的结构中,由于寄存器数量增多,可以在同一个CLB 中实现该电路。现代主流厂商的架构也是增加了每个基本逻辑单元所对应的寄存器数量,例如Xilinx 的每个LUT 对应2 个FF,而Intel 公司的每个自适应逻辑模块更是对应4 个FF。为此,针对CLB 模型进行改进,设置了更多的输出端口,每个LUT 对应2 个寄存器以提高利用率。

图2 改进前后CLB 的利用率

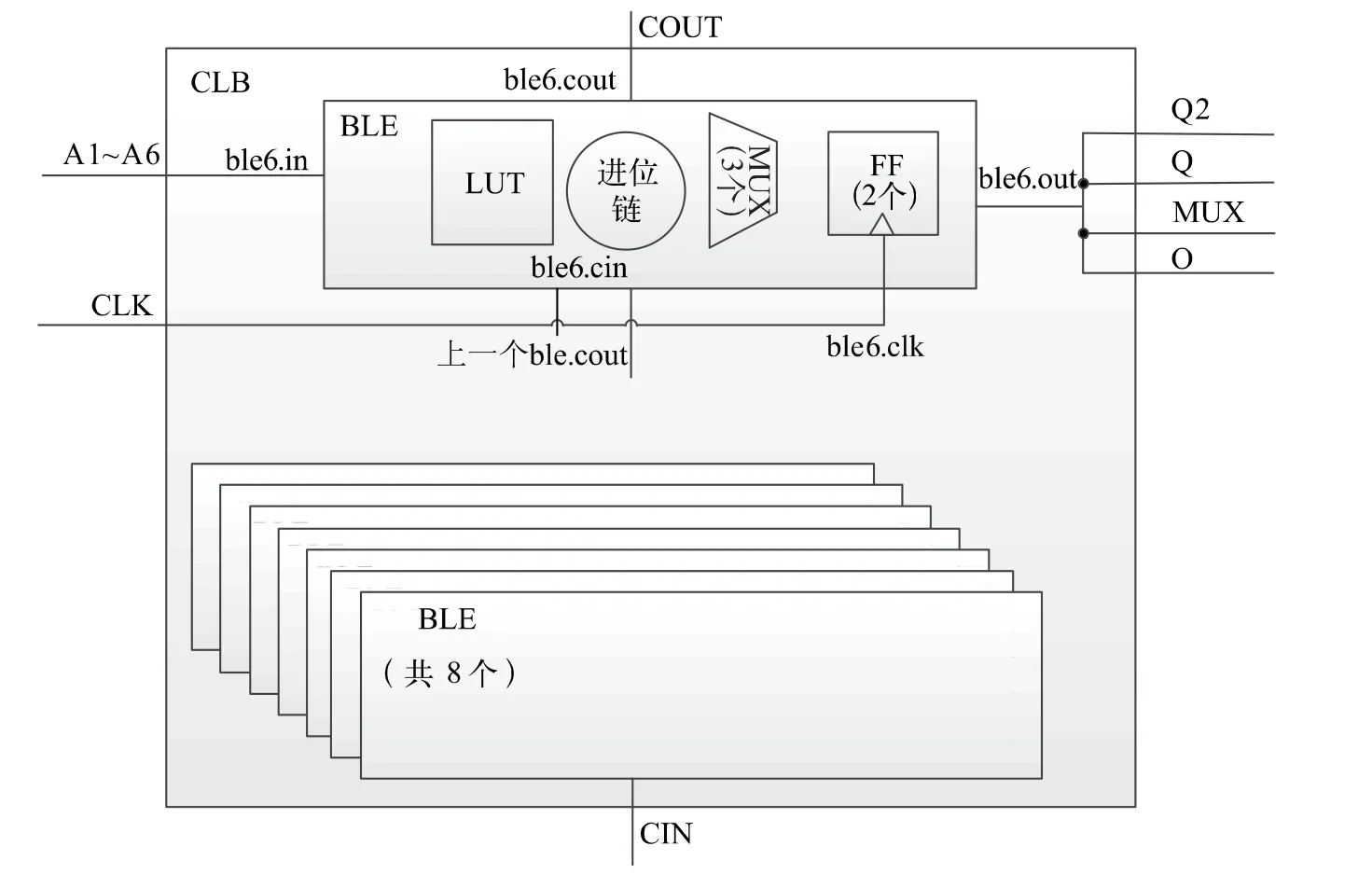

每个改进型的CLB 具有8 个BLE,改进型CLB的结构如图3 所示,用大写字母A~H 来表示8 个BLE。本文的CLB 结构具有可拆分的6 输入LUT,1个纵向的进位链,3 个选择器,2 个带有时钟的FF。BLE 的输入部分有6 个,对应LUT 的6 个输入端口。输出部分有4 类,从下往上分别为经LUT 后直接输出(O)、经过MUX 直接输出(MUX)、经过2 个FF 后输出(Q 和Q2)。

图3 改进型CLB 结构

BLE 的具体连接关系如图4 所示。左侧的LUT为可拆分LUT,能作6 输入1 输出,也可作5 输入2输出。当采用6 输入时,输出端只有单个O6;作为可拆分5 输入时,未使用的A6 端口应置为高电平,此时输出端有O5 和O6 2 个端口。对于快速进位链而言,各个BLE 之间采用级联,即下一级BLE 的输出端COUT 连到上一级的输入端CIN。建模时将内部视为黑盒,而无需探索内部专用进位逻辑的连接方式。进位链的3 个输入部分为S0、DI0、CIN0,2 个输出部分为CO0 和O0。每个BLE 中有3 个MUX,上方2 个与FF 相连的为时序逻辑,最下端的MUX 用于组合逻辑。组合逻辑可直接输出,根据配置属性来选择LUT的O5、O6 端或进位链的2 个输出端。其他2 个MUX不能直接输出,分别接入2 个触发器的输入端D。AQ2和AQ 都是触发器的输出端,受时钟的边沿影响。

图4 BLE 的具体连接

3 VPR 流程与建模

3.1 VPR 简介

VPR 是一款学术界通用的布局、布线软件,根据电路和架构描述文件,综合之后进行映射、打包、布局、布线,并对该类架构进行评估[2]。VPR 的输入文件有2 种,一种是Verilog 电路,另一种是可扩展标记语言(XML)格式的FPGA 架构描述文件。

VPR 的主要步骤包括逻辑综合、工艺映射、打包、布局、布线、性能评估[3]。逻辑综合将行为级电路综合为网表格式,工艺映射则是将综合完成的网表在给定FPGA 上进行映射。打包意味着将FF 和LUT 进行配对并封装为基本逻辑单元[4];布局则是确定所使用模块的位置,主要基于模拟退火算法[5];布线的目的是确定互连通路。布局、布线为整个流程的关键阶段,将决定性能的优劣。如果性能不满足或者超出约束范围,则需要重新布局、布线,直到符合条件为止。所有流程完成后,VPR 将输出各个阶段的报告以及总体表现的结果。

3.2 建模文件

建模工作指对于给定的FPGA,对其每一个子模块进行语言描述,本章重点介绍与CLB 相关的部分,即BLE 中的每一部分和互连线。XML 为文本形式,将信息存储在标签之内,标签的起止点用尖括号表示,标签之间可以进行嵌套和分层[6]。早期的架构评估使用参数化方法,即将关键信息用参数表示。但随着FPGA 集成度和复杂度的提升,已有的参数无法准确描述芯片特性,故参数化的方法目前已基本被淘汰,而采用XML 的格式来描述[7]。

VPR 分析建模文件以获得芯片的通道、开关,得到相应的逻辑资源与布线资源图[8-9]。若描述文件出现错误,则无法解析而导致流程无法完整进行。整个架构文件包含了模块信息、布局信息、芯片整体信息、开关信息、线段信息和模块信息(CLB 和I/O)[10]。

建模文件的最高层定义了CLB 级的输入、输出端口。CLB 内包括了8 个BLE。BLE 定义了2 种模式,分别叫做LUT6 和LUT5×2,含义是6 输入LUT 和双-5输入LUT,其中进位链部分只在LUT5×2 中生效。BLE也描述了输入、输出端口个数、连接关系、互连线之间的延时、建立保持时间等参数。

4 实验结果与分析

本文选取VPR 中的基准电路集部分Verilog 电路在Linux 平台进行测试,与第2 章的传统CLB 架构相比较,探索改进后的架构表现。基准电路来自于7 个不同的应用领域,其代码文件的大小、输入输出个数和复杂度均有较大跨度,具体的基准电路信息见表1。为了避免其他事项干扰,实验采用如下规则。

表1 用于测试的基准电路信息

(1)芯片长宽相等,布局为四周是输入、输出板块(I/O B),中间填充CLB,目的是防止其他模块对结果产生干扰。芯片规模受电路的影响,如果规模不足以实现该电路,VPR 工具将自动扩充。

(2)所选布线资源相同,选用含有抽头的4 倍线;单位长度的电阻值、电容值、开关信息相同,约束条件均为默认值。

(3)每一个CLB 都包含8 个BLE,BLE 中LUT 的输入数为6,连接线的延时数值相同或等比例设置。

(4)由于本文提出的CLB 结构包含2 个FF 和3个MUX,理论上面积应略大于传统的CLB 模型。根据各个子模块仿真的数值,实验时将改进后的CLB 单个面积设为学术型CLB 的1.1 倍。

实验对于所需规模、逻辑块面积、布线面积、总面积、延迟、所用CLB 数做了统计。由于不同电路的数量级差距大,故本文选取改进后的结构与传统CLB 相关参数的比例作为纵坐标值;横坐标的含义是7 个Verilog电路,用序号表示(与表1 的最左列对应),如图5 所示。

图5(a)为所需规模大小,图5(b)为该电路在不同架构下所使用的CLB 数量。改进型结构的CLB 数量平均为传统结构的75.12%,由于结构更为灵活,同一电路在打包过程中所需要的CLB 个数更少,进而导致规模更小。这一点在组合逻辑或寄存器较多的电路用例中(序号3、4、6、7)比较明显。

图5(c)为延时对比。延时的基本单位为纳秒,依旧用两者的比值来表述。由于多出19 个输入、输出端口,内部连线更为复杂,互连线增多,修改后结构的延时也略大于传统架构,平均比例为108.86%。

面积的计算单位叫做最小宽度的晶体管面积。从图5(d)可以看出改进后的结构在面积层面上具有明显的优势,平均节省了12.95%,这是因为逻辑块的面积大大降低。序号2 和5 的电路浮动较大,因为序号2和5 涉及到数据存储部分,而实验的FPGA 只有CLB和I/O 部分,未加入存储相关模块,所以用了大量CLB作为存储单元,因此面积相对较大。

图5 改进型结构与传统结构的性能对比

5 结论

本文提出了一种改进型CLB 的结构,增加了输入、输出端口和寄存器个数,并优化了CLB 内部的连接关系。在VPR 平台进行建模,该文件能正确地被CAD工具解析。通过不同基准电路的测试,根据实验结果可得知,在牺牲了一定延时的情况下,电路映射后的CLB 利用率显著降低,在总面积上也得到了优化。