基于级联步进延时的顺序等效采样方法及实现

2020-11-13李海涛阮林波

李海涛,阮林波,2,田 耕,2

(1.西北核技术研究院,陕西 西安 710024;2.强脉冲辐射环境模拟与效应国家重点实验室,陕西 西安 710024)

0 引言

采样技术广泛应用于数据采集,是数字示波器、频谱分析仪、探地雷达、防撞雷达、电缆测试仪等诸多领域的关键技术之一。采样技术分为等效采样和实时采样。其中,等效采样又分为顺序等效采样和随机等效采样。顺序等效采样具有原理简单、等效速度快的优点,采样点以时间为顺序。等效采样波形易于恢复。基于以上优点,顺序等效采样被深入研究并广泛应用。

目前,国内对于如何提高顺序等效采样率这一方向的研究颇多,重点在于产生一个延时范围大、延时步长小、相位抖动小的精密延时电路。方广有等采用了模拟的斜坡式步进比较延时的方法产生步进延时,最高等效采样率达到125 GS/s[1];但在工程实现时,模拟步进延时电路存在稳定性较差、温漂难以控制、Δt一致性较差等问题。李太有等采用了现场可编程门阵列(field programmable gate array,FPGA)内部的锁相环(phase locked loop,PLL)产生了数字步进延时电路,可以实现8 GS/s的顺序等效采样率[2]。但FPGA内部的PLL存在抖动较大、稳定性差等问题。朱国富等[3]和张亮亮[4]等采用了数字延时芯片的方法。数字延时芯片包括了安森美的MC100EP系列、ADI的AD9500系列、Micrel的SY89296系列等。以上芯片的最小延时步长为10 ps,最高等效采样率达到了100 GS/s,但都存在延时范围较小的问题,限制了应用范围。

1 级联步进延时

顺序等效采样的含义是:针对周期性信号,信号过触发点后,在信号的不同周期、不同相位进行采样;信号不同相位之间的采样数据时间关系是确定、已知的;根据相位关系顺序排列采样数据,得到一个时间展宽的重构波形。实现顺序等效采样的核心是获得一个针对周期信号的、稳定的步进延时系统。该步进延时系统可以将临近两个采样时钟时间间隔稳定为(Tdata+Δt)。Δt是时间间隔(即时间差),其倒数为等效采样频率[1]。

根据顺序等效采样的理论,无论采取哪种步进延时信号的方法,只要相邻两个采样点之间的时间差Δt越小,所得的顺序等效采样频率就越高。因此,产生一个稳定的时间差Δt非常重要[2]。顺序等效采样原理如图1所示。每个信号周期被顺序采样一次,最后通过顺序组合采样数据重构波形,得到时间展宽N倍的信号波形。目前,常用的步进延时信号的产生方式很多,可以细分为两大类:一类是模拟电路方法,另一类是数字电路方法。

图1 顺序等效采样原理图Fig.1 Principle of sequential equivalent sampling

模拟电路步进延时原理如图2所示[1,5-6]。模拟电路主要由快斜波发生器、慢斜波发生器(也可以是阶梯波发生器)和比较器等部分构成。理论上,可以通过改变慢斜波和快斜波的斜率差,进而改变时间差Δt。因此,只要降低时间差Δt,就可以显著提高顺序等效采样率。但是,在工程实现时,很难达到高精度的时间差Δt。这是由于模拟电路的固有缺点导致的,包括模拟电路稳定性较差、温漂难以控制等。

图2 模拟电路步进延时原理图Fig.2 Principle of analog circuit step delay

专用的可编程数字延时芯片可以克服以上困难,但是增加了控制逻辑的复杂度[2-4,7-9]。目前,有商用的可编程数字延时芯片可供选择,例如ADI公司的AD9500等、ON Semiconductor公司的MC100EP195等、Micrel公司的SY89296等。以上可编程延时芯片内部集成了步进延时电路,并且可以对步进延时进行校准。数字延时芯片作为步进延时的核心芯片,具有稳定性好、使用方便等优点;缺点是会有一个固定的芯片传输延迟时间tpd,而且总的延迟时间小,需要通过芯片的级联使用增加总的延迟时[4]。但是,级联延时芯片是有数量限制的,使用级联方法增加的延时也十分有限。在工程实现时,为了满足不同的数据采集系统的要求,不仅需要步进延时步长小,而且要求延时步长大小可以调节、总延时范围大。为了扩展延时系统的总延时,可以使用FPGA内部的锁相环产生一个稳定的粗延时,和细延时配合使用。这需要精确分配粗、细延时,以实现延时搭接[2,7]。还有一种商用的可编程数字延迟线,如MAXIM公司的DS1123L等,可以作为粗延时部分。同时,可编程延时芯片作为细延时部分,两者相互配合,可以实现步进延时小、总延时大的步进延时系统。

本文提出并实现了一种级联步进延时的方法。该方法采用可编程延迟芯片作为细延时部分,采用可编程延迟线作为粗延时部分,结合了细延时的延时步长小、粗延时的总延时大的特点,可以同时获得较小的延时步长和较大的总延时。级联步进延时原理如图3所示,包括可编程延迟线、可编程延迟芯片、电平转换芯片等[10]。在挑选步进延时芯片和步进延时线等关键元器件时,需要注意芯片的最小延时步长、总延时、传输延时、延时抖动等参数。

图3 级联步进延时原理图Fig.3 Principle of digital cascade step delay

粗延时单元采用了Maxim公司的可编程延迟线DS1123L,最小粗延时步长2 ns,延时256步,总延时512 ns。电平转换单元采用了TI公司的SN65EPT22芯片,主要功能是实现电平转换,把DS1123L输出的LVCMOS电平转化为细延时芯片所需的差分LVPECL电平。该芯片的随机抖动最大值为0.8 ps(25 ℃),可以最大程度地降低步进延时路径上引入的干扰。细延时单元采用了Onsemi公司的MC100EP195B可编程延时芯片,最小细延时步长10 ps,延时1 024步,总延时10 240 ps(10.24 ns)。细延时单元总延时10 240 ps(10.24 ns),粗延时单元的最小延时步长为2 ns,粗、细延时之间可实现延时范围搭接。

步进延时系统的粗延时步长、细延时步长均可以根据需要进行调节,以实现不同的顺序等效采样率。粗延时单元能产生2 ns倍数的粗延时步长,细延时单元能产生10 ps倍数的细延时步长。例如,可以将细延时的总延时设定为10 ns,则粗延时的延时步长为10 ns;也可以将细延时的总延时设定为4 ns,则粗延时的延时步长也为4 ns,可确保延时范围搭接。

步进延时系统的总延时可以通过级联可编程延迟线进行扩展,采样两片DS1123L延迟线级联,总延时达到1 024 ns;也可以选用延时步长更大的可编程延迟线如DS1023,最小延时步长5 ns,延时256步,总延时1 280 ns;还可以选用FPGA内部的锁相环(phase locked loop,PLL)实现和可编程延迟芯片的级联步进延时[2]。本文选用的可编程延迟线DS1123L,总延时为512 ns,对应的采样频率值为1.95 MHz,要求对应的采样频率值需要大于1.95 MHz即可。

2 数据采集验证板

根据以上级联步进延时系统的要求,设计了一块专用的数据采集板。该数据采集板采用了“模拟数字转换器(analog to digital converter,ADC)+FPGA”的架构[11]。ADC芯片采用ADI公司的AD9649,采样时钟频率范围3~20 MHz,孔径抖动0.1 ps rms,模拟带宽700 MHz,分辨率14 bit。FPGA采用的是XILINX公司的Virtex-5,级联步进延时系统设计如上所述。

该数据采集板采样率3~20 MS/s(该工况下ADC孔径抖动典型值为0.1 ps rms,工况最佳),对应的总延时为50~333.3 ns,可以灵活设计细延时的步长、粗延时的步长和总延时。AD9649的采样数据单端并行输出到FPGA接口,在FPGA内部完成接收、缓存和处理等操作;通过10 MB/100 MB自适应网络端口,将采样数据传输给后端计算机软件进行分析;采用自研软件分析采样数据,采样数据点数为64 000点。

基于自研数据采集板上FPGA,对级联步进延时系统进行控制。级联步进延时控制流程如图4所示。控制逻辑基于Verilog硬件描述语言设计。ADC工作采样时钟频率为10 MHz,需要步进延时系统总延时为100 ns;粗延时单元的最小延时步长设置为10 ns,总延时为100 ns;细延时的延时步长可调,可以为10 ps或者10 ps的倍数,总延时为10 ns(粗、细延时单元可以实现延时搭接)。该设计可以根据需要灵活调节细延时步长、粗延时步长,在保证粗、细延时范围搭接的前提下,实现不同的顺序等效采样率。

图4 级联步进延时控制流程图Fig.4 Control flow of digital cascade step delay

3 测试结果

为了验证设计的级联步进延时系统的可行性,测试步进延时系统的性能,基于自研的专用数据采集板,搭建了专门的试验验证平台。平台主要包括直流电源、RIGOL信号源DG5251、数据采集板、PC控制软件等,采用直流电源为数据采集板供电。需要指出的是,为了准确测试级联步进延时系统的性能,必须保证整个试验平台所有仪器使用同一个时钟源(即使用同一个频率值)。采用国产频率计SS7200进行测量后发现:信号源DG5251输出信号的标称频率值为10 MHz,实测频率值为9 999 996.79 Hz;数据采集板上的主时钟标称频率值为10 MHz,实测频率值为9 999 825.84 Hz。两者的频率实测值相差较大,需要使用统一的频率值。

验证平台使用数据采集板上的时钟源作为主时钟源,级联步进延时验证平台如图5所示。将数据采集板输出信号频率值9 999 825.84 Hz作为信号源DG5251的工作的主频率,信号源的输出信号作为ADC的待采样输入信号,采用自主研发的数据采集软件接收采样数据。

10 MHz信号20 GS/s采样数如图6所示。最小延时步长为50 ps,总延时100 ns。单信号周期(100 ns)的采样点数为2 000点(100 ns/50 ps=2 000),64 000点对应的32个信号周期,理论和实测波形一致。实测表明,步进延时步长为50 ps,顺序等效采样率20 GS/s。

图6 10 MHz信号20 GS/s采样数据Fig.6 20 GS/s sampling data of 10 MHz signal

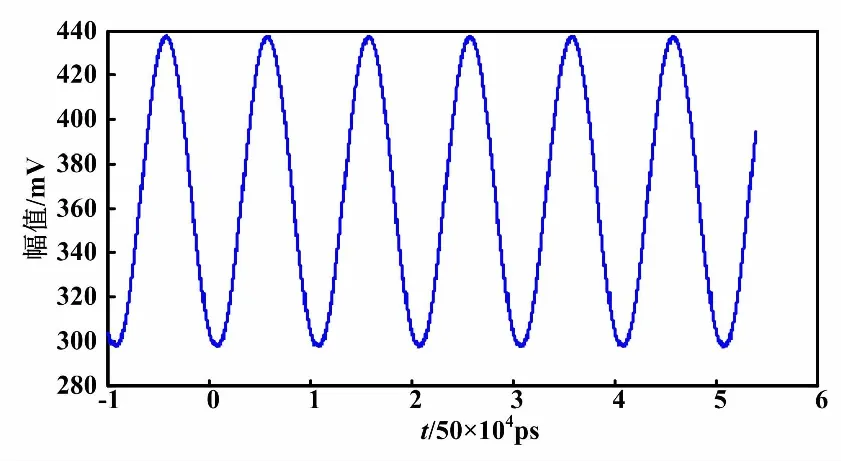

10 MHz信号100 GS/s采样数据如图7所示。

图7 10 MHz信号100 GS/s采样数据Fig.7 100 GS/s sampling data of 10 MHz signal

最小延时步长为10 ps,总延时100 ns。单信号周期(100 ns)的采样点数为10 000点(100 ns/10 ps=10 000),64 000点对应的6.4个信号周期,可见实测波形和理论符合得较好。实测表明:步进延时步长为10 ps,顺序等效采样率为100 GS/s。

通过以上结果分析,理论和实测波形两者一致性较好。观察放大之后的波形细节:波形本身平滑性和连续性较好,展示了基于级联步进延时的顺序等效采样方法的优良性能。

4 结论

本文提出一种基于级联步进延时的顺序等效采样方法,并设计了数据采集板验证该方法的可行性。测试结果表明:采用可编程延迟线、可编程延迟芯片等实现的级联步进延时,实现了信号的高精度、大范围的步进延时,最小延时步长10 ps,总延时达到512 ns,最高的顺序等效采样率为100 GS/s。

该方法易于实现,控制逻辑简单可靠,可以根据实际应用对该方法进行扩展。通过调节粗、细延时的步长,可以实现多种顺序等效采样率。结合目前商用的高带宽采样保持芯片(如HMC661LC4B、HMC1061LC5等产品),可以实现高采样率(≤100 GS/s)、高带宽(≤18 GHz)的顺序等效采样。该方法可以广泛应用于顺序等效采样系统。