一款深亚微米抗辐照芯片的设计与实现

2022-08-01邹文英谢雨蒙周昕杰

邹文英,高 丽,谢雨蒙,周昕杰,郭 刚

(1.中科芯集成电路有限公司,江苏无锡 214072;2.中国原子能科学研究院抗辐射应用技术创新中心,北京 102413)

1 引言

收发器电路是协议处理器电路与外部总线的接口,是实现正常通信的基础[1],被广泛应用于国防科技领域。随着人类对空间的探索不断深入,对应用于航天及国防领域的收发器电路要求也越来越高,其中抗辐照性能是一个重要的指标。但是未经辐照加固的收发器电路,其抗辐照能力较低,远不能满足航天及国防领域对电路抗辐照能力的要求[2]。特别是随着半导体器件的集成度不断提高,特征尺寸及工作电压不断降低,对电路的抗辐照加固设计也提出了更高的要求[2]。因此,研制辐照加固电路成为一项重要的课题[2]。

随着抗辐照加固技术的发展,出现了工艺加固、版图加固、电路加固等多种提高电路抗辐照特性的加固技术。在电路加固技术中,三模冗余(TMR)加固技术因加固效果佳而得到广泛的应用。

本文采用深亚微米CMOS 工艺设计了一款可以应用于航空航天的四路串口收发电路,同时采用工艺加固、单元加固和全电路TMR 加固等多层次抗辐照加固技术,提高了芯片的性能,使之具有较强的抗辐照能力。

2 电路设计

2.1 电路整体结构和功能

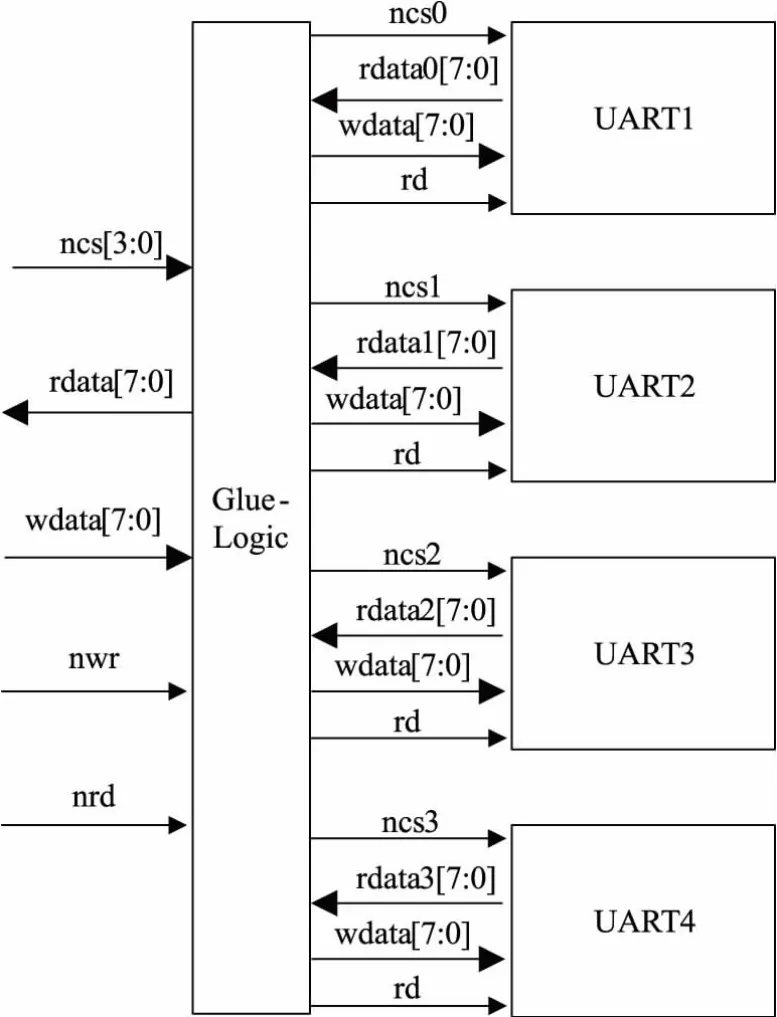

本文设计的四路串口收发器整体功能框图如图1所示。电路主要包括处理器总线的接口逻辑和四路通用异步收发传输器(UART)通讯协议逻辑。位于电路顶层的处理器总线接口逻辑与每一路UART 的总线接口逻辑通过胶连电路模块连接,以实现外部处理器对四路UART 协议模块的分别控制。

图1 电路整体功能框图

每个分立的UART 主要包含波特率发生器、总线接口、发送/接收缓冲先入先出(FIFO)和发送/接收器等模块。波特率发生器可以动态配置,作为UART收发的参考时钟。电路的发送/接收器可以灵活配置字长、校验极性、停止位长度等信息,发送和接收功能各有256 B 的缓冲FIFO,且支持直接存储器访问(DMA)工作模式。

2.2 设计流程

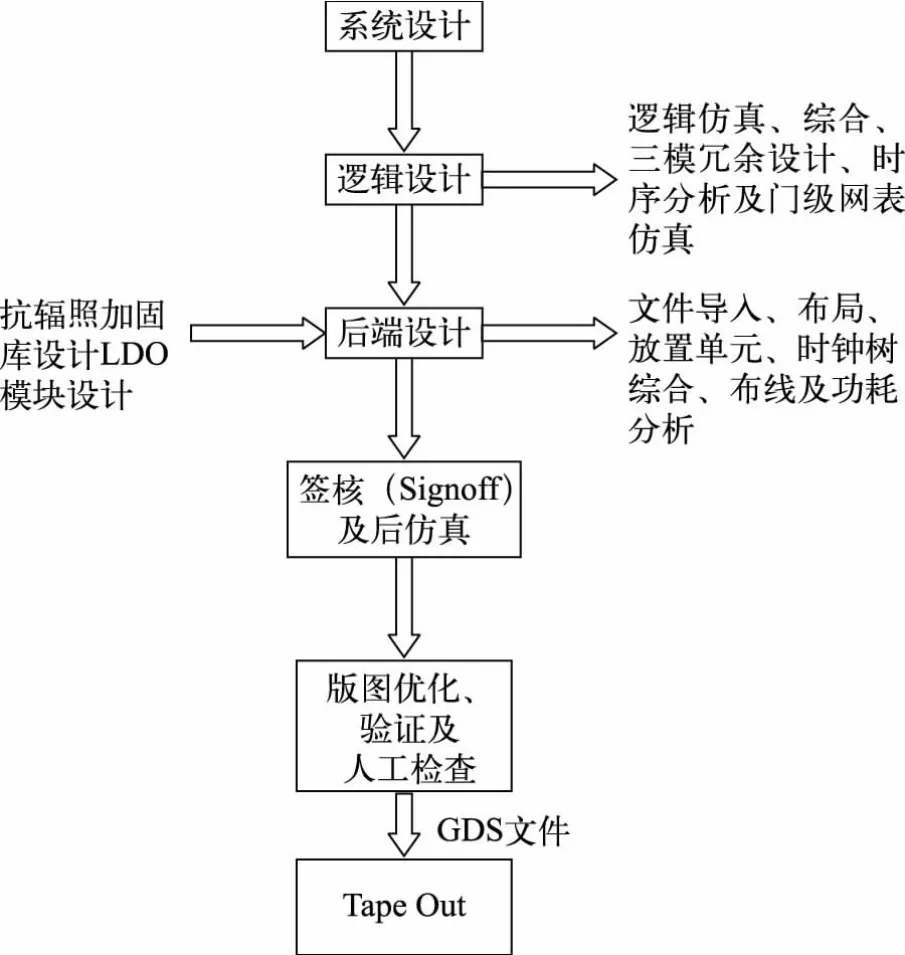

本文设计的电路由5 V 外部单电源供电,端口工作电压为5 V,内核工作电压为1.8 V,需要内嵌低压差线性稳压器(LDO)模块完成5 V 到1.8 V 的电源转换。因此,电路可以分为两个部分(见图2),即数字部分和LDO 模块。数字部分基于抗辐照标准单元库的数字半定制正向流程设计,包括系统设计、逻辑设计、后端设计、签核(Signoff)及后仿真等工作,LDO模块采用全定制设计,最终合并版图完成整个电路的设计。

图2 电路设计流程

2.3 逻辑设计

电路逻辑部分设计的输入形式是综合后的门级网表,需要在其基础上完成网表级的加固和后端设计。由于电路具有较高的单粒子翻转效应(SEU)指标,因此逻辑加固方案采用全电路TMR 设计。逻辑部分的设计内容主要是将原网表转换为TMR 网表,并基于该网表完成时序分析、门级仿真及后端设计。在设计的各阶段需要做功能一致性的验证以及TMR 的加固能力验证。

为确保设计输入网表的正确性,需要对原网表进行仿真验证。针对电路编写了涵盖全部功能的仿真平台,该平台主要包括读写寄存器、配置波特率、多种配置下的收发功能、收发FIFO 缓存功能、DMA 功能以及多路同时收发功能。

2.4 后端设计

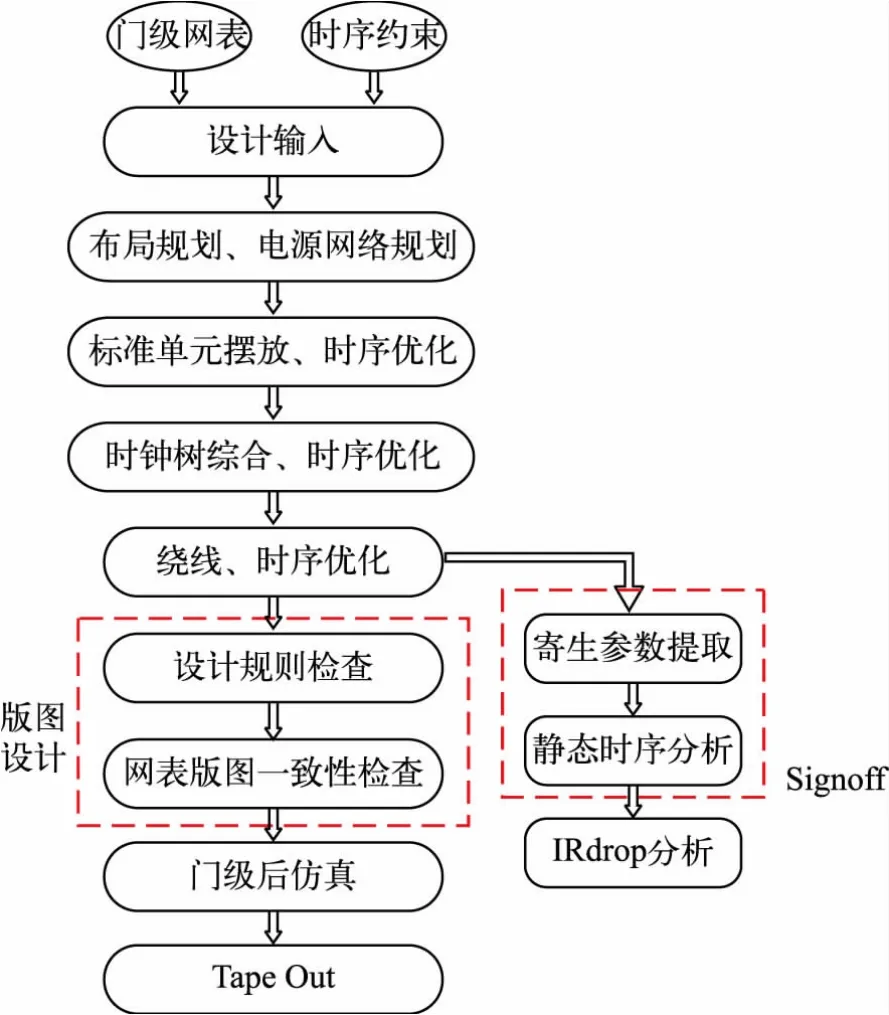

本文提出电路的后端设计流程如图3 所示,为了提高供电能力的可靠性和芯片内部供电的平衡性,在电路布局规划中根据逻辑部分的功耗评估和LDO 的负载能力仿真,在电路的上下部分并联放置了两个LDO 模块,外部5 V 电源连接到LDO 上,LDO 输出1.8 V 到内核电源环上供电。

图3 电路后端设计流程

电路采用TMR 结构,在时钟树综合过程中尽量使三路时钟平衡;设计双倍线宽和双倍线间距以减小时钟信号间的串扰[3];选择驱动能力较强的缓冲器和反相器作为时钟树的驱动单元,既满足时钟偏移及插入延迟要求,又增强时序路径的抗辐照能力。考虑重要信号优先布线原则并进行线长优化,绕线阶段采用双通孔规则以增强电路可靠性等。

2.5 抗辐照加固设计

电路总剂量加固主要采用工艺加固的方法[4]。0.18 μm 加固工艺主要对浅沟道隔离场区进行总剂量加固,通过离子注入的方式将沟道/衬底界面处的P型硅反型阈值提高,从而抑制隔离区寄生晶体管的漏电通道开启[5]。用工艺开发的方式提升NMOS 器件抗总剂量辐射能力,可明显减小版图面积及降低设计难度[5]。工艺加固后,1.8 V NMOS 抗总剂量辐射能力从加固前的100 krad(Si)达到了加固后的500 krad(Si)[5]。

在库单元加固设计方面,通过仿真确认N 管及P管有源区的距离、P 管及N 管源端到体接触的距离,保证400K 下寄生可控硅结构无法导通,以较小的面积损耗实现了单粒子闩锁效应(SEL)加固;SEU 加固采用经典的双互锁存储电路(DICE)结构[6];针对单粒子瞬态效应(SET)加固[7],为实现关键控制逻辑37 MeV·m2·mg-1的翻转指标,直接采用了内部自刷新的三模单元进行触发器加固[8]。在实现抗辐射指标的前提下,与同工艺节点的普通商用单元库相比[9],对应的速度、面积、功耗增加的损耗在30%左右。

逻辑加固方案采用全电路TMR 设计[10]。逻辑部分的门级网表包含时序逻辑和组合逻辑两大部分,时序逻辑中全部是触发器。原网表包含三组触发器,三组触发器共用同一组端口,即CK/RN/D/Q/QN 等信号只有一套。而在TMR 设计时,标准单元库的触发器内部同样是TMR 设计,但分别连接到三组端口上,即CK/RN/D/Q/QN 等信号有三套。因此,在全TMR 设计中,只需要在原网表文件上做修改,将原网表的触发器端口复制三份,组合逻辑整体复制三份,再按照原网表的关系连接起来,就实现了逻辑部分的TMR 设计。逻辑TMR 结构如图4 所示。

图4 逻辑TMR 结构

完成网表TMR 加固设计后,需要进行电路的功能验证和注错验证。网表在仿真平台上进行网表反标电阻、电容寄生参数文件仿真验证。仿真结果证明,经过TMR 加固后,电路的逻辑功能是正确的。采用如下方法进行注错验证:(1)将三模时钟中的一模设置为固定0,进行仿真;(2)将三模reset 中的一模设置为固定0(有效),进行仿真。

3 电路实现与试验结果分析

3.1 电路基本情况及实现

本设计电路是一款四通道UART 收发电路,最高工作频率50 MHz,规模75 万门,包含两个LDO 模块,采用抗辐照0.18 μm 1P6M CMOS 工艺,电路主要技术指标如下。

工作电压:端口5 V,内核1.8 V;

抗SEL 能力:75 MeV·cm2·mg-1;

抗SEU 能力:1×10-10error/(bit·d)。

该抗辐照四路串口收发电路已在华润上华有限公司成功流片,电路尺寸为6.42 mm×6.42 mm。

3.2 试验结果及分析

在中国原子能科学研究院核物理研究所及中国科学院近代物理研究所对上述电路进行抗辐照试验。分别对经过抗辐照加固的四路串口收发电路进行SEU 试验和SEL 试验,试验结果如表1 所示。

表1 单粒子事件数

观察表1 可知,经过抗辐照加固的四路串口收发电路达到了航天器件的抗辐照指标要求。试验结果充分验证了采用工艺加固、库单元加固及全电路的TMR设计能有效提高电路的抗辐照性能。

4 总结

随着航空航天的不断进步,器件的特征尺寸也越来越小,对集成电路设计提出了更高的要求,需要采用多层次的综合加固技术才能有效地提高芯片的抗辐照性能。本文介绍了一款深亚微米抗辐照四路串口收发电路,包括设计流程、逻辑设计、后端设计和抗辐照加固设计等。该电路在空间辐射条件下总线接口满足多款SOC 总线时序,波特率可动态配置,每个通道各有256 B 的收发缓冲,支持DMA 操作,功能与性能可以满足绝大部分航天需求。