高速PCB差分孔阻抗的影响因素及优化研究

2019-08-22袁为群宋建远

袁为群 宋建远

(崇达技术股份有限公司,广东 深圳 518132)

0 前言

高频高速PCB的频率已在1 GHz~77 GHz,传输速率20 Gbps以上,PCB的密度也在不断增加,保证信号完整性成为高速电路设计和制造的重点关注话题[1]。信号完整性是高速电路系统中信号未受到损伤的一种状态,它表明信号通过传输线传递后,仍能保持正确的性能和做出响应。当信号在高频下传输时,导通孔的寄生电容和寄生电感所产生的阻抗会引起信号反射、串扰或衰减等问题。实现高速PCB互连必须采用导通孔设计,导通孔是PCB设计中的常用结构[2]。因此,在高速PCB设计和制造中,如何减小导通孔寄生效应带来的阻抗是我们必须面对的问题。

本文通过导通孔的影响因素分析,并通过优化设计试验得出可以从孔径、焊盘和反焊盘三方面改善孔阻抗。在研究过程中把控深钻技术应用到孔阻抗优化设计,得到了差分孔阻抗的很好改善。

1 孔阻抗的理论分析

1.1 导通孔介绍

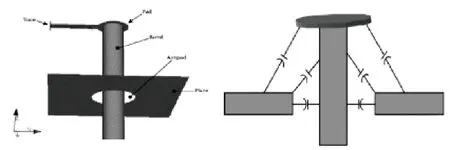

高速电路采用的元器件集成度高、速度快、引出端子多,因而PCB板上布线密度高,层数高且多在16层以上,导通孔(也称过孔)设计非常多,传输线的特性阻抗控制要求高。其中导通孔的主要功能是用于各层次之间的电气连接,即连接高多层板的不同层走线的电导体,从而构成高速互连电路。导通孔的结构主要由三部分组成:孔径(hole)、焊盘(pad)和反焊盘(antipad)。在高频高速下导通孔的信号传输会产生寄生电容和寄生电感,从而产生阻抗。导通孔模型(如图1)。

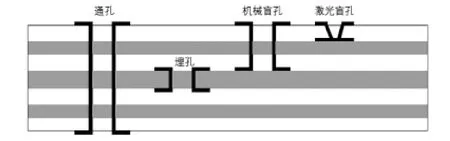

常见的几种导通孔结构和工艺有:通孔、埋孔和盲孔,盲孔包括机械盲孔和激光盲孔。通孔是PCB最常用的过孔结构;埋孔在PCB的内层构成互连电路,可以节省埋孔的上、下各层的布线空间;盲孔用于表层(即顶层和底层)线路与内层线路的电气连接,可以节省盲孔的下方(或上方)各层的布线空间。常见导通孔结构(如图2)。

在最新PCB技术中,实现盲孔的工艺方法还有:背钻和控深钻,这样不仅可以减少多次压合,而且能够实现各种深度的盲孔,大幅降低了技术难度和制造成本。

1.2 关于孔阻抗的影响因素分析

任何阻抗突变都会引起电压信号的反射和失真,这使信号质量会出现问题,只要信号的阻抗保持不变,就不会反射,也不会发生信号失真,而衰减效应是由串联和并联阻抗引起的。信号的串扰是由两相邻信号线及其返回路径之间的电场合磁场的耦合引起的,信号线间的互耦合电容和互耦合电感产生的阻抗决定了耦合电流值。因此,阻抗不仅可以用来描述与信号完整性相关的问题,还可以用来得到信号完整性的解决方案和设计方案[3]。既然阻抗突变会引起信号反射失真或者耦合串扰,我们就得从阻抗分析入手。线阻抗按照常规的阻抗软件模拟计算和控制,不在本文的讨论范围,下文主要讨论孔阻抗。

导通孔是PCB上一个重要的阻抗不连续点,当信号频率达到1GHz以上,高速信号通过时,导通孔的寄生电容会信号上升时间延长,传输速度减慢[4]。这时导通孔寄生效应就凸显出来,其估算如公式(1)。而寄生电感会消弱电源旁路电容的滤波功能,这样高频高速信号在电路板中流窜而引发串扰等问题[5],因此,过孔的寄生电感带来的危害比寄生电容大得多。

导通孔的寄生电容估算公式:

图1 导通孔模型

图2 常见导通孔结构

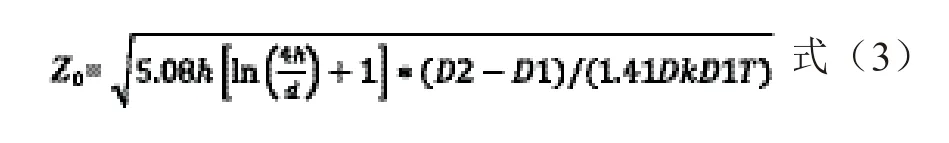

式中,C—寄生电容(pF),T—PCB厚度(in),Dk—介电常数,D1—焊盘直径(in),D2—反焊盘直径(in)。

由公式(1)可知,反焊盘和焊盘对寄生电容有着较大的影响,PCB厚度也会影响寄生电容的大小,在尽可能的情况下,减小PCB厚度。

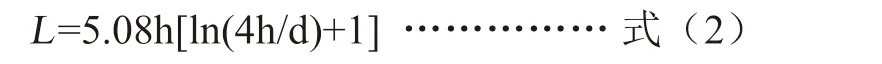

导通孔的寄生电感估算公式:

式中,L—寄生电感(nH),h—导通孔长度(in),d—导通孔直径(in)。

由公式(2)可知,导通孔的长度对寄生电感影响最大,而导通孔的钻孔孔径对寄生电感影响相对较小。改变导通孔长度的方法有背钻技术,即采用背钻技术把导通孔多余的导通部分钻掉,这样可以降低反射系数,提高传输系数和减小阻抗的不连续性[6]。背钻短桩长度不在本文讨论。

根据阻抗公式Z0=并把公式(1)和(2)代入其中,则有

由公式(3)可知,加大反焊盘D2 或减小焊盘D1,或减小导通孔直径,可增大导通孔阻抗值[7]。

2 研究方案

本文研究高速PCB的差分孔阻抗变化情况,主要是通过试验的方法来探讨导通孔的钻孔孔径、焊盘和反焊盘三种参数对孔阻抗的影响效果。要求:导通孔的孔径0.36 mm±0.5 mm,内层差分线阻抗90±5 Ω,差分孔阻抗≥85 Ω。本方案采用一款22层板作为研究对象,采用低损耗高速板材TU833,叠层结构(如图3)。

由图3可知,信号层L7、L16、L18和L20的差分孔有背钻,原因在于这些层设计有差分阻抗线。为了减小高频高速下差分孔的长度对阻抗的影响,设计背钻来控制寄生电感值,背钻短桩(stub)大小按背钻深度来管控,一般在0.25 mm范围以内。方案中,阻抗测试采用TDR时域反射计,请注意:是德的VNA网络分析仪不适合进行孔阻抗测试。

图3 叠层结构图

2.1 差分孔阻抗设计优化

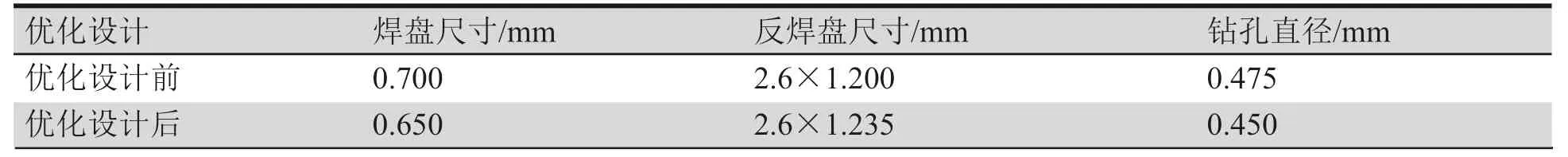

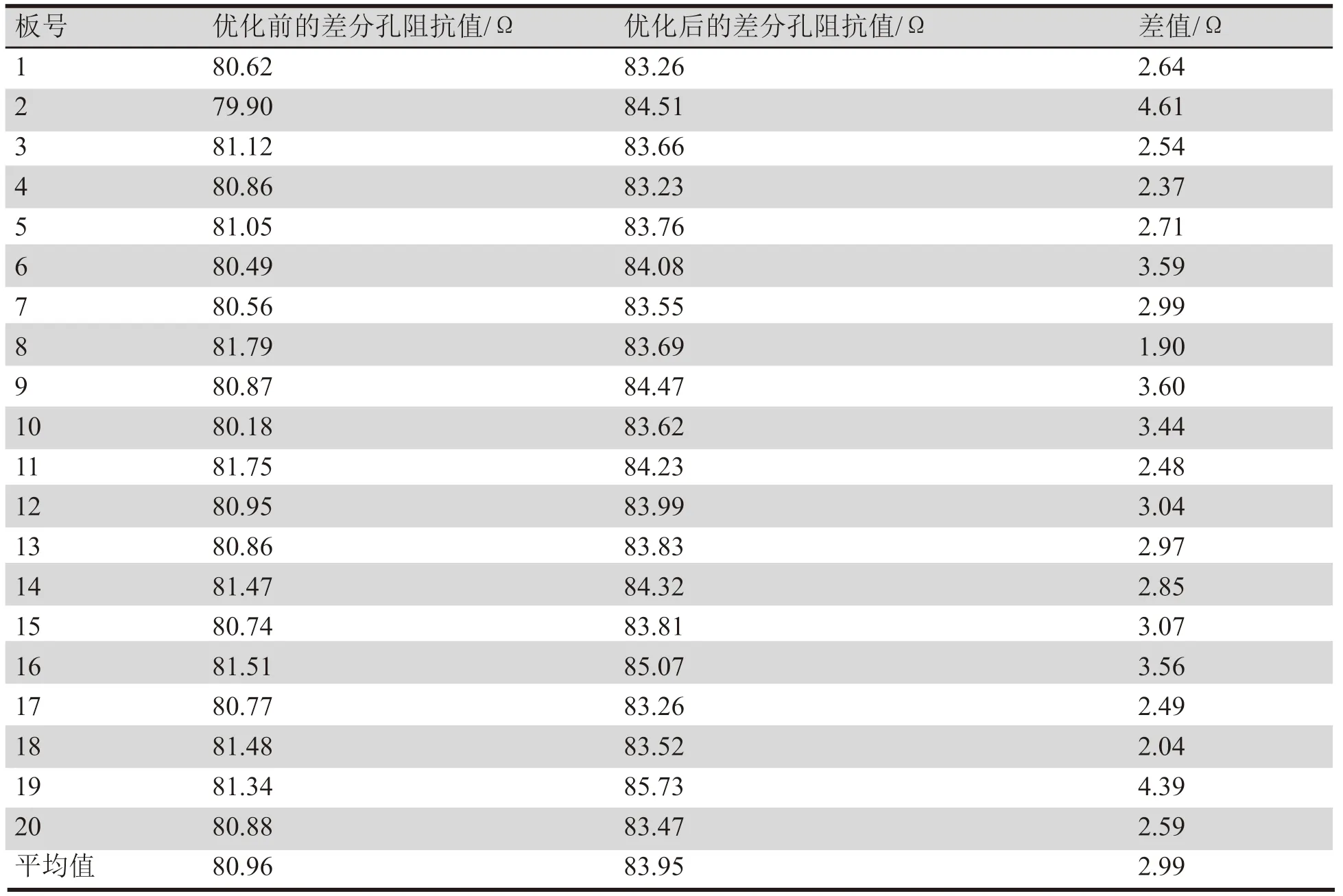

在优化设计前,孔阻抗在80Ω上下,达不到83Ω。经过分析问题出在导通孔的反焊盘和焊盘尺寸设计上,根据孔阻抗的公式,加大反焊盘和减小焊盘尺寸,同时减小该孔的钻孔直径。优化设计前后的数据(见表1)。

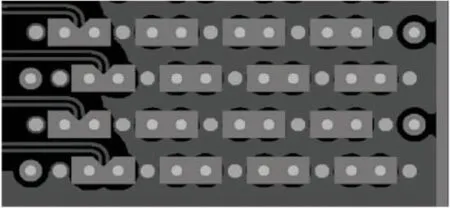

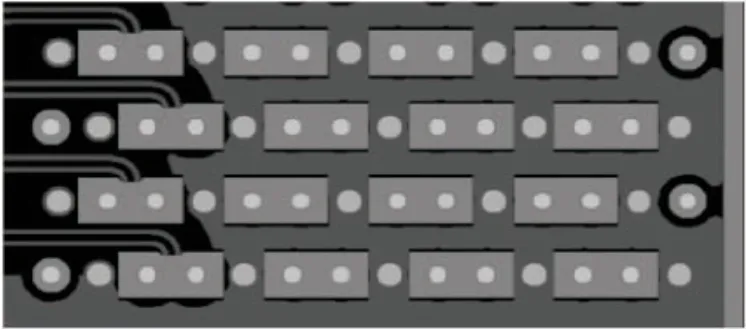

优化设计前后的导通孔线路图如图4和图5。从图示可看出,优化设计后的线路层和地层还在布局上做了一些细节上的更改。

试验板20块(pcs),进行全流程制作和阻抗测试,与优化前的20 pcs数据进行对比分析。

2.2 差分孔阻抗优化验证

减小钻孔直径、增大反焊盘尺寸和缩小焊盘尺寸,可以把孔阻抗做到83Ω之上,满足了高速PCB孔阻抗要求。以L20为例,优化设计前后的孔阻抗测试情况,如表2实测数据。通过孔径、反焊盘和焊盘优化设计可把L20层的差分孔阻抗值提升2.99 Ω。根据实测数据分析,其他层次的差分孔阻抗提升值是有些差异的,平均值基本在2~3 Ω之间(见表2)。

表1 0.36mm导通孔的优化设计参数

图4 导通孔优化设计前的电路图示

图5 导通孔优化设计后的电路图示

这样的优化设计给高速PCB制造带来很大的难度。减小钻孔,为了满足孔径0.36 ±0.05mm,必须控制电镀孔铜厚度和均匀性,这需要试验设计抓取电镀工艺参数,并检测孔径。减小导通孔的焊盘,保证不破盘,需要提升层间对准度,优化OPE冲孔、压合和钻孔的工艺参数,并检测层偏数据,以保证良好的对位能力。

2.3 实现压接孔阻抗优化的新方法

实现压接孔阻抗优化的新方法如下叙述。

2.3.1 如何实现压接孔阻抗优化

压接孔是导通孔的一种,用于安装带有压接脚的连接器(或元器件)。由于信号传输速度非常高且在20 Gbps以上,对差分线阻抗和差分孔阻抗的要求也就非常高。如上文案例中,压接孔0.36±0.05 mm,差分线阻抗90±5 Ω,差分孔阻抗≥83Ω,是通过优化孔径、焊盘和反焊盘的方式来提升孔阻抗。这样做给生产制程带来较大的难度,有没有其他的新方法呢?

根据文献研究结果,导通孔的孔径对阻抗的影响大,随着孔径的增大会引起更大的阻抗不连续性[8]。反过来说,减小孔径是可以改善孔阻抗的。这符合孔阻抗的影响因素分析结果。我们可以从钻孔大小的思路来改善孔阻抗。在满足压接脚长度的情况下(一般压接脚长度1.0 mm),把非压接端的孔做小些,以期差分孔阻抗得以提升。

表2 差分孔阻抗优化设计前后的实测数据

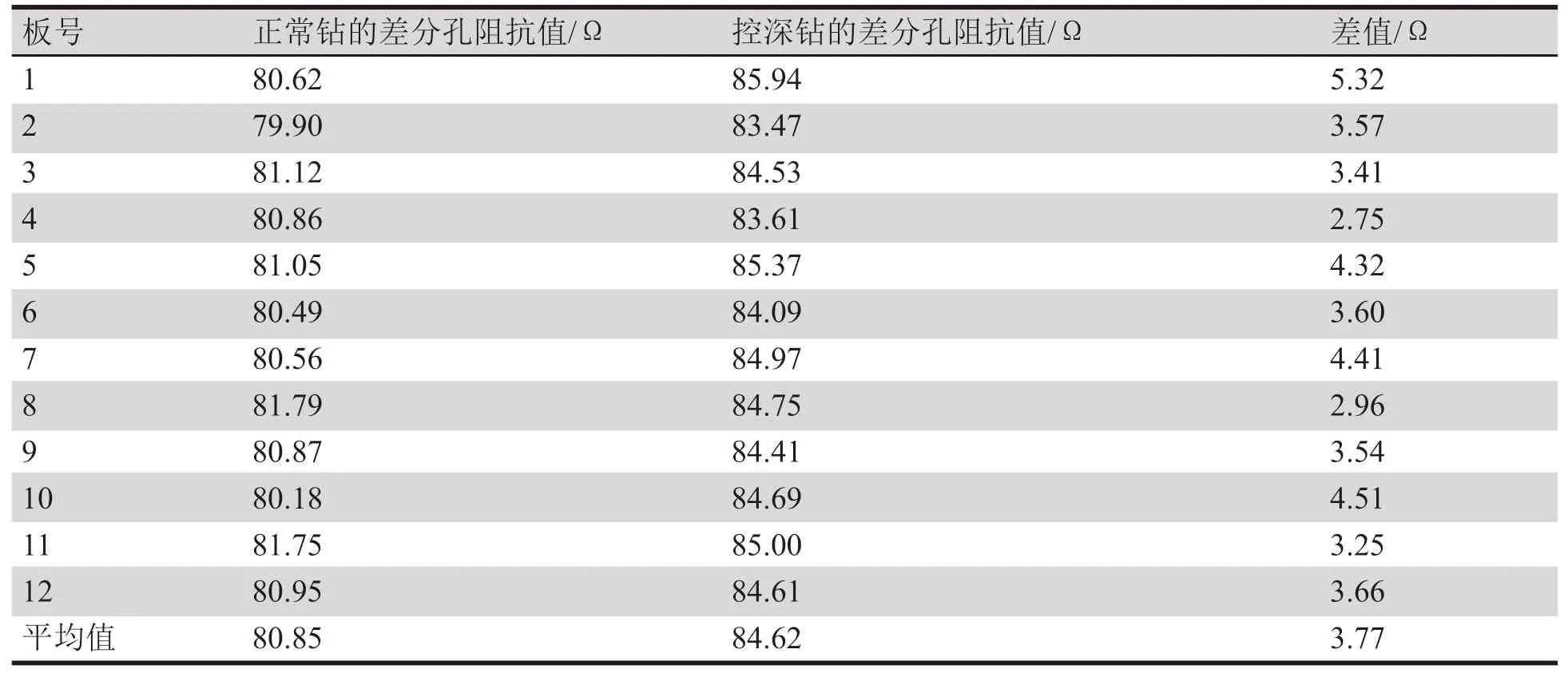

试验方案:叠层结构同前,对于压接孔0.36 mm而言,先从顶面(top)钻0.30 mm小孔,然后在同一位置钻1.2~1.4 mm深度的0.45 mm大孔,而压接孔的焊盘和反焊盘尺寸不做设计优化。

2.3.2 试验结果与分析

如上试验方案完成试验板,并进行差分孔阻抗测试。仍以L20为例,采用控深钻与原来正常钻的测试数据如表3。通过采用大小孔优化设计可把L20层的差分孔阻抗值提升3.77 Ω。根据实测数据分析,其他层次的差分孔阻抗提升值是有些差异的,平均值基本在2.5~4 Ω。

表3 差分孔阻抗有无控深钻的实测数据

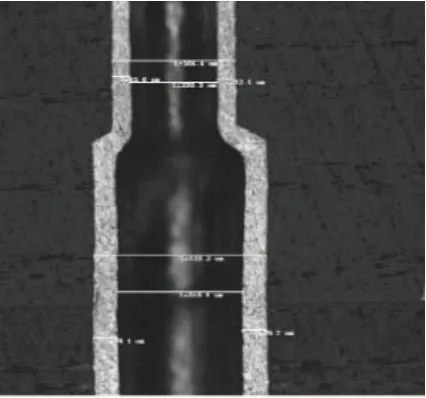

图6 大小孔切片图

采用大小孔设计和控深钻技术,电镀后的孔图片如图6。

这种大小孔在电镀上不存在技术问题,可以保证电镀孔品质。

3 结论

高速PCB是电子电路设计和制造研究的热点。通过上面差分孔阻抗设计优化和试验分析,可以得出下面结论,为高速PCB差分孔阻抗设计和制造提供了可靠依据:(1)可以从导通孔径、焊盘和反焊盘来改善导通孔阻抗,当孔径减小25 μm,焊盘减小50 μm且反焊盘增大35 μm时,差分孔阻抗可以提升3Ω。这种优化设计的方法,需要考虑工艺制程的能力,把孔设计和可制造性相结合;(2)钻孔孔径大小对差分孔阻抗有着非常明显的改善效果,而且可以适当降低制作难度。当采用大小孔设计并使用控深钻技术,可以提升差分孔阻抗约3.5Ω,能够达到同时优化孔径、焊盘和反焊盘尺寸的效果。