基于FPGA可配置任意整数半整数50%占空比时钟分频的实现

2017-02-09王兴宏张艳飞

王兴宏,涂 波,闫 华,张艳飞

(1.中国电子科技集团公司第58研究所,江苏无锡214072;2.无锡中微亿芯有限公司,江苏无锡214072)

基于FPGA可配置任意整数半整数50%占空比时钟分频的实现

王兴宏1,涂 波1,闫 华2,张艳飞1

(1.中国电子科技集团公司第58研究所,江苏无锡214072;2.无锡中微亿芯有限公司,江苏无锡214072)

基于FPGA,采用FPGA内部相移时钟,设计了一种可配置任意整数半整数50%占空比的时钟分频电路。以环形触发器电路为主要分频电路,根据各相移时钟的相位关系调整输出时钟占空比。设计结合时钟的相位关系与分频时钟周期的关键点,以多输入差分锁存结构完成输出时钟的占空比调整,最终实现整数、半整数分频。最后对电路进行了仿真验证。

FPGA;占空比;整数半整数分频;差分

1 引言

随着无线通信技术的快速发展,频率综合作为现代通信系统的核心部分,对其性能要求越来越高。在无线局域网、移动通信、卫星通信、雷达监测、数字电视等先进的电子系统中需要一个输出频率高度稳定的频率综合器来产生输出频率。分频是频率综合器的重要组成部分,它直接影响频率综合器的分辨率、频率切换速度和输出相位噪声。在现有的技术下小数分频是通过计数器计数的方法来实现的。这样对IC设计来说,需要占用很大的空间。因此现在的研究主要集中在如何设计性能良好、集成度高的结构以最大限度降低由于小数分频造成的杂散问题。

本设计的目的是克服现有实现方案存在的不足,提供一种基于FPGA[1]50%占空比可配置任意整数半整数分频实现的结构设计,使其提高集成度,避免无效的冗余设计。

2 设计方法与实现

在提及有关分频的结构时,通常会想到采用计数器,通过脉冲吞吐计数器和锁相环计数,先设计两个不同分频比的整数分频器,然后通过单位时间内两种分频比出现的不同次数来获得所需要的小数分频值。在分频整数、小数、指定占空比(比如说25%、75%占空)分频时钟,很少采用时钟本身的相位优势设计。从单独设计分频器的角度出发,似乎看起来采用计数器的设计理念要优于本设计,但要设计一款集成度很高的IC,采用本设计则更合理且更能节省资源。本设计基于FPGA,采用FPGA内部四相位相移时钟,快速定位整数分频和半整数对应的二分频时钟的周期、半周期、四分之一周期、四分之三周期位置,并采用窄脉冲来标记以上关键周期位置,多输入差分结构完成输出目标分频时钟。

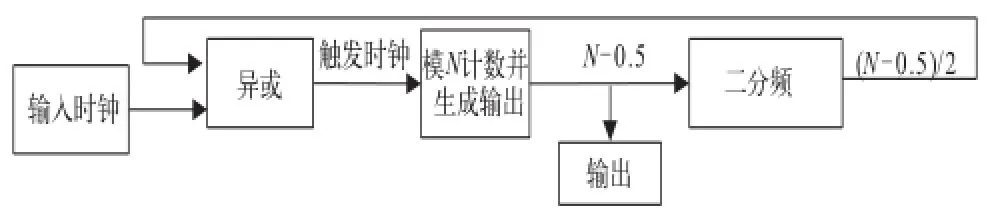

图1为传统小数分频的设计实现过程,其基本的设计思想是:进行模N的计数,在计数到N-1时,输出时钟变为1,回到计数0时,又变为0;在时钟为1期间,只要保持计数值N-1为半个时钟周期,即实现了N-0.5的分频。图2将N-0.5分频时钟再二分频,异或,可使得触发时钟每经过N-0.5分频时钟周期就会产生一次时钟翻转。这样即可实现N-0.5倍的分频。

图1 传统半整数分频器的实现

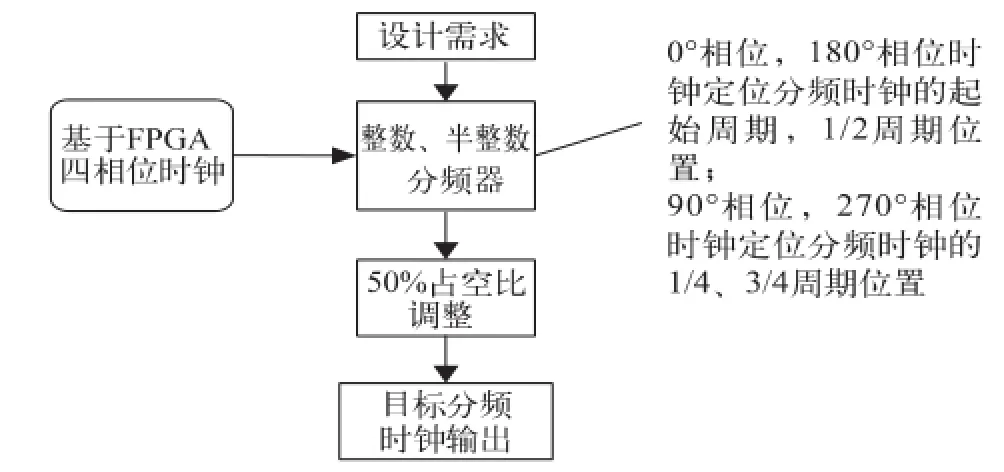

图2 整数半整数分频电路设计流程图

图2所示为整数半整数分频电路设计流程图,整数半整数50%占空比时钟分频的实现分为4个阶段。第一阶段提出设计所需要的目标分频系数,并确定n× 2分频系数;然后进入第二阶段,围绕第一阶段的两种分频系数,对分频器电路进行配置,依据FPGA内四项位时钟产生目标分频时钟,随后进入占空比调整阶段。在完成占空50%调整之后进入最后一个阶段输出目标分频时钟。

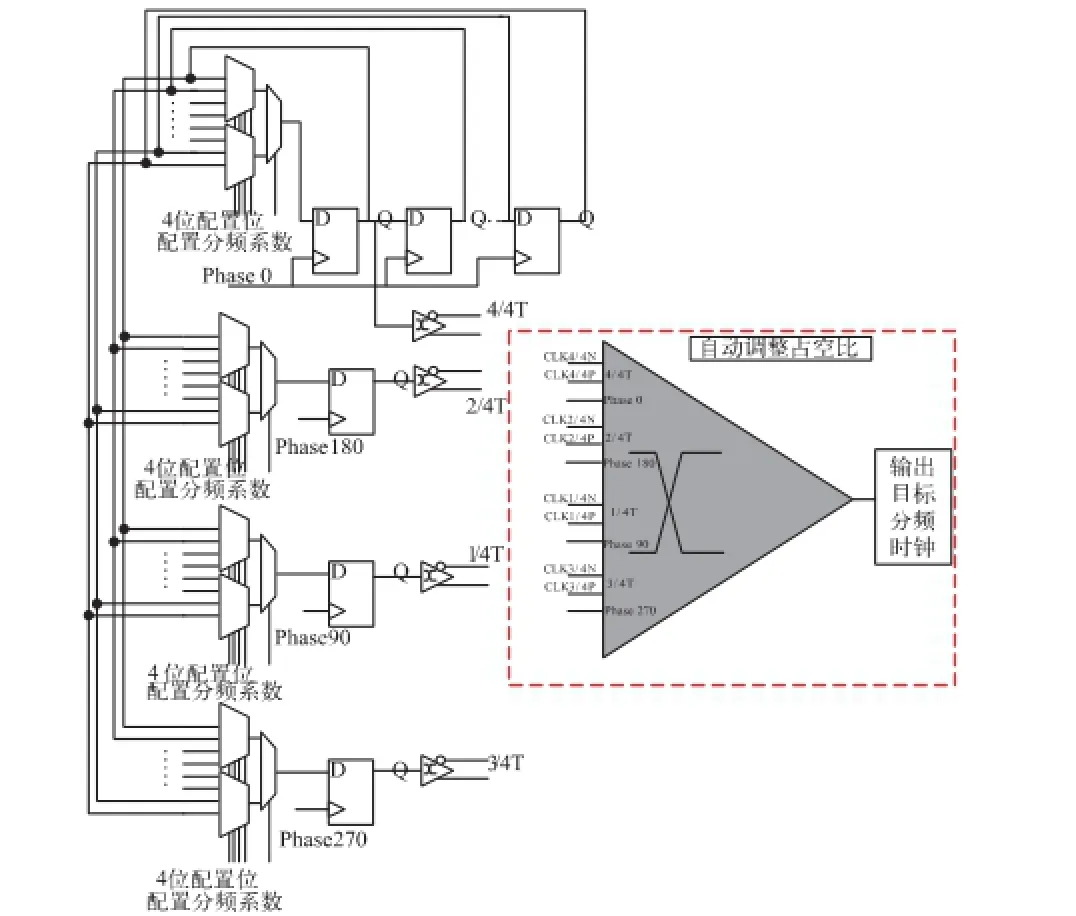

图3所示为整数半整数分频器电路设计,其工作原理如下所述:首先通过配置,选择对应n×2分频系数(n为目标分频系数)的MUX,完成分频后,FPGA内部的四项位时钟负责采集n分频时钟的关键周期点。从图3可以看出,分别采用4路单输入差分结构来合成分频时钟,最后如图2所示在占空比调整阶段,围绕之前输入的4路时钟,采用多输入差分电路,合成n分频时钟,并完成占空比50%的调整后输出。本设计在功能上可以配置任意整数半整数分频系数[3],并对目标分频时钟完成自动调整占空比功能;在设计结构上采用对称重复的设计单元,分频过程中不存在计数器计数所浪费的时间和所需要的设计空间,能够快速定位到半整数分频的周期和占空比50%的时钟位置。

图3 整数半整数分频器设计图

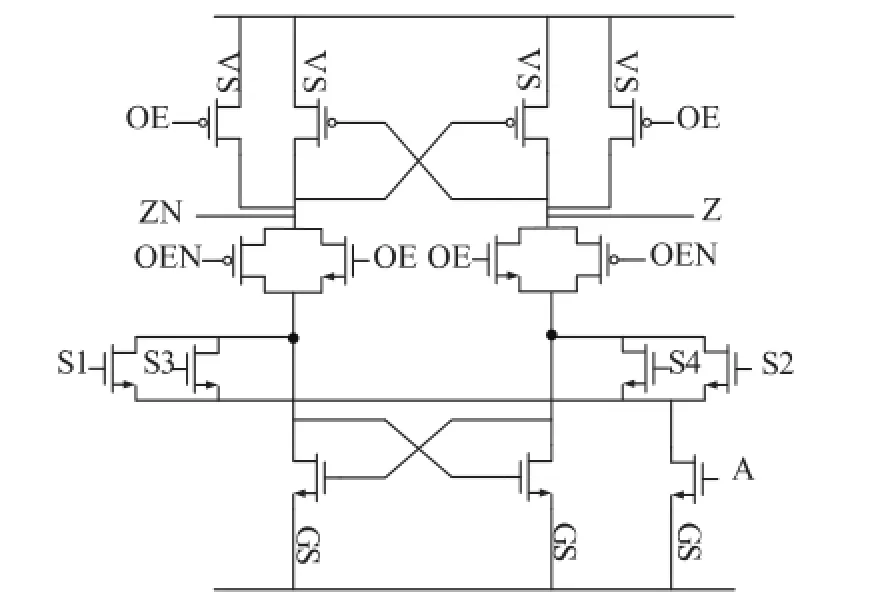

如图4所示,提供了图3小数分频时钟(目标分频时钟)调整占空比差分结构,其中A置为高电平,OE、OEN互补,在分频前OE置为“1”;当分频开始时,OE置为“0”,同时S1接N×2分频的起始周期时序,S2接N×2分频的半周期时序,S3接N×2分频的四分之一周期时序,S4接N×2分频的四分之三周期时序。

图4 输出分频时钟差分结构

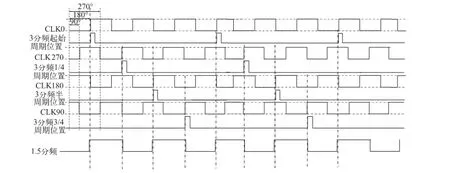

如图5所示设计提供了具体的1.5分频实现过程。首先在完成3分频时,需要源时钟采用触发器输出并反馈的方法,经过3个触发器,与PHASE0时钟通过差分使之定位到3分频的周期位置,另外需要源时钟过1个触发器,与PHASE180时钟通过差分定位到3分频半周期位置。同理,将得到四分之一、四分之三周期位置,设计将 PHASE0与 PHASE180、PHASE90与PHASE270组成两组互补时钟,由于两组时钟相位相差180°,那么一定存在超前和滞后半个周期,所以在后半段完成定位分频时钟的关键周期点时起到了重要作用,并且两组时钟之间又有着90°相位差,所以在定位四分之一、四分之三周期的关键周期点上提供了保障。此外在设计中采用完全相同的结构进行设计,从而降低了设计复杂度[4]。

图5 1.5分频的实现

3 仿真验证

整个设计基于SMIC工艺,建立整个仿真验证环境,利用Cadence公司仿真工具spctre进行设计仿真验证。

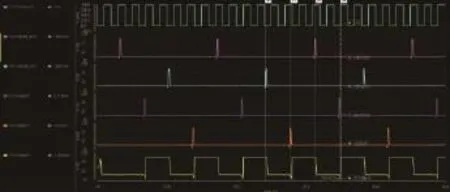

图6 3.5分频的仿真实现

图6举例说明分频时钟的实现,从仿真结果可以看出实现的是3.5分频时钟。其中在完成目标分频时钟的几个关键周期点时采用窄脉冲做标记,随后需要采用调整占空电路的方法来完成时钟的翻转。从仿真波形上看,本设计最重要的是分频器的设计和分频时钟关键点的定位,控制好窄脉冲的脉宽对后续的占空比调整至关重要,过窄达不到时钟的翻转上升或下降沿时间,造成差分来不及响应,过宽则超过了分频时钟的占空时间。

4 结论

本文提出了一种基于FPGA可配置任意整数半整数50%占空比分频的实现方法,介绍了现有分频方法的局限性,提出了一种新的设计原理以及实现框图,最后进行了仿真验证。本设计应用于可配置任意分频时钟的设计领域,设计一方面突破计数器计数的方法带来的冗余设计问题,更简单地通过配置可实现任意整数半整数分频;另一方面巧妙采用了差分结构实现分频时钟50%占空比的设计要求,使其更高效地完成时钟占空比的调整。

[1]徐志军,徐光辉.CPLD/FPGA的开发与应用[M].北京:电子工业出版社,2002.

[2]高博,龚敏.基于FPGA的可控分频器研究与设计[J].电子工程师,2003,29(6):44-46.

[3]刘亚海,林争辉.基于FPGA的小数分频器的实现[J].现代电子技术,2005,28(3):113-114.

[4](美)拉贝艾(Rabaey JM)等著,周润德等译.数字集成电路——电路、系统与设计(第二版)[M].北京:电子工业出版社,2004:319-357.

Design of FPGA-Based Frequency Dividing Circuit Capable of 50%Duty-Cycle Configuration for Integers/Half-Integers

WANG Xinghong1,TU Bo1,YAN Hua2,ZHANG Yanfei1(1.China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China;2.East Technologies,inc.Wuxi 214072,China)

In the paper,an FPGA-based frequency dividing circuit is designed.In the design,the FPGA phase-shift clock and flip-flop circuit are used to adjust the duty cycle of clock according to phase relation among phase-shiftclocks.The design usesmulti-inputdifferentialclock latch to achieve the integer/half-integer clock division.And the results are verified by simulations.

FPGA;duty-cycle;integer or half-integer frequency division;differential circuit

TN402

A

1681-1070(2017)01-0032-03

王兴宏(1989—),男,甘肃庆阳人,本科,工程师,研究方向为千万门级FPGA设计与验证。

2016-6-3