基于Virtex 4 FPGA的全覆盖二倍线内建自测试*

2017-02-09董宜平谢文虎

董宜平,谢文虎,李 光

(中国电子科技集团公司第58研究所,江苏无锡214035)

基于Virtex 4 FPGA的全覆盖二倍线内建自测试*

董宜平,谢文虎,李 光

(中国电子科技集团公司第58研究所,江苏无锡214035)

随着集成电路技术的发展,高集成度和高复杂度的器件不断出现,大规模集成电路的测试技术成为重要的研究方向。自建内测试方法是一种有效的系统级大规模集成电路FPGA测试方法。提出了一种基于Xilinx公司Virtex-4(V4)系列芯片全覆盖的FPGA二倍线内建自测试方法,该方法采用脚本生成Xilinx设计语言(XDL),对V4芯片二倍线进行全局布线,然后进行FPGA配置,施加测试向量,从而对固定故障或者桥接故障进行测试。同时给出了基于XC4VLX100芯片的实际测试结果,验证了该测试方法的正确性。

XDL;内建自测试;测试向量;全局布线;二倍线

1 引言

可编程逻辑器件FPGA,具有开发周期短、成本低、风险小、集成度高、灵活性强且便于电子系统维护和升级的特点,因此成为了数字芯片的主流,被广泛应用在通信、控制、视频、信息处理、消费电子、互联网、汽车以及航空航天等诸多领域。在FPGA被使用之前需要进行充分的测试,以保证FPGA器件的可靠性。

对FPGA进行功能测试可分为3个主要步骤:首先,给FPGA配置内建测试向量;其次,在配置完成后需要根据内建测试向量在相应的引脚加外部测试向量集;最后,通过观察输出引脚的现象来分析判断芯片的好环。

本文介绍一种基于XDL(Xilinx Design Language)语言的FPGA内建测试向量的编写方法。第一部分概述了本文研究的内容及意义。第二部分描述Xilinx FPGA XC4VLX100的结构。第三部分介绍了布线资源测试的主要故障类型。第四部分介绍了XDL(Xilinx design language)语言及如何利用XDL进行二倍线自建内测试等。第五部分给出了使用XDL生成的布线,施加测试向量的具体测试方法。第六部分为全文总结及研究展望。

2 Virtex 4 FPGA的结构

图1所示为Xilinx公司基于Virtex系统架构的xc4vlx100的FPGA,包括IOB (Input/output Block)、CLB(configurable Logic Block)、CLB的互联开关盒(Swith Box,SB)等。基于以上架构的FPGA,IOB的物理位置位于左侧和右侧。

图1 Xilinx xc4vlx100架构

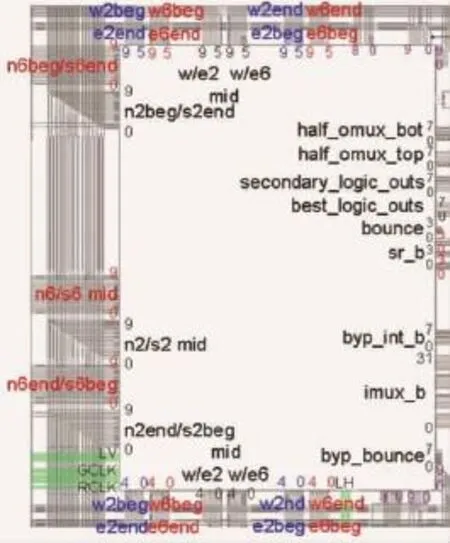

图2所示为FPGA内部SB的内部接线盒架构,包括二倍线起始(E2Begin,W2Begin,N2Begin,S2Begin),二倍线终止(E2End,W2End,N2End,S2End),六倍线起始(E6Begin,W6Begin,N6Begin,S6Begin),六倍线终止(E6End,W6End,N6End,S6End)。

图2 FPGA xc4vlx100内部Swith Box的接线

3 FPGA布线资源典型故障和测试方法

在FPGA芯片中,布线资源占据FPGA芯片面积的大部分(50%~90%),是FPGA资源中发生故障概率最高的部分,所以布线资源的测试非常重要。布线资源的故障一般有:(1)线段的固定型(stuck at)故障;(2)线段的开路(stuckopen)故障;(3)线段间的桥接故障。

FPGA器件的测试,简单来说就是把FPGA器件配置成相应的测试电路,用多次配置来覆盖所有的资源,然后对每项配置施加特定的测试向量。好的布线资源的测试方法是在尽可能高的故障覆盖率下,通过最少的编程次数和测试向量对布线资源进行测试。

本文提供的测试方法针对二倍线布线资源故障,依据XDL规范自主布线,把一个方向(南北或者东西)的所有二倍线串联起来,从而通过一次配置,就能够判断那根二倍线是否有故障。通过多次配置进行二分法排除,可以确定哪一行或者哪一列的二倍线出现故障。

4 XDL语言规则

4.1 XDL基本格式

XDL语言是xilinx公司开发的一种全功能物理层设计语言。由4个声明构成了对整个文件和电路的描述,这4个声明分别是design声明、module声明、Instance声明和net声明。

Design声明在XDL必须存在,并且只能存在一次。该声明包括一个全局的设计名称以及目标FPGA的部分名称。Design的格式如下:

design"V4test"xc4vlx100ff1148-10 v3.2;

Module声明是一系列instance和net的结合,通常在硬宏(hard macros)里使用。本文不涉及。

Instance声明以关键词’inst’开头,元件类型主要有CLB、IOB、TBUF等几种类型,放置元件关键词placed,所在的tile,即所在的分区。对XC4VLX100 CLB_x1y0的Instance进行配置的实例格式如下:

inst"INST_X0Y0""SLICEM",placed CLBX1Y0 SLICE_X0Y0,

cfg " BXINV::#OFF BYINV::#OFF BYINVOUTUSED::#OFF BYOUTUSED::#OFF CEINV::#OFF

CLKINV::#OFF COUTUSED::#OFF CY0F:: #OFF CY0G::#OFF CYINIT::#OFF DIF_MUX::#OFF

DIGUSED::#OFF DIG_MUX::#OFF DXMUX: :#OFF DYMUX::#OFF F:LUT4_inst[8449]:#LUT:D= (A4)

F5USED::#OFF FFX::#OFF FFX_INIT_ATTR: :#OFF FFX_SR_ATTR::#OFF FFY::#OFF

FFY_INIT_ATTR::#OFF FFY_SR_ATTR:: #OFF FXMUX::#OFF FXUSED::#OFF F_ATTR::#OFF

G:LUT4_inst[8450]:#LUT:D=(A4)GYMUX:: #OFF G_ATTR::#OFF REVUSED::#OFF

SHIFTOUTUSED::#OFF SLICEWE0USED:: #OFF SLICEWE1USED::#OFF SRFFMUX::#OFF

SRINV::#OFF SYNC_ATTR::#OFF WF1USED::#OFF WF2USED::#OFF WF3USED::#OFF

WF4USED::#OFF WG1USED::#OFF WG2USED::#OFF WG3USED::#OFF WG4USED:: #OFF

XBMUX::#OFF XBUSED::#OFF XMUXUSED::#OFF XUSED::0 YBMUX::#OFF YBUSED::#OFFYMUXUSED::#OFF YUSED::0";

Net声明由net、输入 (inpin)、输出(outpin)、PIP (Programmable Interconnect Point)共4部分组成。一个从IOB引入一根输入线到CLB_X1y0的F1的Net声明如下:

net"IOB0inLine0",

outpin"IOB0in"I,

inpin"INST_X1Y1"F1,;

4.2 使用XDL生成二倍线测试布线

使用XDL生成二倍线的测试布线分成4个步骤,步骤一将IO的输入接入到二倍线的输入,或者将前一行或者前一列的二倍线输出接入到二倍线的输入。步骤二利用每行或者每列中的某个CLB进行中继,将IO的输入经过Slice引入到二倍线中,同时将同行或者同列不同方向的二倍线首尾相接。步骤三将同方向的二倍线按照行或者列进行首尾相接。步骤四所示是将二倍线的输出连接到下一行或者下一列的输入,将相邻行或者相邻列的二倍线进行首尾相接,或者将二倍线的输出连接到IOB的输出上。

图3 FPGA二倍线测试步骤

下面以0号二倍线(E2begin0和W2begin0)为例,如图3所示,每个步骤对应的XDL net如下:

步骤一将IOB连接到二倍线的一个slice输入F1,其中INST_IOB0in为XC4VLX100的IOB AM25, INST_X1Y1为slice X1Y1:

net"IOB0inLine0",

outpin"IOB0in"I,

inpin"INST_X1Y1"F1,;

步骤二、三实现的 XDL net如下,其中INST_X0Y0为Slice x0y0,INST_X1Y1为Slice x1y1:

net"netrow0WELine0",

outpin"INST_X1Y1"X,

inpin"INST_X0Y0"G4,

pip CLB_X1Y0 X_PINWIRE3 ->BEST_LOGIC_OUTS3_INT,

pipINT_X1Y0BEST_LOGIC_OUTS3->E2BEG0,

pip INT_X0Y0 E2END0->E2BEG0,

pip INT_X2Y0 E2END0->E2BEG0,

……

pip INT_X70Y0 E2END0->E2BEG0,

pip INT_X72Y0 E2END0->E2BEG0,

pip INT_X3Y0 W2END0->W2BEG0,

pip INT_X5Y0 W2END0->W2BEG0,

……

pip INT_X69Y0 W2END0->W2BEG0,

pip INT_X71Y0 W2END0->W2BEG0,

pip INT_X0Y0 W2END0->W2BEG0,

pip INT_X1Y0 E2END0->IMUX_B0,

pip CLB_X1Y0 IMUX_B0_INT->G4_PINWIRE0,

pip CLB_BUFFER_X36Y0 CLB_BUFFER_ IE2MID0->CLB_BUFFER_E2MID0,

pip CLB_BUFFER_X36Y0 CLB_BUFFER_ W2END0->CLB_BUFFER_IW2END0,

pip L_TERM_INT_X0Y0 L_TERM_INT_ W2BEG0->L_TERM_INT_E2MID0,

pip R_TERM_INT_X72Y0 R_TERM_INT_ E2MID0->R_TERM_INT_W2END0,

;

net"netrow0EWLine0",

outpin"INST_X0Y0"Y,

inpin"INST_X0Y0"F4,

pip CLB_X1Y0 Y_PINWIRE0->BEST_LOGIC_ OUTS4_INT,

pipINT_X1Y0BEST_LOGIC_OUTS4->W2BEG0,

pip INT_X0Y0 E2END0->E2BEG0,

pip INT_X2Y0 W2END0->W2BEG0,

……

pip INT_X70Y0 W2END0->W2BEG0,

pip INT_X72Y0 W2END0->W2BEG0,

pip INT_X3Y0 E2END0->E2BEG0,

pip INT_X5Y0 E2END0->E2BEG0,

……

pip INT_X69Y0 E2END0->E2BEG0,

pip INT_X71Y0 E2END0->E2BEG0,

pip INT_X1Y0 W2END0->IMUX_B8,

pip CLB_X1Y0 IMUX_B8_INT->F4_PINWIRE0,

pip CLB_BUFFER_X36Y0 CLB_BUFFER_ IE2BEG0->CLB_BUFFER_E2BEG0,

pip CLB_BUFFER_X36Y0 CLB_BUFFER_ W2MID0->CLB_BUFFER_IW2MID0,

pip L_TERM_INT_X0Y0 L_TERM_INT_ W2MID0->L_TERM_INT_E2END0,

pip R_TERM_INT_X72Y0 R_TERM_INT_ E2BEG0->R_TERM_INT_W2MID0,

;

这里面有 4个转角,其中 pip L_TERM_ INT_X0Y0L_TERM_INT_W2BEG0->L_TERM_ INT_E2MID0为最左侧西向向东向的转角,pip R_TERM_INT_X72Y0 R_TERM_INT_E2MID0 ->R_TERM_INT_W2END0为最右侧东向向西向的转角,pip L_TERM_INT_X0Y0 L_TERM_INT_W2MID0 ->L_TERM_INT_E2END0为最左侧西向东转角,pip R_TERM_INT_X72Y0 R_TERM_INT_E2BEG0 ->R_TERM_INT_W2MID0为最右侧东向西转角。

步骤四的实现为将本行首尾相接的二倍线输出连接到下一行的输入,其中INST_X1Y3为下一行的slice X1Y3:

net"netrow0line0Out",

outpin"INST_X0Y0"X,

inpin"INST_X1Y3"F1,;

依此方法,逐步生成整个FPGA的二倍线南北方向或者东西方向的布线。

4.3 根据测试布线生成rbt文件

通过脚本或者C语言写程序,生成整个FPGA的二倍线南北或者东西方向的布线XDL后,调用XDL命令XDL-xdl2ncd生成NCD文件,然后用FPGA Editor打开,调用auto route功能,把所有的二倍线首尾连接好。然后再调用bitgen生成rbt文件。

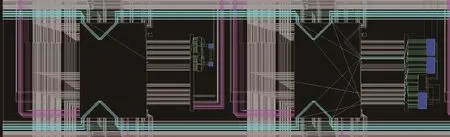

完整的XC4VLX100的FPGA东西向的二倍线NCD部分图如图4所示,包括全部的E2begin0~E2begin9,W2begin0~W2begin9。

5 使用测试向量对XC4VLX100进行测试

生成RBT文件后,对FPGA XC4VLX100进行配置,然后对输入侧对应E2Begin0~E2Begin9的IOB施加测试向量。如果对0号线(E2begin0)进行测试,则施加(1,0,0,0,0,0,0,0,0,0)的测试向量,然后在对应输出端的 IOB观察输出结果。如果输出为(1,0,0,0,0,0,0,0,0,0),则0号线无故障,如果输出不为(1,0,0,0,0,0,0,0,0,0),则0号线有故障,记录输出结果。然后对0号线再施加(0,1,1,1,1,1,1,1,1)的测试向量,如果输出为(0,1,1,1,1,1,1,1,1),则0号线无故障,如果输出不为(0,1,1,1,1,1,1,1,1),则0号线有故障,记录输出结果。

综合输出结果,故障类型初步判断为:

(1)输出结果始终为(0,0,0,0,0,0,0,0,0,0),0号线固定0故障或断路故障;

图4 完整的东西向二倍线布线部分图

(2)输出结果始终为(1,0,0,0,0,0,0,0,0,0),0号线固定1故障或断路故障;

(3)0号线位置为0,其他位置出现了1,或者0号线位置为1,其他位置出现了0,则为桥接故障。

判断出二倍线故障后,通过二分法将IOB输入端、IOB输出位置进行变化,则可以定位哪一行或者哪一列出现了故障。

6 结论

通过直接写XDL,进行二倍线东西方向或者南北方向直接布线的方式,通过一次配置就能判断出二倍线东西方向或者南北方向是否有故障,而且故障覆盖率为100%。这种方法同样可以扩展到能够首尾相接的六倍线。

[1]Christian Beckhoff,Dirk Koch,Jim Torresen.The Xilinx Design Language(XDL):Tutorial andUse Cases[J].

[2]M Renovell,Y Zorian.Different Experiments in Test Generation for XILINX FPGAs[J].ITC INTERNATIONAL TEST CONFERENCE,2000,32(2):854-862.

[3]Mehdi Baradaran Tahoori,Subhasish Mitra.Fault Grading FPGA Interconnect Test Configurations[J].ITC INTERNATIONAL TEST CONFERENCE,2002,22(2):608-617.

[4]Soft Test Inc.The Fundamentals of Digital Semiconductor Testing[P].Version 2.03,1999.

[5]OReilly.Learning Perl 5th Edition[P].2008,7.

[6]http://china.xilinx.com[EB/OL].

[7]成飞.基于ATE的FPGA测试 [D].上海:复旦大学,2011,4.

[8]王世颖.基于ATE的百万门级FPGA测试方法的研究[D].成都:电子科技大学,2012,2.

[9]张秀均,陈诚,孟祥媛.一种用perl编写Xilinx的FPGA内建测试向量的方法[J].电子与封装,2014,14(3):18-20.

A Full-Coverage Double-line BIST Method for Vertex 4 FPGA

DONG Yiping,XIE Wenhu,LI Guang

(China Electronic Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

The rapid development of Integrated circuit has been increasingly bring about highly integrated and complicated device.The test technology is becoming more and more important.Built in selfttest(BIST)is an effective system-level test method for FPGA.A BIST method based on Vertex 4 for full coverage of FPGA double lines is presented in this paper.At first,XDL language written in script is used for global routing of V4 double lines.Then FPGA for test is configured,and test vector is added.The stuck and bridge fault then can be diagnosed according to the output.Then at the end the test result of XC4VLX100 is given.

XDL;BIST;test vector;global routing;double lines

TN407

A

1681-1070(2017)01-0019-05

董宜平(1983—),男,2006年东南大学电子工程学院学士毕业,2011年日本早稻田大学理工学院系统大规模集成电路专业工学博士,研究方向为基于FPGA的高性能片上网络NoC,2012年4月至2014年7月任职于日本日立制作所研究开发中心,2014年8月起任职于中国电子科技集团公司第58研究所,从事自主高性能大规模FPGA芯片的研发工作。

2016-7-26

江苏省自然基金青年基金(BK20160202)