DRM/DAB/AM/FM频率综合器中吞吐脉冲分频器的设计

2014-06-06雷雪梅王志功沈连丰王科平

雷雪梅,王志功,沈连丰,王科平

(1.东南大学信息科学与工程学院,210096 南京;2.内蒙古大学电子信息工程学院,010010 呼和浩特;3.华盛顿大学电子电气工程学院,98195 西雅图)

DRM/DAB/AM/FM频率综合器中吞吐脉冲分频器的设计

雷雪梅1,2,王志功1,沈连丰1,王科平3

(1.东南大学信息科学与工程学院,210096 南京;2.内蒙古大学电子信息工程学院,010010 呼和浩特;3.华盛顿大学电子电气工程学院,98195 西雅图)

为使DRM/DAB/AM/FM频率综合器具有良好性能,本文设计了一种高速大分频比低功耗吞吐脉冲分频器.此吞吐脉冲分频器由32/33双模预分频器(dual-modulus prescaler,DMP)、5位吞吐计数器和11位可编程分频器及时序控制电路构成.此吞吐脉冲分频器内部的不同模块分别采用SCL、TSPC、CMOS静态触发器及可置位的CMOS静态触发器等多种触发器结构优化,使此吞吐脉冲分频器具有高速、大分频比和低功耗的特点.此吞吐脉冲分频器应用中芯国际SMIC 0.18 μm RF CMOS工艺流片,芯片核心面积为270 μm×110 μm.测试结果显示,在1.8 V工作电压的条件下,此吞吐脉冲分频器的最高工作频率为3.4 GHz,工作频率范围为0.9~3.4 GHz.在输入信号频率为3.4 GHz,分频比为45 695时,功耗为3.2 mW.实验结果表明,此吞吐脉冲分频器完全满足DRM/DAB/AM/FM频率综合器的要求.

吞吐脉冲分频器;高速;大分频比;低功耗;DRM/DAB/AM/FM频率综合器

随着广播技术的发展,数字广播逐步取代模拟广播,并已成为广播技术发展的必然趋势.而在众多数字广播标准中,DRM(Digital Radio Mondiale)[1]和 DAB (Digital Audio Broadcasting)[2]由于其突出的优点[3]而被在全球推广应用.但目前基于DRM和DAB标准的高质量接收机体积较大且价格昂贵,而使其成为推广的一个瓶颈.因此,提高集成度、降低价格、减小体积成为数字广播接收机的研究热点.另一方面,为了兼顾技术发展和现有资源再利用,基于DRM和DAB标准的接收机应该兼容模拟广播AM和FM.兼容多个标准,接收机需覆盖的频段范围为148~1 500 000 kHz,使射频前端成为实现接收机的关键部分和设计难点.

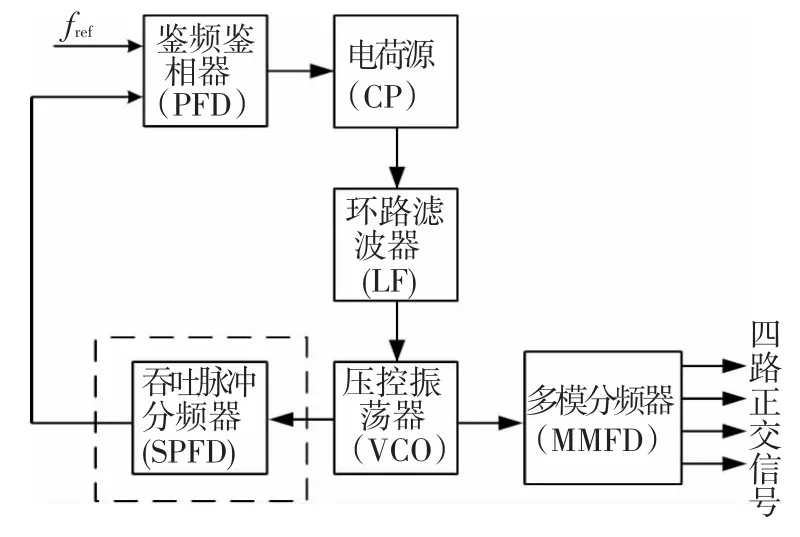

为了能同时满足DRM、DAB、AM和FM标准对接收机的要求,降低射频前端频率综合器的设计难度,射频前端采用二次变频的低中频结构,本振信号输出范围为 36.600 5 ~1 572.452 MHz[4].另外为了同时满足DRM、DAB、AM和 FM标准的信道带宽要求,频率综合器采用了带输出分频器的单环单压控振荡器结构[3],如图1所示.

为满足DRM、DAB、AM和 FM标准各个频段对频率间隔的要求,频率综合器环内分频比范围为3 272~37 162,吞吐脉冲分频器的输入信号频率范围为2 500~3 055 MHz,在此吞吐脉冲分频器必须具有高速、大分频比、可编程和低功耗等特性.本文的主要工作是设计满足以上要求的高速低功耗16位可编程吞吐脉冲分频器,并采用中芯国际SMIC 0.18-μm CMOS RF工艺实现.

图1DRM/DAB/AM/FM频率综合器的结构框图

1 吞吐脉冲分频器结构

根据DRM/DAB/AM/FM频率综合器对吞吐脉冲分频器的要求,对吞吐脉冲分频器的主要模块双模分频器(dual-modulus prescaler,DMP)、吞吐计数器和可编程分频器进行规划.

吞吐脉冲分频器工作原理如下:首先分别给可编程分频器和吞吐计数器置初值P和S(P>S),双模分频器的模式转换控制信号MC置为低电平,同时在输入时钟信号的控制下DMP进行(M+1)分频.吞吐计数器和可编程分频器把DMP的输出信号作为输入时钟信号开始计数.当吞吐计数器计数到0时,MC信号翻转为高电平,DMP开始M分频.当可编程分频器各个输出端皆为0时,可编程分频器、吞吐计数器和MC复位,重复上述过程.

根据以上描述可知,在时序控制电路的控制下,DMP对输入信号首先S次进行(M+1)分频,然后进行(P-S)次M分频,所以总的分频比N为

分析此吞吐脉冲分频器分频比要求,确定双模分频器、吞吐计数器和可编程分频器的位数.分频比要求:

1)最高分频比为37 162(1 001 000 100 101 010)2,吞吐脉冲分频器为16位分频器;

2)最低分频比3 272(110 011 001 000)2,即要求吞吐计数器和DMP触发器个数和小于11;

3)为了使分频比可连续变化,DMP和吞吐计数器为相同位数.

综合以上分析,最终确定此吞吐脉冲分频器包括一个32/33双模分频器DMP、5位的吞吐计数器、11位的可编程分频器以及对应的时序控制电路,其结构如图2所示.

图2 可编程吞吐脉冲分频器的结构框图

2 模块设计

此吞吐脉冲分频器的主要模块为32/33多模分频器、吞吐计数器和可编程分频器,其主体电路单元都是触发器,各个模块的设计主要集中在从输入信号频率范围、功耗及噪声等方面选择合适的触发器结构,并进行优化.

2.1 32/33双模分频器的设计

DMP的实现方式主要有三种:触发器和组合逻辑门[5]、相位开关技术[6]和注入锁定技术[7].其中相位开关技术的双模分频器需要解决信号畸变问题,实现复杂;注入锁定技术的双模分频器的带宽比较窄;触发器和组合逻辑门的双模分频器具有宽带特性而被广泛应用[8-13].

本设计为了可靠保证速度和工作带宽,32/33双模分频器采用触发器和组合逻辑门实现的双模分频器,包括同步4/5双模分频器和异步8分频器两个模块,其结构如图3所示.图中Vc信号为控制4/5双模分频器的分频模式,当Vc高电平为4分频,低电平为5分频时,Vc信号的电平转换由MC信号和异步8分频器的3个输出信号通过“或”运算来进行控制.

图3 32/33双模分频器的结构框图

由吞吐脉冲分频器的输入信号频率范围可知,同步4/5双模分频器输入信号频率在2.5~3.055 GHz范围内,所以4/5双模分频器的触发器选用广泛应用于高速宽带的源极耦合逻辑(source couple logic,SCL)[8-10]结构.对于这种结构的双模分频器,其最高工作频率fmax为

式中:tpdff为一级触发器的传输延迟;tpgate为分频器内部逻辑运算的逻辑门的传输延迟.根据式(2),减少传输延迟可提高工作速度,所以在SCL触发器里集成了“或”逻辑[14],使整个延时只为一级触发器的延时,极大的提高了工作速度.

异步分频器中的第一级2分频器的工作频率范围为500 MHz~1 GHz,其工作频率为中高,重点优化功耗和面积,所以第一级2分频器的触发器结构为真单相时钟(true-single-phase-clock,TSPC)[12],通过参数优化达到指标要求.

对于异步分频的最后两级,最高工作频率不超过500 MHz,选择具有相对较大的带宽、优良相位噪声性能及静态功耗为零的CMOS静态触发器,其电路结构如图4所示.

图4 CMOS静态触发器的电路原理

以上3种结构的触发器配合工作,使整个DMP具有高速、宽频带、低功耗和低相位噪声等性能.

2.2 吞吐计数器的设计

吞吐计数器的输入时钟信号为32/33双模分频器的输出信号,其频率范围为75~96 MHz,为了完成可编程计数,每一级分频器必须具有置位和使能端,所以其内部触发器单元基本结构选择为带置位使能端的CMOS静态DFF(在图4的电路上加上带置位和使能端).吞吐计数器同时为DMP提供MC信号.为了保证整个吞吐脉冲分频器的工作时序,产生的MC信号必须保持到置数生效之前,即置数完毕后才可翻转为低电平,并在SC计数到0时同步翻转为高电平.

因此,吞吐计数器包括两部分:5位的异步可置位计数器和MC信号产生电路,如图5所示.

图5 吞吐计数器的原理

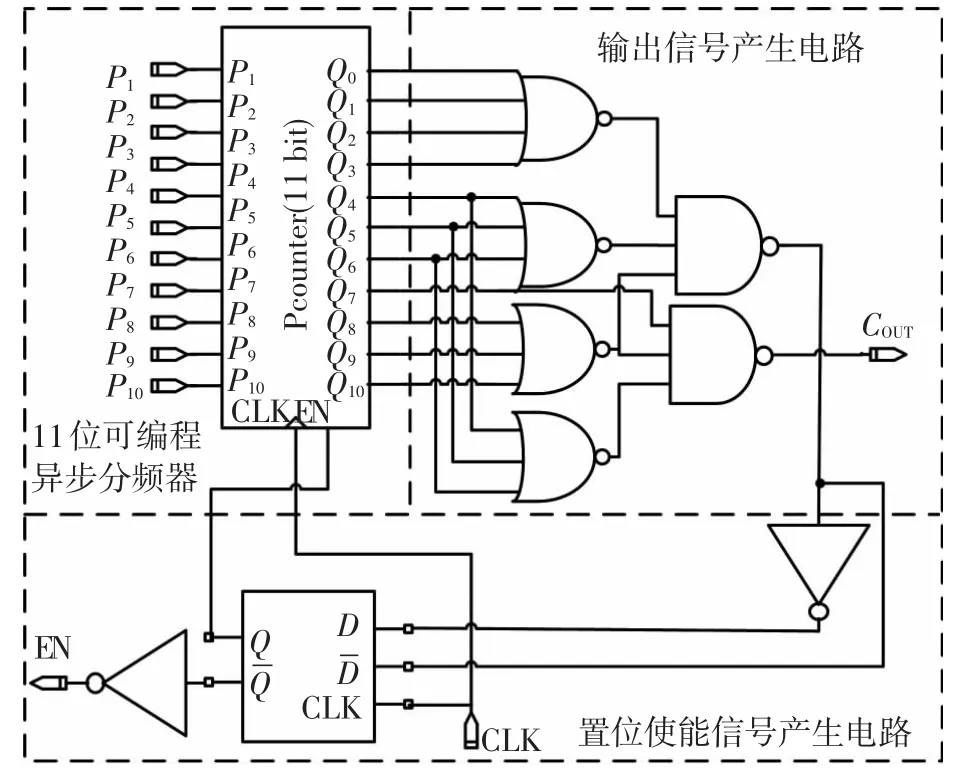

2.3 可编程分频器的设计

可编程分频器的输入时钟信号频率范围和吞吐计数器相同,也需具有可编程分频功能,所以其内部触发器单元结构与吞吐计数器相同.可编程分频器同时要为自身和吞吐计数器提供置数使能信号EN,为了保证可编程分频器和吞吐计数器有序工作,置位信号EN要求在1个时钟周期内完成并保持1个时钟周期.故可编程分频器包括三部分:11位异步可置位分频器、置位使能信号产生电路和输出信号产生电路,如图6所示.

图6 可编程分频器的原理

综上所述,32/33双模分频器、5位吞吐计数器和11位可编程分频器在时序上配合工作,在电路上无缝衔接,保证了吞吐脉冲分频器良好性能.

3 测试结果

设计的可编程吞吐脉冲分频器采用中芯国际SMIC 0.18 μm RF CMOS 工艺实现的,其芯片照片如图7所示.包括焊盘和驱动电路,芯片面积为625 μm×575 μm,其中核心部分的面积为270 μm×110 μm.

图7 吞吐脉冲分频器的芯片照片

在流片过程中,为了节省芯片面积,一些可编程控制引脚预先在芯片内部就接到了VDD或GND引脚上.例如,图6中的P0和P1接到VDD,P2、P3、P5、P6和P9接到 GND;图5 中的 S4接到图5 中的P10,S3接到P8,S2接到P7,S1和S0接到P4.所以在测试过程中,分频比的改变是通过改变接入到P10、P8、P7和P4的高低电平来改变的.由于篇幅原因,只给出典型的两种控制字,三种测试结果,控制字的设置如表1所示.

表1 测试时的两种控制字的设置

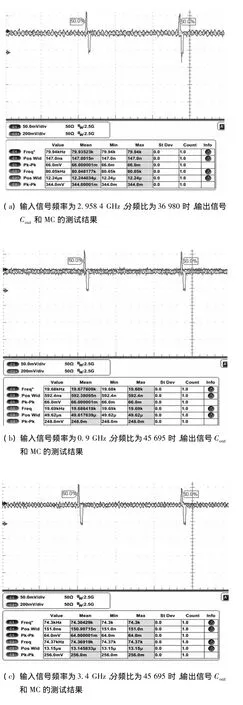

芯片的测试在东南大学射频与光电集成电路研究所完成,测试中使用的仪器有:微波与高速芯片探针台(Cascade Summiti 1000)、脉冲码形发生器(Advantestd 3186)、示波器(Tektronix DPO 7354)以及电源 (Kikusui PMR18-1.3TR 和Agilent 66309D,测试结果如图8所示.图8中上面的信号为可编程分频器的输出信号Cout,下面为MC信号.

对应于此吞吐脉冲分频器灵敏度测试结果如图9所示.由图9可知,在输入信号峰峰值电压为小于1 V的情况下,此吞吐脉冲分频器可靠的工作频率范围为 0.9 ~3.4 GHz.

图8 可编程分频器的测试结果

图9 可编程吞吐脉冲分频器灵敏度测试结果

此16位可编程吞吐脉冲分频器与最近其他公开发表可编程整数分频器的研究测试结果比较如表2所示.为了对各个可编程分频器的总体性能比较,特定义优值FOM(figure of merit),根据文献[15]的研究成果可知,功耗与输入频率和分频比近似成正比关系,定义FOM为

式中:fmax为最高输入频率,(Mdivisionratio)max为所能达到的最大分频比,P为所消耗的功率.

表2 与其他最近的研究成果比较

4 结论

本文设计了应用于DRM/DAB/AM/FM频率综合器的高速低功耗16位可编程吞吐脉冲分频器,采用中芯国际 SMIC 0.18 μm CMOS 工艺实现.测试结果表明,此吞吐脉冲分频器工作频率范围 为 0.9 ~ 3.4 GHz,在 1.8 V 的 工 作 电压,3.4 GHz的工作频率下,其功耗为7.2 mW(包括测试驱动电路的功耗).根据仿真,可以估算出各个部分的功耗,其中32/33双模分频器、5位吞吐计数器和11位可编程分频器的平均功耗分别为 2.61 mW、0.35 mW 和 0.09 mW,所以芯片核心部分的功耗为3.2 mW.由表2中本文设计实现的吞吐脉冲分频器与最近的研究结果比较可知,其所能达到的分频比最大,工作频率范围和功耗适中,并达到了最高的优值FOM.故此可编程分频器不仅完全满足 DRM/DAB频率综合器的要求,而且也适用于其他多标准、超宽带、低功耗的频率综合器.

[1]ETSI.ETSI ES 201 980.Digital Radio Mondiale(DRM);System Specnification [S]. Nice: European Telecommunications Standards Institute,European Broadcasting Union,2005.

[2]ETSI.ETSI EN 300 401.Digital Audio Broadcasting(DAB)to Mobile,Portable and Fixed Receivers[S].Nice:European Telecommunications Standards Institute,European Broadcasting Union,2006.

[3]周建政.DRM/DAB/AM/FM接收机射频前端芯片设计中的关键技术研究[D].南京:东南大学,2009.

[4]周建政,王志功,李莉,等.DRM接收机射频前端芯片的频率规划设计[J].高技术通讯,2008,18(5):480-486.

[5]LIN C S,CHIEN T H,WEY C L.A 5.5-GHz 1-mW full-Modulus-range programmable frequency divider in 90-nm CMOS process[J].IEEE Transactions on Circuits and Systems-II:Express Briefs,2011,58(9):550-554.

[6]CRANINCKX J,STEYAERT M.A 1.75 GHz 3 V dual modulus divider by 128/129 prescaler in 0.7 μm CMOS[J].IEEE Journal of Solid-State Circuits,1996,31(7):890-897.

[7]YIU Xiaopeng,ZHOU Jianjun,YAN Xiaolang,et al.Sub-mW multi-GHzCMOSdual-modulusprescalers based on programmable injection-locked frequency dividers[C]//IEEE Radio Frequency Integrated Circuits Symposium,2008.Atlanta,GA,2008:431-434.

[8]XU Yong,WANG Zhigong,LI Zhiqun,et al.A novel high-speed lower-jitterlower-powerdissipation dualmodulus prescaler and applications in PLL frequency synthesizer[J].Chinese Journal of Semiconductors,2005,26(1):176-179.

[9]LI Zhiqiang,CHEN Liqiang,ZHANG Jian,et al.A programmable 2.4 GHz CMOS multi-modulus frequency divider[J].Chinese Journal of Semiconductors,2008,29(2):521-526.

[11]CHI Baoyong,SHI Bingxue.A novel CMOS dualmodulus prescaler based on new optimized structure and synamic circuit technique[J].Chinese Journal of Semiconductors,2002,23(4):357-361.

[12]HUANG Qiuting,ROGENMOSER R.Speed optimization of edge-triggered CMOS circuits for gigahertz singlephase clocks[J].IEEE Journal of Solid-State Circuits,1996,31(3):456-465.

[13]de MIRANDA F P H,Jr Navarro S J,Van NOIJE W A M.A 4 GHz dual modulus divider-by 32/33 prescaler in 0.35 pm CMOS technology [C]//17th Symposium on Integrated Circuits and Systems Design, 2004.Pemanbuca,Brazil:[s.n.],94-99.

[14]XU Yong,WANG Zhigong,LI Zhiqun,et al.A novel high-speed lower-jitterlower-powerdissipation dualmodulus prescaler and applications in PLL frequency synthesizer[J].Chinese Journal of Semiconductors,2005,26(1):176-179.

[15]GAO Haijun,SUN Lingling,LIU Jun.Pulse swallow frequency divider with idle DFFs automatically powered off[J].Electronics Letters,2012,48(11):636-638.

[16]YU Lu,FAN Xiangning,LI Bin.A 4-6 GHz low-voltage CMOS integer-M frequency divider applied in wireless sensor networks[C]//IEEE 11th International Conference on Solid-State and Integrated Circuit Technology.Xi'an:[s.n.],2012:1-3.

[17]PAN Jie,YANG Haigang,YANG Liwu.A high-speed low-power pulse-swallow divider with robustness consideration[C]//9th InternationalConference on Solid-State and Integrated-Circuit Technology.Beijing:[s.n.],2008:2168-2171.

A design of pulse swallow frequency divider for DRM/DAB/AM/FM frequency synthesizer

LEI Xuemei1,2,WANG Zhigong1,SHEN Lianfeng1,WANG Keping3

(1.School of Information Science and Engineer,Southeast University,210096 Nanjing,China;2.College of Electronic Information Engineering,Inner Mongolia University,010010 Hohhot,China;3.Dept.of Electrical Engineering,University of Washington,98195 Seattle,USA)

For the good performance of DRM/DAB/AM/FM frequency synthesizer,the implementation of a high-speed large division ratio low-power pulse swallow frequency divider is described,which consists of a divided-by-32/33 dual-modulus prescaler(DMP),a 5 bits swallow counter,an 11-bits programmable divider,and a time sequence control circuit.The different modules of pulse swallow frequency divider apply SCL,TSPC,CMOS static flip-flop DFF,and CMOS static flip-flop DFF with preset to realize the low power,large division ratio,and high speed performances.The chip has been fabricated in a 0.18 μm CMOS process of SMIC and the core area is 270 μm×110 μm.Measured results show that its most high operation frequency is 3.4 GHz and the rang of operation frequency is from 0.9 GHz to 3.4 GHz.And when the operating frequency is 3.4 GHz and division ratio is 45 695,the maximum core power consumption is 3.2 mW under 1.8 V power supply.Its performance satisfies the requirement of DRM/DAB/AM/FM frequency synthesizer.

pulse swallow frequency divider;high speed;large division ratio;low power consumption;DRM/DAB/AM/FM frequency synthesizer

TN792;TN795

A

0367-6234(2014)03-0074-06

2012-12-17.

科技部中小企业创新基金资助项目(11c26213211234);内蒙古自治区高等学校科学技术研究资助项目(NJZY11016).

雷雪梅 (1972—)女,博士后,副教授;

王志功 (1954—)男,教授,博士生导师;

沈连丰 (1952—)男,教授,博士生导师.

王志功,zgwang@seu.edu.cn.

(编辑 张 宏)