基于信号/电源完整性的3D-SiP陶瓷封装设计

2017-02-09张荣臻高娜燕丁荣峥

张荣臻,高娜燕,朱 媛,丁荣峥

(中国电子科技集团公司第58研究所,江苏无锡 214035)

基于信号/电源完整性的3D-SiP陶瓷封装设计

张荣臻,高娜燕,朱 媛,丁荣峥

(中国电子科技集团公司第58研究所,江苏无锡 214035)

通过3D集成技术实现电子产品的小型化、高密度、高性能,已成为一条重要的技术途径。为了实现某型号数字信号处理系统的小型化,采用上下腔、3D叠层的气密性陶瓷封装结构,基于产品的信号/电源完整性对陶瓷封装进行了设计。运用Cadence Release16.3及SIwave5软件对其电性能进行了仿真分析,并根据仿真结果对封装设计进行优化,使封装的信号/电源完整性符合产品设计要求。最终研制生产的产品测试结果与仿真结果吻合,验证了封装电设计的合理性。

3D-SiP;信号/电源完整性;陶瓷封装

1 引言

随着电子产品朝着小型化、高密度集成、多功能和高性能的方向不断发展,系统级封装(System in Package,SiP)作为集成的重要技术,得到了越来越广泛的关注和应用。系统级封装技术是将多个不同功能的元器件通过不同的技术集成在一个封装体内,形成具有系统或子系统功能的单颗封装件,具有更小的体积、更轻的质量,且相较于系统级芯片具有研制周期短、集成度及可靠性高等优点[1]。

本文拟通过某型号数字信号处理系统采用上下腔、3D叠层的气密性陶瓷封装结构,运用Cadence Release 16.3及SIwave5软件对其信号/电源完整性进行设计、仿真分析,并根据仿真结果对其进行优化,最后研制生产出产品并进行测试,将测试结果与仿真结果进行对比,以验证电设计合理性以及与产品实现的一致性。

2 3D-SiP产品方案设计

该型号数字信号处理系统主要包含DSP、FPGA、SRAM、FLASH及信号调制解调芯片等,共17个裸芯片与46个阻容器件,其电路功能框图如图1所示。芯片最高工作频率200 MHz,输入电平为3.3 V TTL电平(RS422差分电平除外),要求供电电源电压为3.3 V±0.5 V,输出高电平大于2.4 V、低电平小于0.5 V,且输出的RS422差分电平信号应符合RS422标准。

图1 某型号数字信号处理系统的电路功能框图

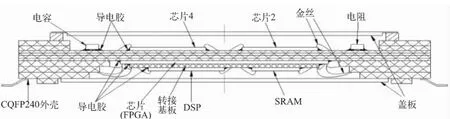

产品采用陶瓷封装,采用400 MPa抗弯强度的高温共烧多层氧化铝陶瓷外壳技术,设计有独立的气密性上下腔体、引出采用四边扇出方式,采用3D叠层工艺,封装体为大小35 mm×32 mm的0.50 mm节距CQFP240。陶瓷封装结构及布局如图2和图3所示。封装下腔包括FPGA、DSP、SRAM、FLASH芯片,采用转接基板加3D叠层方式实现。由于FPGA芯片尺寸最大,将FPGA芯片放在下腔的最底层;同时根据SRAM、FLASH、DSP芯片的大小及芯片叠层的技术要求,在FPGA芯片上首先叠一个转接基板,然后再在转接基板上组装SRAM、FLASH、DSP芯片。封装上腔包括图1中的芯片1~芯片4,及需要内置的46个电阻电容。

图2 陶瓷封装结构示意图

图3 陶瓷封装布局图

根据转接基板及HTCC陶瓷外壳制作工艺要求,在考虑设计规则和组装工艺的基础上,进行裸芯片互连转接基板设计及陶瓷外壳设计。转接基板为硅基板,最终设计尺寸为14.71 mm×14.71 mm,通过硅基转接板用键合丝实现FPGA与SRAM、FLASH、DSP之间的互连,以及与HTCC外壳之间的互连。FPGA芯片采用导热导电胶与下腔底固定,硅基转接板采用导热绝缘胶与FPGA芯片固定。上腔裸芯片采用导热导电胶与上腔底固定,亦采用键合方式与外壳键合指互连;电阻电容均采用导热导电胶与上腔底固定。陶瓷封装下腔封帽工艺采用平行缝焊,上腔封帽工艺采用合金熔封;外引脚采用模具成型/剪边。

3 3D-SiP产品电设计

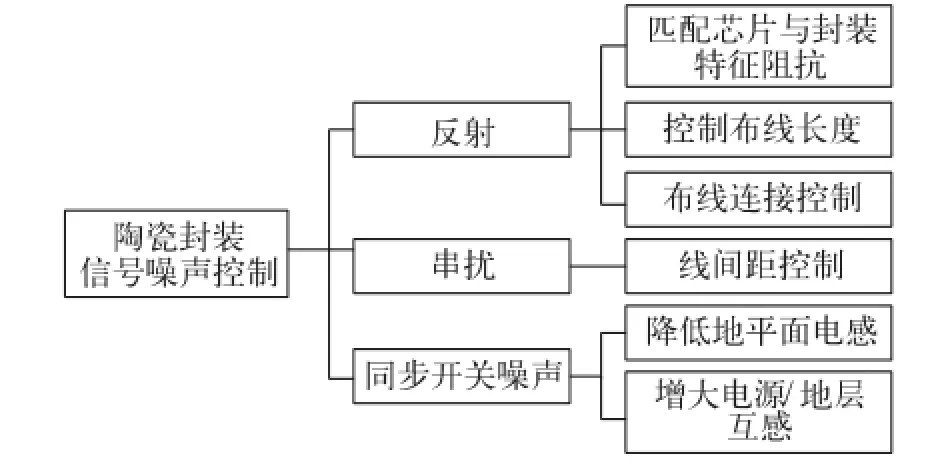

对于介电常数较高的陶瓷封装,由多种因素引起的信号噪声将对电路的信号/电源完整性产生无法忽视的影响[2]。从本质上看,信号噪声源于传输线本身存在的寄生电阻、电容、电感与电信号的相互作用,最终导致一系列信号质量下降、参考电位不稳定等问题。陶瓷封装互连中的信号噪声包括反射(会引起上冲、下冲和振铃效应)、串扰和同步开关噪声(包括电源弹跳和地弹跳,即SSN)等。反射产生于电互连阻抗不匹配处,串扰产生于信号互连线间电磁场的相互干扰,同步开关噪声是由于电源和地网络阻抗及电源/地层布局不合理[3]。

图4 陶瓷封装信号噪声控制方法

在进行陶瓷封装布线设计时,从防反射、防串扰、降低同步开关噪声3方面对信号噪声进行控制,如图4所示。首先是注意芯片与封装特征阻抗的匹配,保证走线尽量为芯片引出端到封装引出端之间的距离最短,避免走线衔接处呈90°,尽量采用135°或圆弧过渡连接,降低反射噪声;并对关键信号控制线间距或以正交方式走线,减小电磁耦合面积,以降低串扰噪声;同时增大电源/地层互感,并保证相邻信号走线在地平面有完整投影,以降低同步开关噪声。

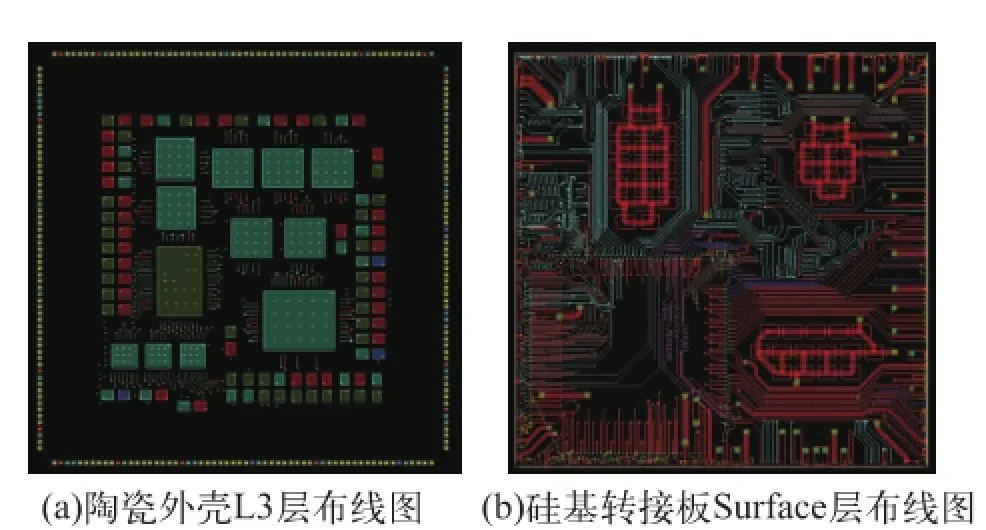

3D-SiP陶瓷封装布线设计由硅基转接板和陶瓷外壳两部分组成。其中,硅基转接板设计为两层布线,最小线宽间距均为10μm;HTCC陶瓷外壳布线设计为24层布线,最小线宽间距均为100μm。硅基转接板和陶瓷外壳剖面示意图如图2所示,典型布线图如图5所示。

图5 产品布线示意图(部分)

4 封装电性能仿真分析

在陶瓷封装布线设计完成后,利用仿真软件从信号完整性及电源完整性两个方面对封装进行仿真分析,根据仿真分析结果对陶瓷封装设计进行优化,确保信号走线的合理布局,改善陶瓷封装的电性能,使本设计能够满足该型号数字信号处理系统的设计要求。

4.1 信号完整性仿真分析

产品要求输出高电平大于2 V或2.1 V(Flash信号),低电平小于0.8 V。通过信号完整性仿真验证整个链路系统信号的合理性。仿真利用Cadence公司的SiP Digital SI XL 16.5以及Ansoft公司的SIwave5仿真软件。根据信号的走向将所要仿真的信号分成5类,即DSP到FPGA信号、DSP到BGA信号、FPGA到SRAM信号、FPGA到FLASH信号及FPGA到PROM信号。

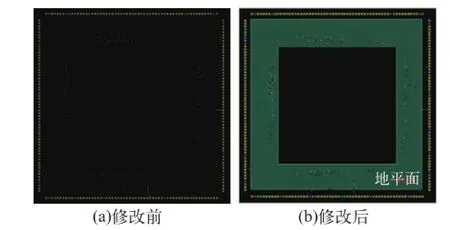

图6所示为信号完整性仿真波形图,图中3种波形分别代表Slow、Typical、Fast 3种环境状态下的波形,即低温高压、常温常压、高温低压,虚线为判断标准。图6(a)为设计优化前时钟信号ECLKOUT的仿真波形图,由该图可以看出该信号存在较大的过冲及振铃。图7和图8为陶瓷外壳布线图修改前和修改后的情况,图中圈出标注处信号为ECLKOUT,由于目前设计该net没有参考面,因此在L14层该net下方铺一层地平面为参考平面。由图6(b)信号波形可以看出,进行上述优化后的信号质量得到很大的改善。

图6 信号完整性仿真波形图

图7 陶瓷外壳L15层布线修改前后变化

图8 陶瓷外壳L14层布线修改前后变化

对产品各类信号分别进行仿真,并根据仿真结果进行相应优化,最终仿真结果表明,尽管有些波形存在一定的过冲及振铃,但是波形整体良好,满足产品设计要求。

4.2 电源完整性仿真分析

电源噪声不仅会对芯片本身工作状态产生影响,还会影响时钟系统,引起时序匹配问题等,通过电源完整性仿真验证使电源系统更加稳健。仿真利用Cadence公司的SiP Digital SI XL 16.5以及Ansoft公司的SIwave5仿真软件。

4.2.1 谐振分析

在高频时,由于分布电感ESL的影响,电源、地平面相当于一个谐振腔,具有谐振特性[4]。图9中所示是一块完整的封装基板模型,从图中我们可以看到,电源平面其实可以看成是由很多电感和电容构成的网络,也可以看成是一个共振腔,在一定频率下,这些电容和电感会发生谐振现象,从而影响电源层的阻抗。随着频率的增加,电源阻抗是不断变化的,尤其是在并联谐振效应显著的时候,电源阻抗也随之明显增加,进而造成电源的不稳定。

谐振分析主要是在信号工作频段范围(210 MHz)内,查看电源平面是否有谐振点出现,在设计中要避免信号走在发生谐振幅度最高的位置附近。若无法避免,则需要在发生谐振幅度最高的位置附近增加去耦电容来改变谐振频点的分布[5]。

图9 封装基板等效模型图

首先选择要分析的电源平面及对应的参考地平面,然后根据仿真出的谐振频点查看谐振分布图。图10和图11分别为L6-5VB、L9-3.3V层谐振图,本文仿真列出5个谐振频点,图中显示的是谐振幅度最大的谐振频点处的谐振图。由谐振图可以看出,在信号工作频段内(210 MHz以内),各电源平面没有出现谐振点。

图10 L6-5VB层谐振图

图11 L9-3.3V层谐振图

4.2.2 关键IC芯片Z阻抗分析

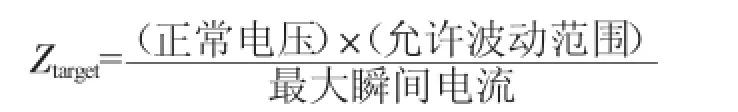

目标阻抗主要考虑的问题有基板叠层方案、滤波电容的选择和放置、电源分割等[6]。进行Z阻抗设计,需要根据要求给出一个目标阻抗:

大部分数字电路器件对电源波动的要求在正常电压的±5%范围之内。最大瞬态电流为芯片上电稳态后的电流与最大峰值电流差值(更严格的设计为最大工作电流,实际上多数芯片有上电过程,不可能从零直接到峰值)。最大瞬态电流ΔI是与频率相关的值,即包含直流分量和交流分量,在直流情况下,由于Z变成了纯电阻,低阻就对应了低的电源供电IR压降,在交流情况下,低阻能使开关电流产生的瞬态噪声也变小,因此,Ztarget是频域参数。

根据上述目标阻抗计算公式计算目标阻抗,其中电压允许波动范围取5%,最大瞬间电流由各电源功耗除以对应电压值得到,系统要求在信号工作频段,Z阻抗不超过目标阻抗值。此仿真主要分析5 V及3.3 V电源平面的Z参数。

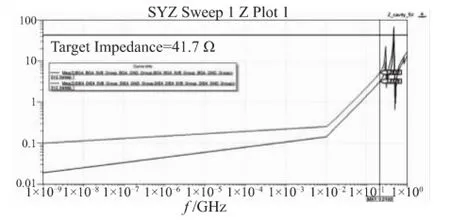

5 V电源网络目标阻抗为41.7 Ω,仿真结果见图12,满足设计目标要求。

图12 5 V电源Z阻抗曲线

3.3 V电源网络目标阻抗为0.162 Ω,将原来10个0.1 μF电容改为4个100 pF、5个1 nF和1个0.1 μF的电容,Z阻抗有一定的降低,但还未达到目标阻抗,仿真结果见图13。对于该电源,需要在封装基板周围增加去耦电容,对于所加的电容容值建议均使用0.1μF,且应在该电源网络输出管脚处至少添加一个去耦电容,具体数量可根据实际布板情况增减。

图13 3.3 V电源Z阻抗曲线

5 产品研制生产与电参数测试分析

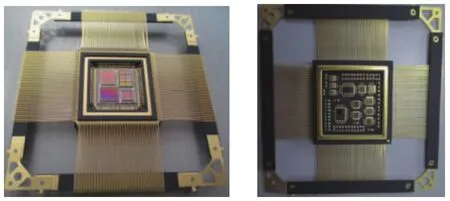

基板与外壳加工制作完成后,与检验合格芯片等元器件一起进行3D-SiP电路封装,封装工艺参数、过程控制严格按封装工艺文件进行;封装生产出的产品进行电参数测试分析,该陶瓷封装产品参见图14。

图14 初样电路

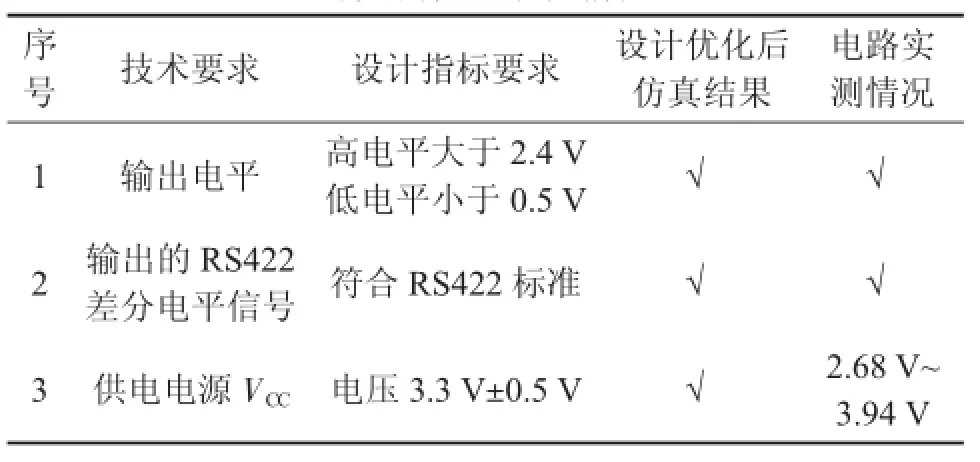

经测试,电路系统在-45℃~+85℃下,芯片最高工作频率200 MHz,系统供电电源电压3.3 V,上下波动不超过0.5 V,输出高电平大于2.4 V,低电平小于0.5 V,实验测试结果与仿真结果一致性良好,电路各项技术指标均可满足系统设计要求,见表1。

表1 3D-SiP产品主要技术指标的设计值与实测值一致性情况

6 结论

本文通过一款上下腔、3D叠层的气密性陶瓷封装的数字信号处理系统产品的设计,利用Cadence Release 16.3及SIwave5软件进行信号完整性仿真分析及电源完整性仿真分析(包括谐振分析和关键芯片Z阻抗分析),并根据仿真结果,采用增加去耦电容、改变走线布局、增加地平面等方式对封装进行设计优化,优化后的仿真结果表明系统具备了较好的信号/电源完整性;产品研制生产后对陶瓷封装的电参数测试分析,结果表明电路各项指标均满足系统的设计要求,与仿真结果相吻合,表明本文基于信号/电源完整性的3D-SiP陶瓷封装设计是合理的。同时,本文基于信号/电源完整性的设计方法也可为后续集成电路三维封装产品的设计提供参考。

[1]耶菲,张军,芦彩香.系统级封装技术研究及实现[J].电脑知识与技术,2015,(11):94-96.

[2]杨轶博,丁荣峥,高娜燕,等.高密度陶瓷封装电设计中噪声控制研究[J].电子与封装,2013,13(9):1-5.

[3]孟辰.高速电路中反射、串扰及SSN的分析与研究[D].西安电子科技大学,2013.

[4]刘学杰,高进.高速印制电路板中电源完整性的优化设计[J].电子科技,2015,28(12):147-149.

[5]肖丹.电源完整性设计中的谐振仿真[J].安全与电磁兼容, 2012,(6):85-88,91.

[6]张建新.高速PCB的信号和电源完整性问题研究[D].西安电子科技大学,2012.

A Design of 3D-SiP Ceramic Package Based on Signal/Power Integrity

ZHANG Rongzhen,GAO Nayan,ZHU Yuan,DING Rongzheng

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

Recently it is a common way to manufacture products of miniaturization,high-density and high-performance using 3D integration technology.The paper presents a design of 3D-SiP ceramic package based on signal/power integrity.The product is of 3D multi-stack air tightness ceramic package structure with the upper and lower cavities.The simulation is performed using Cadence Release 16.3 and SIwave5.After the simulation,the design is optimized.The experimental test results coincide with the simulation.

3D-SiP;signal/power integrity;ceramic package

TN305.94

A

1681-1070(2017)01-0001-05

2016-10-21