一种用于FPGA存储单元的上电复位状态机设计*

2017-02-09徐玉婷董宜平

徐玉婷,耿 杨,董宜平,胡 凯

(1.无锡中微亿芯有限公司,江苏无锡214072;2.中国电子科技集团公司第58研究所,江苏无锡214072)

一种用于FPGA存储单元的上电复位状态机设计*

徐玉婷1,耿 杨1,董宜平2,胡 凯2

(1.无锡中微亿芯有限公司,江苏无锡214072;2.中国电子科技集团公司第58研究所,江苏无锡214072)

基于FPGA芯片,设计实现了一种上电复位状态机。在电路内部产生一系列的复位信号,控制配置存储单元SRAM的数据、地址以及电源,使其在不同阶段保持合适的电压,帮助SRAM在上电过程中顺利完成初始化,提高FPGA芯片启动的稳定性。

FPGA;上电复位;状态机;SRAM

1 引言

FPGA芯片通常包含大量的可配置模块(CLB)、输入/输出块(IOB)和连线资源[1]。可编程的连线结构都是由可配置单元所存储的配置信息所决定的。采用可配置存储单元设计的优势在于减少了用于编程的I/O接口的数量。而且和单端的存储单元相比,可差分的写存储单元结构大大减少了写电路的驱动数量[2]。此外,局部的复位电路也从存储单元中去除,以降低存储单元和I/O接口的复杂性。但是同时,此类I/O接口的简化大大增加了电路上电复位时存储单元初始化的难度。因此,本文采用了一种合理的上电顺序,使得存储单元SRAM的数据、地址以及电源都受上电状态机的控制,保持合适的电压,使得上电复位后,SRAM存储的数据完成初始化,对提高FPGA芯片的安全性和启动的稳定性都有极大的帮助。

2 上电状态机

FPGA芯片中可配置存储单元SRAM的常见结构为六管结构[3],如图1所示。两个PMOS管M3和M4是负载管,主要是用来补偿存储管和开关管漏端电荷的泄放。与M3和M4构成反相器对的两个NMOS管M1和M2是存储管,数据和数据的反分别存放在Q和QN点。而栅极与字线(WL)相连的两个NMOS管M5和M6起开关的作用,BIT和BITN为两条位线。SRAMVDD为SRAM提供电源。

图1 SRAM六管结构图

为了提高FPGA芯片的安全性和启动的稳定性,本文采用的FPGA电路上电顺序分为以下几个步骤:

(1)接通电源,上电复位电路开始检测电源电压;

(2)SRAM单元在电源电压上电时完成第一次初始化;

(3)SRAM的电源电压SRAMVDD保持为零,数据输入端保持为零;

(4)所有SRAM的第一地址驱动电压生效,上拉到FPGA内核电源电压;

(5)将所有SRAM的电源电压偏压到VDD;

(6)通过LDO电路开始调整SRAM的电源电压到VLDO;

(7)FPGA芯片开始正常的配置操作。

当电源电压缓慢上升时,上电检测电路开始工作,同时所有的SRAM由于QN和Q负载的不同,SRAM出现第一次自动的初始化,内部Q存储的数据变为0或1。此时SRAM中存储的状态均为确定值,可大大减小上电时SRAM的电流。电源上电检测完成,上电复位信号POR_TRIP由高电平跳变成低电平,此时状态机开始工作,产生一系列复位信号,时序图如图2所示。在时间点A之前,SRAM的电源电压SRAM VDD保持为零,字线WL的驱动电压WL_VS保持为零,SRAM的数据输入端保持为零。POR_1发生跳变后,WL_VS被上拉到FPGA内核电源电压1.1 V。在时间点B,SRAM VDD偏压到偏置电压,BIT端依然保持为零,此时SRAM阵列根据从地址译码器接收到的地址,逐列打开WL,对SRAM阵列进行第二次初始化,将BIT端的数值0逐列写入SRAM单元,从而保证每一位配置存储器存储的数据均为0。由于大部分SRAM单元在第一次初始化时内部存储的值已经为0,因此第二次初始化只有小部分的值需要从1改写为0,这也大大减小了改写时SRAM的电流。从时间点C开始,SRAMVDD电压逐步偏压到LDO的输出电压。在时间点E,WL_VS电压也略微升高,始终高于SRAM VDD。FPGA芯片开始正常的配置操作,可重新按需求对SRAM进行配置。

图2 上电复位信号时序图

3 设计实现

基于上述上电复位的过程,FPGA芯片中的上电状态机实现如图3所示。

图3 上电状态机控制框图

POR上电检测完成后的复位信号触发POR状态机开始工作,POR状态机产生一组复位信号分别控制LDO模块、配置控制器、地址驱动模块。其中LDO模块用于产生SRAM的电源SRAM VDD,地址驱动模块用来产生SRAM的字线WL的地址,配置控制器则负责将数据传递到DSR模块,通过DSR模块传输到SRAM的BIT端和BITN端。

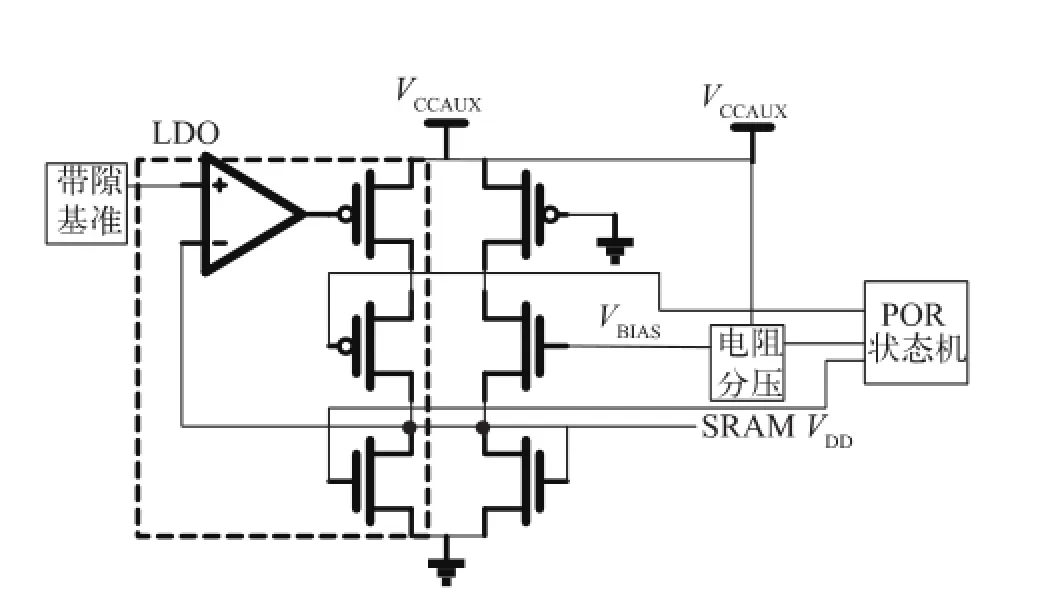

SRAM的电源电压产生电路LDO模块的设计基于低功耗考虑,采用可挂起的模式,具体结构见图4。

图4 LDO结构图

根据图2所示的上电复位流程,SRAM的电源电压SRAM VDD受状态机的控制,分为4个阶段。一开始,SRAM VDD保持为0;后来,SRAM VDD的值由图4右侧的电路产生,其中VBIAS的电压由POR控制的电阻分压电路产生,此时SRAM VDD电压偏低,记为Vbias_out。随后图4中左侧LDO开始工作,SRAM VDD电压逐渐变为LDO提供,此时SRAM VDD的值高于Vbias_out,记为VLDO。

4 仿真验证

在SMIC 40 nm工艺下对电路进行了实现,采用cadence的仿真工具spectre对电路进行了仿真,状态机仿真波形如图5所示。电源上电,上电复位检测成功,POR_TRIP由高电平1.1 V跳变到低电平0 V,此时状态机开始工作,依次产生POR_1~POR_5一系列不同延迟的复位信号。

图5 上电复位信号仿真波形

由于电路规模较大,考虑到复位信号延迟时间比较长,下面的仿真模拟了状态机的顺序,缩减状态机的工作时间,对受上电复位状态机控制的LDO进行了仿真,模拟SRAM VDD不同阶段的电压,仿真波形如图6所示。

如图6的仿真波形所示,一开始SRAM VDD的值为0,后来SRAM VDD的值约为1.18 V,当LDO开始工作后,SRAM VDD电压开始上升至1.28 V。

图6 SRAM VDD仿真波形

5 结论

本文采用SMIC 40 nm工艺,设计实现了一种上电复位状态机,在电路内部产生一系列受状态机控制的复位信号,使得存储单元SRAM的数据、地址以及电源都受上电状态机的控制,保持合适的电压有利于SRAM存储的数据在上电时完成初始化。该上电状态机结构已应用于某重点项目工程实践中,可大大减少上电时芯片的启动电流,提高SRAM启动时的稳定性,增强FPGA芯片的安全性。

[1]王道宪.CPLD/FPGA可编程逻辑器件应用与开发[M].北京:国防工业出版社,2004.

[2]Xilinx.Virtex-5 FPGA Configuration User Guide[P].2012.

[3]R JacobBaker,Harry W Li,David E Boyce.CMOS电路设计、布局与仿真[M].北京:机械工业出版社,2006.

Design of Power-on Reset State Machine for FPGA

XU Yuting1,GENG Yang1,DONG Yiping2,HU Kai2

(1.East Technologies,inc.Wuxi 214072,China;2.China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

A design of power-on reset state machine for FPGA is presented in the paper.The state machine generates a set of reset signals to maintain proper voltage for memory cells.It ensures the memory cells initializes successfully during the power-on process and enhances FPGA reliability and stability.

FPGA;power on reset;state machine;SRAM

TN402

A

1681-1070(2017)01-0024-03

徐玉婷(1983—),女,江西南昌人,硕士,工程师,研究方向为千万门级FPGA设计。

2016-6-3

国家科技重大专项资助项目(2015ZX01018101-005)