基于FPGA的多路数据采集与处理系统设计

2016-04-26詹从来丁远超李富贵

詹从来,龙 伟,丁远超,李富贵

南昌大学信息工程学院,江西南昌330031

基于FPGA的多路数据采集与处理系统设计

詹从来,龙伟,丁远超,李富贵

南昌大学信息工程学院,江西南昌330031

摘要:针对血液分析仪需在8 s内完成4路血细胞和1路状态信号数据采集、处理的要求,设计一套基于现场可编程门阵列的多路数据采集与处理系统.系统实现5路数模转换的并行数据采集、数据处理,并通过串行外设接口通讯接口将处理的数据上传至ARM主机.临床试用结果表明,系统数据采集和处理的方法完全满足血液分析仪对测试速度的要求,仪器性能指标达到了国家注册检验的要求.

关键词:信息处理技术;血液分析仪;数据采集;现场可编程门阵列;数模转换器;串行外设接口

传统血液分析仪大多采用ARM作为控制器,在实际应用中每个ARM工作时钟内只能对1路血细胞信号进行采样,造成采样速率慢,易导致线程死锁等现象[1].其次,ARM控制器为串行指令工作方式[2],其有限资源难以完成血液分析仪复杂的控制动作,影响了系统的实时性.另外,随着对血液分析仪检测与诊断水平要求的提高,其控制系统也在不断更新升级,这就要求控制电路具有较好的灵活性,以降低仪器更新升级的成本.

实际测试结果表明,血液分析仪需在1 min内完成单个测试分析动作,包括采集4路血细胞信号和1路状态信号,5路数据总共所占存储空间大小约为110 Mbyte.根据设计开发要求,血液分析仪的单个测试分析动作需在60 s内完成,而控制电磁阀和电机等动作部分占据大量时间,所以留给数据采样及处理的时间仅有8 s左右.若先将采样数据存入同步动态随机存储器(synchronous dynamic random access memory, SDRAM)模块,再统一上传,耗时就会超过设计要求,要想达到设计要求则只能缩短采样时间.采样时间越短,所采集的细胞个数就越少,这时,任何细胞个数的波动都会对细胞整体计数造成很大影响,使仪器性能不稳定.

为解决采样时间、系统可靠性及准确性之间的矛盾,系统采用ARM(管理级)+ FPGA(基础自动化级)的两级控制系统的方法[3-5],本研究选择现场可编程门阵列(field programmable gate array, FPGA)作为血液分析仪控制系统的核心,利用其并行工作特点,在完成多路信号并行采样、数据处理等工作的同时,完成血液分析仪的控制动作,也可满足系统不断更新升级的需要.

1系统总体框架设计

本研究设计的5路并行数据采集、处理系统,如图1.其中,包括4路的白细胞、红细胞、血小板、血红蛋白和1路状态信号(压力、小孔电压和试剂)的数据采集、处理的控制模块共同组成血液分析仪多路数据采集与处理系统[6-8].设计时考虑到节约硬件资源及成本,采用1片8路分时选通的CD4051芯片,用于切换不同的状态检测信号,CD4051的输出端连接到模数转换器(analog to digital converter, A/D)的输入端,完成状态参数的检测.在信号采集的同时,针对不同信号进行对应的数据处理,然后将处理的数据缓存于随机存储器(random access memory,RAM)模块,RAM模块存满后,再通过数据存储控制模块将细胞特征存储于SDRAM中,最后上传至ARM主机.

图1 多路数据采集与处理系统整体框图Fig.1 The overall block diagram of multi channel data acquisition and processing system

2模块设计与实现

2.1A/D芯片的选择与控制

A/D芯片若采用并行数据传输方式,硬件上至少需要14根信号线连接,而选择串行外设接口(serial peripheral interface, SPI)控制方式,硬件上只需3根信号线进行连接,分别为CS、CLK和SDO[9-10];每路A/D至少可节约11个FPGA通用输入/输出(input/output, I/O)端口并简化硬件连线.同时,根据实际测试可知,经过放大后的血细胞脉冲电压幅值约为0.4~5.0 V,频率约为500 Hz~70 kHz,依据采样定理,采样频率必须大于等于信号变化频率的2倍,才能将信号还原,而实际工程上一般都取5~10倍以上.因此,本研究选用TI公司的带SPI控制方式的芯片ADS7883,其采样频率最高可达3×106次/s(million samples per second,MSPS),能更好的复原被采样波形的包络线,提高细胞的识别精度.

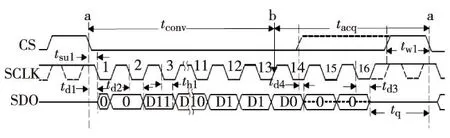

ADS7883工作时序图如图2.工作过程为:当SPI的时钟信号SCLK传送到A/D的SCLK引脚时,A/D开始工作;当SPI的CS下降沿传送到A/D的CS引脚时,开始转换;A/D进行转换操作是在CS为低电平的状态下;当CS上升沿到来时,A/D转换工作结束.A/D进行转换的周期为16帧,但是CS可以在任何时间进行中断(拉高),此时SDO数据线处于3态,CS为高电平.当CS再次变为低电平时开始下一个模/数转换周期,因此每个数据的实际采样周期为18 =(16+2)个时钟.

图2 ADS7883工作时序图Fig.2 The work sequence diagram of ADS7883

图3是血红细胞A/D采样电路原理图.红细胞脉冲微信号经过放大后的电压信号RBC是A/D芯片的输入信号.引脚CS、SDO和SCLK是A/D芯片SPI串行工作方式的3条连接线路,分别为片选、数据线和时钟,分别连接到FPGA对应的I/O引脚上;DAD4是保护A/D芯片的稳压二极管,可限制A/D的输入信号在5 V以下.FPGA接收到A/D转换后的数据后,通过细胞识别模块,利用细胞识别算法进行细胞识别[11],再将识别后的细胞特征值传递给RAM缓存模块进行缓存.

图3 A/D采样模块硬件设计原理图Fig.3 The principle diagram of A/D sampling module hardware design

2.2RAM数据缓存模块的设计

细胞识别模块通过对采样波形的分析,对细胞脉冲进行识别,并记录血细胞脉冲的最大高度和最大宽度,将其缓存于FPGA内置的双口RAM模块中[12].本研究选用的FPGA芯片EP2C20F484C8,其内部RAM模块寄存器转换级(register transfer level, RTL)电路如图4.其中,rdclock为数据读取时钟;wrclock为数据写入时钟;wren为RAM模块的写使能信号;data[15∶0]为16 bit的写入数据;rdaddress[8∶0]为9 bit的数据读取地址信号线;wdaddress[8∶0]为9 bit的数据写入地址信号线;q[15∶0]为16 bit的读出数据.在采样过程中, RAM缓存控制模块收到细胞特征值存储请求后,首先将细胞高度值传递给data[15∶0],然后将数据写使能wren置1,再给一个wrclock写脉冲信号,将细胞高度值写入RAM模块中,同时数据写入地址加1,准备写入下一个细胞特征值.

图4 RTL级双口RAM图Fig.4 The diagram of RTL dual port RAM

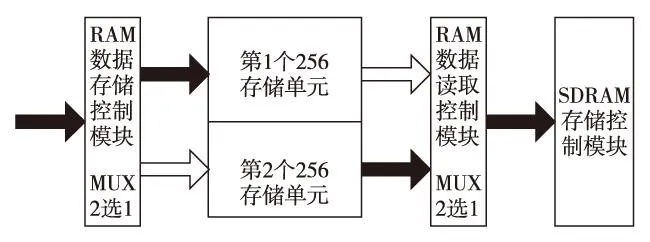

由于实际采样频率为50/18 = 2.78 MHz,而数据传输频率为50 MHz,为了达到采样与存储的时钟匹配,本研究采用数据乒乓存储操作,保证数据的连续性和准确性.具体实现方式为:在设计过程中,先将RAM中512个存储单元,分成2个256存储单元使用.采样开始时,首先将细胞特征值存储于第1个256存储单元,当第1个存储单元存满后,开始将细胞特征值存储于第2个256存储单元,同时,将第1个存储单元的数据,转存到SDRAM中.第2个256存储单元存满后,再将细胞特征值存储于第1个256存储单元,同时,将第2个256存储单元的数据转存到SDRAM中.如此反复操作,实现了数据存储的乒乓操作,既保证了数据存储的连续性,又保证了实时性.数据存储乒乓操作过程如图5.

图5 数据存储乒乓操作过程示意图Fig.5 The schematic of ping-pong operation of data storage

2.3SDRAM存储模块的设计

由于RAM模块仅有512个存储单元,而每路细胞特征值最高可达1×105个数据点,只有4个RAM缓存模块,分别存储不同细胞信号的特征值,因此,当RAM模块存储满后,需将数据进行转存.本研究选择2片Micron(美国镁光)公司的MT48LC16M16A2P芯片进行数据存储[13],其内存带宽为133 MHz,每片存储空间有32 MByte,每片SDRAM芯片对应存储2个RAM模块数据.将SDRAM的各个引脚连接到FPGA相对应的引脚上,并定义好FPGA引脚功能定义,其中,SDRAM的CLK引脚连接到FPGA的锁相环(phase locked loop,PLL)时钟输出引脚上,在实现SDRAM存储时,可通过PLL进行倍频,以提高SDRAM的读写速度.

在采样过程中,数据的存储与读取通过SDRAM控制器实现.由于每片SDRAM模块对应存储2个RAM模块的数据,因此,将SDRAM的32 Mbyte空间分成2个16 Mbyte空间,分别存储2个RAM模块的数据.数据存储时,SDRAM控制器通过切换数据存储地址实现数据的正确存储.采样开始后,SDRAM控制器首先检测第1个RAM模块是否有数据存储请求信号,即req_1是否为1,如不为1,则检测第2个RAM模块是否有数据存储请求信号,即req_2是否为1,如不为1,则再次检测req_1信号.当req_1=1后,则将第1个RAM模块中的数据读出,存储到SDRAM模块中,数据存储完成后,再检测req_2信号.这样就实现了存储完第1个RAM模块的数据后,首先检测第2个RAM模块是否有数据存储请求,保证了每个RAM模块的数据均能及时存储到SDRAM中,避免了数据丢失或阻塞现象.

2.4SPI数据通讯模块的设计

血液分析仪单个分析动作所采集的细胞总数最多约为15万个,处理过程中需取每个细胞的宽度和高度两个细胞特征值,因此,FPGA需反馈给ARM处理器的总数据量最多约为30万个,每个数据点为16 bit,因此总数据量为0.6 Mbyte.根据设计要求,数据上传耗时仅1 s,SPI理论传输速率为25 Mbyte.为保证通讯可靠,本研究采用12 MHz的控制时钟,则SPI传输速率为1.5 Mbyte,因此数据传输完成总时间为0.4 s,可满足设计要求.SPI通讯连接示意图如图6.由于上下位机之间连线较少,因此提高了整个系统的稳定性与可靠性.

图6 ARM和FPGA之间的SPI通讯连接示意图Fig.6 The schematic diagram of SPI communication between ARM and FPGA

FPGA需将采集的数据通过SPI接口上传给ARM进行分析管理,此时ARM作为主机,FPGA作为从机.具体流程如图7,FPGA通过REQ信号向ARM发出数据发送请求;ARM收到请求信号后,启动SPI控制器控制FPGA的SPI模块进行数据发送,再将CS置为0,然后发出16个CLK脉冲时钟,每个CLK的上升沿通过SPI的MOSI向ARM发送1 bit数据,高位在前,低位在后,数据发送完毕后,将CS置为1.FPGA的采样数据均为12 bit,ARM的控制器发出的SPI时钟为16 bit,因此数据发送时,以1个16 bit的数据为1个单位,FPGA中数据不足的位补0,即每发出1个REQ请求信号,上传2 byte给ARM,直到数据传送完为止,停止REQ的请求.

图7 数据传输流程图Fig.7 The flowchart of data transmission

3系统数据验证

为验证系统数据采集及处理的正确性,针对A/D采样部分,本研究以3 V直流电压源为输入到5路A/D行采样,同时运用FPGA编程软件Quartus II[14]自带的SignalTap逻辑分析仪进行在线观测.从A/D采样、AD输入到SDRAM、SDRAM数据存储与读取、SPI通讯4方面对系统进行了测试分析,验证数据的正确性.

3.1A/D采样数据的验证

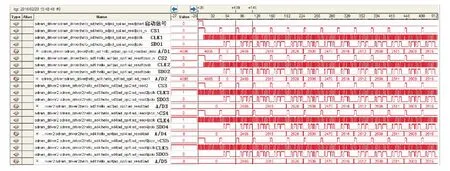

测试过程中输入信号为约3.07 V的直流源,对应的十进制A/D数据为3.07×4 095/5 = 2 514.若5路A/D转换器采集电压值对应的十进制值都在2 514左右范围内,则采样的数据是准确的,否则错误.当控制5路A/D采样的SPI时钟完全同步时,由图8可知,同时段内采集的电压值相同且都在误差允许范围内,说明5路A/D采样的数据准确.

3.2AD输入到SDRAM数据链路验证

为验证从AD输入到SDRAM输出的数据链路的正确性和完整性,采用SignalTab工具观测SDRAM输出数据是否与AD输入保持一致.

图9为SignalTab观测的SDRAM数据输出时序图.其中,S_enable为读SDRAM的使能信号.当S_enable为高电平时,开始读取SDRAM的数据.参考图8可知,SDRAM输出数据与AD输出数据完全一致,无丢失和错码,说明从AD输入到SDRAM输出链路数据正确且完整.

3.3SDRAM数据存储与读取的验证

数据处理完毕,通过将细胞特征值用1~4 095依次递增的循环数进行代替,验证数据存储与读取的正确性与完整性.

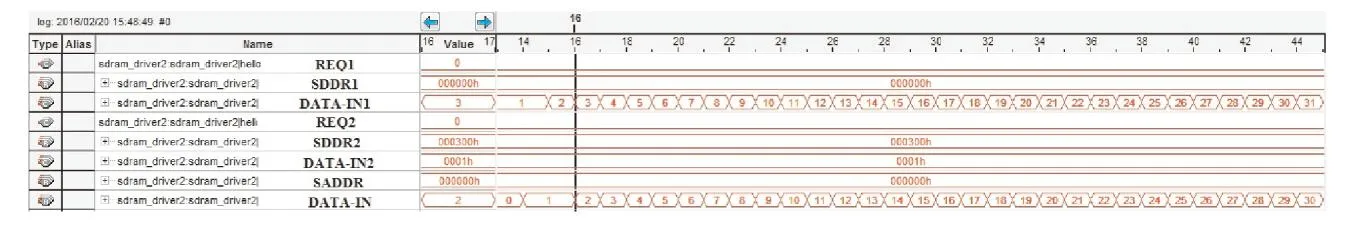

图10为1路RAM模块将256个连续数据存储到SDRAM模块的时序图.当第1个缓存模块r_req发出数据发送请求后,SDRAM数据存储控制模块起始地址为数据存储起始地址saddr1,同时将缓存中的数据存入SDRAM中.由图10可知,data-in寄存器存储数据为1~256,共256个数据.然后,停止数据存储,此时白细胞数据存储起始地址saddr1由开始的0000H变为0100H,共增加了256,数据存储位数和地址变化正确.

为进一步验证数据的正确性,放大后的逻辑分析仪效果图如图11.数据寄存器data-in中的数据由1开始递增变化,数据存储正确.

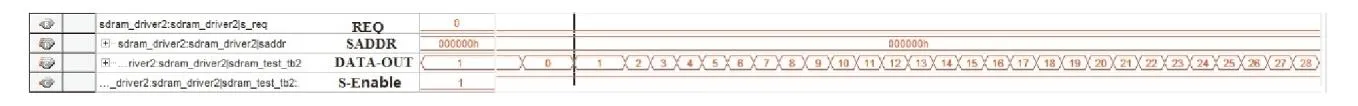

由图12可知,当数据读取请求信号req发出时,SDRAM读取控制器开始读取SDRAM中的数据,每次请求数据读取的总数为256个,同时将数据存储到RAM中.数据读取起始地址由0开始,每读完256个数据,读取的起始地址加256,当读取完4次256个数据后,停止数据读取.因此可知,数据读取个数与数据读取起始地址变化正确.

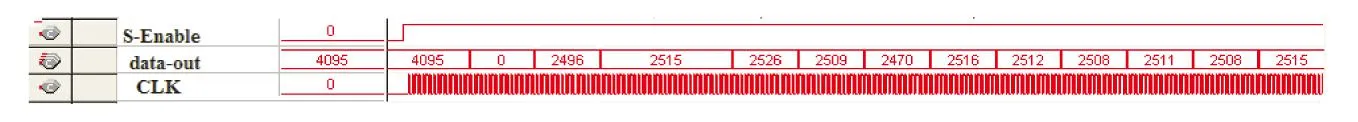

为进一步验证数据读取的正确性,放大后的逻辑分析仪效果如图13.数据输出寄存器data-out中的数据,由1开始依次递增,因此,SDRAM读取出来是正确的,同时也再次验证了存入SDRAM模拟数据的正确性.

3.4数据传输验证

图8 5路A/D同步采样数据验证时序图Fig.8 (Color online) The diagram of sampling data validation sequence for 5-channel synchronous A/D converter

图9 AD输入到SDRAM验证时序图Fig.9 (Color online) The validation sequence diagram from A/D to SDRAM

图10 SDRAM数据存储时序图Fig.10 (Color online) The diagram of SDRAM data storage sequence

图11 放大后数据存储的逻辑分析仪时序图Fig.11 (Color online) The timing diagram of enlarged logic analyzer

图12 SDRAM数据读取时序图Fig.12 (Color online) The diagram of SDRAM data read sequence

图13 SDRAM数据读取的逻辑分析仪观测时序图Fig.13 (Color online) The observation sequence diagram of SDRAM read data logic analyzer

采样结束后,需将SDRAM中的数据通过SPI通讯接口上传给ARM主处理.具体的处理过程为:SPI在ARM主处理器的控制下,首先将CS置为0,然后发出CLK时钟信号,每个CLK的上升沿将数据逐位通过MOSI发送出去,数据发送完后,将CS置为1.由图14可知,数据发送寄存器data-out为依次递增的数列,数据正确且完整,验证了数据发送正确性及完整性.

图14 SPI通讯数据验证时序图Fig.14 (Color online) The validation sequence diagram of SPI communication data

结语

设计一种基于FPGA的多路数据采集与处理系统,实现了5路A/D的并行数据采样、处理的功能.采用A/D芯片的串行SPI控制接口,节省了FPGA的硬件资源;2.78 MSPS采样速度达到了血液分析仪采样速率的要求;乒乓存储操作的方式,良好地匹配了数据采样与存储的时钟.系统不但满足了血液分析仪对数据采集、处理的要求,也可根据实际需求,实现对硬件电路的升级.与传统数据采集系统相比,本系统具有运行稳定可靠、实时性强、灵活性好等特点,对性比价高的血液分析仪的研制具有一定的参考价值.

引文:詹从来,龙伟,丁远超,等.基于FPGA的多路数据采集与处理系统设计[J]. 深圳大学学报理工版,2016,33(2):127-133.

参考文献/ References:

[1] 张海鹏,李曦.操作系统中的死锁检测[J].计算机系统应用,2013,22(10):14-18.

Zhang Haipeng, Li Xi. Deadlock detection in operating system[J]. Computer System & Application, 2013, 22(10): 14-18.(in Chinese)

[2] 邵磊,倪明.基于FPGA的高速数据采集系统设计与实现[J].计算机工程,2011,37(19):221-223.

Shao Lei, Ni Ming. Design and implementation of high speed data acquisition system based on FPGA[J]. Computer Engineering, 2011, 37(19): 221-223.(in Chinese)

[3] 林长青,孙胜利.基于FPGA的多路高速数据采集系统[J]. 电测与仪表,2005,42(473):52-54.

Lin Changqing, Sun Shengli. Multi-channel high speed data acquisition system based on FPGA[J]. Electrical Measurement & Instrumentation, 2005, 42(473): 52-54.(in Chinese)

[4] 于雪莲.基于FPGA的高速数据采集系统的设计[D].保定:河北大学,2014.

Yu Xuelian. FPGA-based high-speed data acquisition system design[D]. Baoding: Hebei University, 2014.(in Chinese)

[5] 刘怿恒.基于FPGA的数据采集与处理系统设计[D].长沙:湖南大学,2013.

Liu Yiheng. The design of data acquisition and processing system based on FPGA[D]. Changsha: Hunan University, 2013.(in Chinese)

[6] 胡雪峰.基于FPGA的电子系统柔性设计[J].现代电子技术,2007,30(8):163-164.

Hu Xuefeng. Flexible design of electronic system based on FPGA[J]. Modern Electronic Technique, 2007, 30(8): 163-164.(in Chinese)

[7] 张小琴.基于FPGA的高速图像数据采集系统设计[D].武汉:武汉理工大学,2010.

Zhang Xiaoqing. Design of high speed digital image acquisition system based on FPGA[D]. Wuhan: Wuhan University of Technology, 2010.(in Chinese)

[8] 李华,刘宝盈,刘萌,等.基于FPGA的多路数据采集与传输系统设计[J].电子测试,2014(18):29-31.

Li Hua, Liu Baoying, Liu Meng, et al. Design of multi-channel data acquisition and transmission system based on FPGA[J]. Electronic Test, 2014(18): 29-31.(in Chinese)

[9] 唐玉蓉.基于FPGA的高速数据采集系统的设计与实现[D].北京:北京邮电大学,2012.

Tang Yurong. Design and implementation of high-speed data acquisition system based on FPGA[D]. Beijing: Beijing University of Posts and Telecommunications, 2012.(in Chinese)

[10] 高鹏.基于FPGA的PCI接口数据采集系统设计[D].镇江:江苏科技大学,2012.

Gao Peng. A thesis submitted in fulfillment of the requirements for the degree of master of engineering[D]. Zhenjiang: Jiangsu University of Science and Technology, 2012.(in Chinese)

[11] 龚莹.基于HHT-SVM的血细胞识别算法研究[D].南昌:南昌大学,2014.

Gong Ying. Research of Identification method for hemocyte on HHT-SVM[D].Nanchang:Nanchang Univer-sity, 2014.(in Chinese)

[12] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

Xia Yuwen. Verilog digital system design guide[M]. Beijing: Beijing University of Aeronautics and Astronautics Press, 2008.(in Chinese)

[13] 周昆正.基于FPGA的SDRAM控制器设计[J]. 现代电子技术,2003,13:63-65.

Zhou Kunzheng. Design of SDRAM controller based on FPGA[J]. Modern Electronic Technique, 2003, 13: 63-65.(in Chinese)

[14] 周润景.基于Quartus II 的 FPGA/CPLD 数字系统设计实例[M].北京:电子工业出版社,2013.

Zhou Runjing. FPGA/CPLD digital system design based on Quartus II instances[M]. Beijing: Electronic Industry Press, 2013.(in Chinese)

【中文责编:英子;英文责编:雨辰】

Design of multi channel data collection and processing system based on FPGA

Zhan Conglai, Long Wei†, Ding Yuanchao, and Li Fugui

Information Engineering School, Nanchang University, Nanchang 330031,Jiangxi Province, P.R.China

Abstract:We present a new multi-channel data acquisition and processing system based on field programmable gate array (FPGA) for hematology analyzers. This system is able to acquire four-channel data of blood cells and process one channel status signal in eight seconds. The digital to analog converter for the total five data channels is implemented in parallel. The processed data are transferred to ARM host via the serial peripheral interface communication protocol. Clinical trials indicate that the new system fulfills the strict requirement for the test speed of hematology analyzers, and its performance meets the national registered inspection standard.

Key words:information processing technology; hematology analyzer; data collection; field programmable gate array; digital to analog converter; serial peripheral interface

作者简介:詹从来(1990—),男,南昌大学硕士研究生.研究方向:计算机控制与嵌入式智能仪表技术.E-mail: 767006719@qq.com

基金项目:国家自然科学基金资助项目(61261011)

中图分类号:C 37;P 413

文献标志码:A

doi:10.3724/SP.J.1249.2016.02127

Received:2015-10-06;Accepted:2016-02-16

Foundation:National Natural Science Foundation of China (61261011)

† Corresponding author:Professor Long Wei. E-mail: jnlwdd@163.com

Citation:Zhan Conglai,Long Wei,Ding Yuanchao,et al. Design of multi channel data collection and processing system based on FPGA[J]. Journal of Shenzhen University Science and Engineering, 2016, 33(2): 127-133.(in Chinese)

【电子与信息科学 / Electronics and Information】