一种千兆以太网SerDes 接口与电接口的转换方法

2016-04-07徐玉杰孟博

徐玉杰 孟博

摘要:该文针对千兆以太网SerDes接口(1000 BASE-X)和电接口(1000 BASE-T)转换的问题,给出了一种基于FPGA的千兆以太网SerDes接口和电接口转换的方法。详细介绍了该方法的硬件架构和逻辑设计,工程应用证明该方法稳定可靠,逻辑设计简单易行,达到了设计的预期目标。

关键词:千兆以太网;高速串行接口;现场可编程门阵列

中图分类号:TP393 文献标识码:A 文章编号:1009-3044(2016)03-0047-02

千兆以太网以其技术先进、使用灵活、便于单元板小型化等优点已广泛应用于背板结构产品,特别是采用信号数量较少的SerDes接口进行单元板间互联已成为主流[1]。而在XX应用环境中,千兆以太网交换设备接口数量受限,在系统调试过程需要调试网口(电接口)与外部计算机进行通信,为了不增加额外以太网接口,本文根据具体的应用设计了一种千兆以太网SerDes接口与电接口的转换方法[2],该方法使一路以太网接口同时具备调试与数据传输的功能,既减少了千兆以太网接口数量又实现了千兆以太网SerDes接口与电接口转换。

1 方案的总体分析

接口转换及其应用的系统结构示意图如图1所示,该系统使用SerDes作为物理层的千兆以太网实现各单元板、接口板和交换板互联。交换板与接口板之间的数据通路在系统调试过程中作为调试网口使用,同时在接口板中完成千兆以太网SerDes接口与电接口的转换,这样即可实现与外部计算机通信;调试完成后通过更改FPGA逻辑将该接口用于数据传输。

该转换方法主要由物理层芯片、FPGA和千兆以太网收发部分组成,其中在调试过程FPGA主要实现两片物理层芯片的配置及互联,在调试完成后按系统要求实现数据传输,本文主要讨论调试过程接口转换的方法。

2 方案详细设计

该转换方法先将千兆以太网SerDes接口转化为GMII接口,调试使用时FPGA主要完成对物理层芯片的GMII接口互联和配置,然后再将GMII转换成传统的千兆以太网电接口;作为数据传输接口使用时,直接在FPGA中增加一个MAC核完成数据传输。方案中使用的主要元器件为物理层收发器88E1111和Xilinx公司的Vertex-5系列FPGA。

2.1 关键元器件介绍

2.1.1 物理层收发器

Marvell的88E1111是一款千兆以太网收发器物理层芯片,采用标准的CMOS工艺制造。88E1111支持用于直接连接到MAC/Switch接口的MII、GMII、RGMII和SGMII四种以太网接口模式。内部集成了一个可选的1.25Ghz的SerDes接口,它包括了千兆以太网物理层PCS、PMA和PDM子层所有的功能,这个接口可直接连接到光纤收发器,器件采用了先进的回声消除、近端串扰抑制等多种手段提高信号质量在经过接收PCS层解码后交付MAC层[3]。其发送端集成了一个多功能的D/A转换器,可以支持4D PAM5、MLT3和曼彻斯特编码,分别支持1000BASE-T、100BASE-TX和10BASE-T的编码[4]。

2.1.2 可编程逻辑器件

该方案中接口转换功能对FPGA的资源要求高,为了不改变原有的系统结构,该方案中FPGA选用Xilinx公司的Virtex-5系列,该系列芯片内部资源丰富,性价比较高。Xilinx公司提供嵌入式以太网MAC核,符合IEEE Std 802.3标准[5],满足该设计的应用需求。

2.2 硬件详细设计

千兆以太网SerDes接口与电接口的转换是由物理层芯片和FPGA芯片之间交互实现的,其硬件设计的关键在于元器件之间的接口互连,图2为关键元器件接口互联的示意图。

第一个物理层芯片对外传输方式选择使用SerDes接口,物理层传输协议使用1000BASE-X,使用GMII接口和FPGA相连,其工作模式设置为强制1000BASE-X全双工模式。

第二个物理层芯片工作模式设置为强制1000BASE-T全双工模式,物理层传输协议使用1000BASE-T,使用GMII接口和FPGA相连,电接口通过变压器后与RJ45(外部PC机)相连。

这种转换方法硬件设计较为复杂,但设计中两个物理层芯片均与FPGA相连,可根据具体的应用在调试阶段将交换板与接口板之间的数据通路作为调试使用,待调试完成后只需要在FPGA中增加MAC层,该数据通路即可作为数据传输使用。

2.3 FPGA逻辑设计

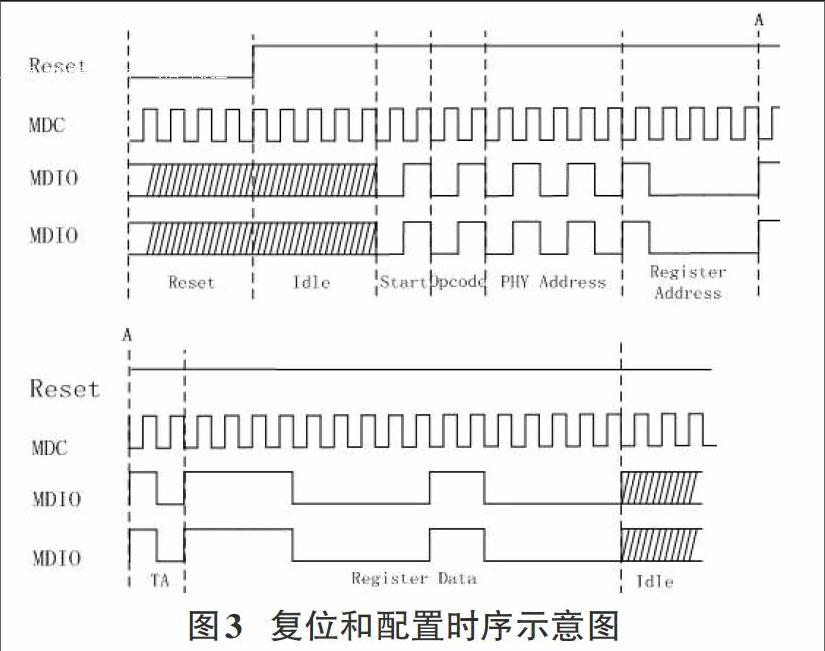

本文描述的方法中FPGA逻辑主要实现两个物理层芯片的复位、GMII接口互联和配置功能。其中两个GMII接口直接进行互联,复位通过对物理层芯片的RST控制完成,配置通过串行管理接口(MDC/MDIO)完成,图3为复位和配置的控制时序示意图:

复位和配置的流程如下:

a.上电后分别对两个物理层芯片进行复位。

b.复位完成后对两个物理层芯片进行配置,本文配置时序示意图中两个配置接口的时钟MDC均为4Mhz,将第一个物理层芯片配置成1000 BASE-X 全双工模式,将第二个物理层芯片配置成1000 BASE-X全双工模式。

c.通过第二步将配置信息写入配置寄存器,再对两个物理层芯片进行软复位,软复位完成后配置即可生效,整个配置过程完成。

在实际应用中,系统在上电复位完成后可根据具体的应用对物理层芯片进行配置。为了查看配置是否正确,可在对芯片软复位之前读取配置信息,确认配置无误后再进行软复位,使配置生效。

3 实验与验证

对本文提出的接口转换方法进行功能和性能验证,根据图4搭建了系统验证测试平台:

将计算机的IP 地址设置为192.168.1.1,第N个单元板的IP 地址设置为192.168.1.N,将调试接口和计算机使用网线进行连接。单元板与交换板之间用SerDes进行连接。加电启动完毕后,通过查看交换板的网络管理和计算机的网络连接,发现计算机和交换机连接的网口都为1000Mbps 连接。在计算机上发起ping 包测试,测试结果如下表所示。通过测试可以看出,丢包率满足小于0.1%的要求。

验证测试平台中计算机通过接口板和交换板向系统中的其它模块发送数据,各模块接收到数据后返回给计算机,在计算机中进行数据比较并统计速率,经测试,数据传输正确,速率达到了76MB/s。

上述测试表明本文所提出的方法可以实现SerDes信号与电接口的转换。

4 结束语

经过工程应用验证,使用该方法的硬件平台工作稳定可靠、FPGA逻辑设计简单易行,使用灵活。虽然该方法硬件电路比较复杂,但该方法减少了千兆以太网接口数量又实现了千兆以太网SerDes接口与电接口转换,达到了设计的预期目的。

参考文献:

[1] 潘波,朱伟,袁静.基于SerDes 的千兆以太网设计与实现[J].微处理机,2014(2).

[2] 于洪涛,丁铁夫,郑喜凤,等.基于FPGA的千兆以太网光纤转换器的设计[J].中国光学与应用光学.2009(8).

[3] 张磊.基于千兆网口的星敏感器图像显示和存储[J].液晶与显示,2014(6).

[4] 88E1111 Datasheet Integrated 10/100/1000 Ultra Gigabit Ethernet. USA: Marvell February 2006,10.

[5] Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC user guide. USA: Xilinx February 2011,14.