基于ARM+FPGA的BD2接收机设计与实现

2015-06-21纪元法孙希延

王 超,纪元法,2,孙希延,2

基于ARM+FPGA的BD2接收机设计与实现

王 超1,纪元法1,2,孙希延1,2

(1.桂林电子科技大学信息与通信学院,广西桂林 541004; 2.桂林电子科技大学广西无线宽带通信与信号处理重点实验室,广西桂林 541004)

为了接收北斗卫星B2频点信号,设计了一种基于ARM+FPGA的BD2接收机。该设计采用MAX2112和MAX1003分离元器件构建射频前端模块,辅以基带信号处理模块、通讯模块和电源模块搭建了接收机的硬件平台。在硬件平台的基础上,设计了ARM和FPGA的软件功能。测试结果表明,设计的样机能够正确捕获跟踪B2频点信号,经度标准差为1.5 m,纬度标准差为5.1 m,高度标准差为4.4 m,定位精度达到了设计目标。

BD2接收机;MAX2112;ARM;FPGA

随着北斗ICD文件的公布以及相关技术的不断发展,依托国内外市场需求和政府的支持,北斗卫星导航二代系统(BD2)已经具备初步的区域服务能力,其应用遍及航海、航空、交通、资源勘探等领域[1]。北斗卫星导航系统(BDS)发射B1、B2、B3频点信号,在民用领域针对兼容B1频点信号的北斗导航终端开发应用较多,而对B2频点信号的北斗导航终端开发和利用B1、B2双频信号实现与生命安全相适应的高精度和完好性服务需求提上了日程[2]。鉴于此,设计了一种基于ARM+FPGA的BD2接收机,在保证北斗卫星B2频点信号处理实时性的同时,提高了系统的集成度和稳定性。

1 接收机的硬件设计

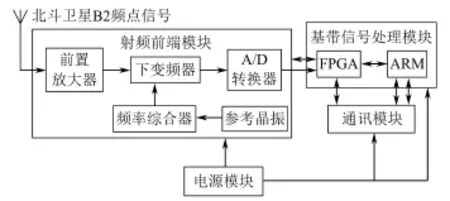

为了实现终端定位功能,BD2接收机将北斗卫星信号下变频混频并进行数字采样,使包含B2频点的信号调制在中频载波上,后级基带信号处理单元完成信号的捕获、跟踪、解调导航电文和提取观测量[3],最终将定位结果传输至上位机。在充分考虑系统的实时性和硬件稳定性的基础上,采用MAX2112、ARM和FPGA为核心搭建了BD2接收机的硬件平台,该平台主要由射频前端模块、基带信号处理模块、通讯模块和电源模块组成[4],如图1所示。

图1 BD2接收机的结构Fig.1 The structure of BD2 receiver

1.1 射频前端模块

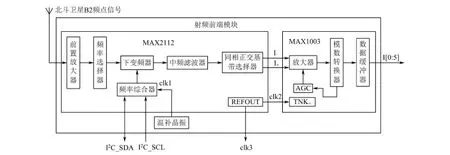

北斗卫星B2频点信号频率为1207.14 MHz,信号传播至天线接收端时功率微弱且掺杂了噪声和干扰,因此采用射频前端模块对信号进行调整、滤波、下变频混频、信号放大和模数转换,并将其离散成包含B2频点信号成分的数字中频信号[5]。射频前端模块采用MAX2112、MAX1003芯片分离元器件协同处理。MAX2112芯片集成了低噪声放大器、射频可变增益放大器、I/Q两路下变频混频器、可编程的7阶巴特沃斯滤波器以及数控可变增益的基带放大器[6]。该芯片采用2线I2C总线接口编程配置中频频率,将925~2175 MHz的射频信号直接下变频至I/Q两路中频频率。MAX1003为低功耗、双通道6位转换精度和采样速率高达90 Mbit/s的模数转换芯片,最大输入50 MHz带宽模拟信号,可满足接收机高速采样和低功耗的要求。

射频前端模块如图2所示,它由温补晶振提供16.368 MHz时钟源clk1,经过MAX2112芯片的REFOUT引脚输出频率为16.368 MHz的clk2和clk3时钟信号,clk2时钟信号提供给MAX1003芯片的TNK+引脚作为数据采样时钟,clk3时钟信号提供给基带信号处理模块的FPGA作为系统时钟源。

图2 射频前端模块Fig.2 RF front-end module

FPGA采用I2C总线方式配置MAX2112芯片,将北斗卫星B2频点信号下变频混频至模拟中频信号,在I2C总线中,I2C_SDA为串行数据线,I2C_SCL为串行时钟线。然后利用MAX1003芯片进行模拟中频信号数据采样,输出2.046 MHz的6 bit数字中频信号I[0:5],最终截取高2位量化电平传输至基带信号处理模块。

1.2 基带信号处理模块

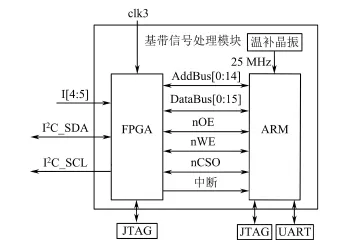

基带信号处理模块如图3所示,它不仅完成北斗卫星B2频点信号解扩时大量相关运算,同时实时提取原始观测数据和导航电文参数,进而解算接收机位置。考虑系统功耗、体积、成本和可靠性需求,基带信号处理模块采用ARM高速处理器和FPGA可编程逻辑控制器处理架构。

图3 基带信号处理模块Fig.3 Baseband signal processing module

ARM采用STM32F205RET6芯片,该芯片集成了1 MB Flash存储器、128 kB的SRAM、UART、FSMC、RTC等资源,使得接收机设计更加灵活,同时其拥有高速运算性能,满足了系统的运算处理要求。FPGA采用EP4CE115F28C8N芯片,该芯片拥有114 480个逻辑单元、266个18×18乘法器和3.888 Mbit的嵌入式存储器,可满足16个相关通道的并行运算。

接收机实现精确定位必须依靠精准的时钟信号,普通晶振容易受环境、温度等因素的影响[7],基带信号处理模块采用温补晶振为接收机提供精准时钟源,其中ARM输入时钟为25 MHz,通过内部倍频至100 MHz工作频率,保证与FPGA、上位机等数据交互处理的实时性。为保证射频前端信号采样和基带处理模块时钟同源,FPGA从射频前端模块获取输入时钟clk3的频率为16.368 MHz,通过内部PLL倍频至130.944 MHz,满足接收机设计相关通道的时序控制要求。

ARM通过GPIO口模拟FSMC总线,与FPGA进行15位地址总线和16位数据总线交互。其中: n OE为读使能端;n WE为写使能端;nCSO为片选地址线。FPGA利用内部的时钟管理模块输出基准时钟,基带信号作为ARM的外部中断输入源,使ARM和FPGA共同完成捕获、跟踪等基带信号处理。

1.3 通讯模块

通讯模块采用2个JTAG和1个UART与外界进行通讯。ARM和FPGA利用JTAG接口进行在线编程、程序下载和调试开发。ARM配置其UART内部功能模块,实现接收机的定位信息传输至上位机,其中数据传输格式的波特率配置为115.2 kbit/s, 8位数据位,1位停止位,无奇偶校验位。

1.4 电源模块

电源模块对接收机工作的稳定性至关重要。系统电源分为5.0、3.3、2.5、1.2 V四种,系统输入电源为5 V/2 A,其他电压均为5 V。ARM I/O供电电源为3.3 V;FPGA供电需要3种电源:内核电源(1.2 V)、I/O电源(3.3 V)、模拟电源(2.5 V); MAX2112供电电源为3.3 V;MAX1003供电电源为3.3 V。

电源模块采用AMS1117、XM5151芯片提供系统电源,AMS1117芯片是一款低压差线性稳压器,内部集成过热限流保护,可固定输出2.5、3.3、5.0 V电压。XM5151是一款具有固定工作频率的同步降压转换芯片,最高可输出1.5 A电流,能够输出0.6~5.0 V的电压。系统电源中XM5151配置输出1.2 V电压供电给FPGA,其他均由AMS1117配置供电。

2 接收机的软件设计

接收机的软件设计主要由基带处理模块中的核心器件协同完成,软件设计按芯片处理功能分为ARM主控制端和FPGA协处理端[8]。软件设计结构如图4所示。

图4 软件设计结构Fig.4 The structure of software design

2.1 ARM主控制端

ARM主控制端作为基带处理的核心计算单元,主要由捕获策略模块、跟踪策略模块、同步解调电文模块和定位解算模块组成。

捕获策略模块为FPGA分配捕获卫星列表和通道,接收FPGA捕获卫星的FFT相关峰值做捕获门限判决,组装捕获卫星的多普勒频移和码相位信息,为FPGA的跟踪模块输送载波NCO初始值和码NCO初始值。

跟踪策略模块负责接收FPGA传来的相关积分值,对载波跟踪环路和码跟踪环路进行鉴频鉴相滤波,实时更新FPGA的跟踪模块载波NCO值和码NCO值,与FPGA共同完成信号的载波剥离和码剥离[]。

同步解调电文模块在接收机完成捕获、跟踪北斗卫星B2频点信号后,对信号进行位同步、帧同步和BCH译码,组装获取卫星信号发射时间等相关信息。

定位解算模块提取伪距和计算卫星位置,通过构建伪距测量方程实时更新导航定位的解,将定位信息输送至上位机显示。

2.2 FPGA协处理端

FPGA协处理端作为基带信号的相关处理单元,主要由配置射频模块、捕获模块和跟踪模块组成。

配置射频模块通过I2C总线配置MAX2112芯片,完成北斗卫星B2频点信号直接下变频至设置的中频频率。

捕获模块对射频前端模块输入的2位量化电平信号进行捕获,将捕获卫星的多普勒频移、码相位和FFT峰值等信息输送至ARM捕获策略模块做判决。

跟踪模块对北斗卫星B2频点信号实时进行载波剥离和码剥离。接收ARM捕获策略传来的载波NCO初始值和码NCO初始值,将信号剥离后的相干积分值输送至ARM跟踪策略模块,与其构成闭环,实时更新载波NCO和码NCO值[10]。

3 测试结果

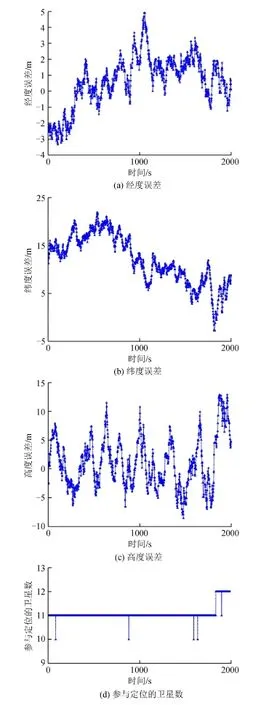

根据硬件方案设计样机,首先对射频模块、基带信号处理模块、通讯模块和电源模块进行整机测试,样机可以正常工作,验证了方案设计的合理性。结合接收机软件功能,利用北斗卫星B2频点信号对样机进行静态测试,将Nov Atel公司的703-GGG有源天线固定于已知的标定点,标定点坐标为东经110.331 508 3°、北纬25.285 481 6°、高度为166 m。北斗卫星B2频点信号的定位结果如图5所示。

从图5可看出,设计的BD2接收机可以正确捕获、跟踪北斗卫星B2频点信号,且能将定位结果传输至上位机。BD2接收机的经度标准差为1.5 m,纬度标准差为5.1 m,高度标准差为4.4 m,定位精度达到了预期的目标。在测试过程中参与定位的卫星数在10颗以上,验证了该方案的可行性。

图5 北斗卫星B2频点信号的定位结果Fig.5 The positioning results of BeiDou B2-frequency signal

4 结束语

为了接收北斗卫星B2频点信号,提出了一种基于ARM+FPGA的BD2接收机设计方案,完成了BD2接收机的软硬件设计。测试结果表明,该设计方案合理可行,所设计的样机能够正确捕获、跟踪北斗卫星B2频点信号,定位结果的经度标准差为1.5 m,纬度标准差为5.1 m,高度标准差为4.4 m,定位精度达到了预期目标,为利用B1、B2双频信号实现高精度定位积累数据和经验。相比使用功能单一的射频集成芯片,采用MAX2112、MAX1003分离元器件构建的射频前端模块,使得方案设计更灵活、适用范围更广,为多频/多模接收机的设计提供解决思路。

[1] 陈洪卿.北斗系统与中国PNT应用平台[J].电子测量与仪器学报,2010,24(12):1075-1081.

[2] 谭述森.北斗卫星导航系统的发展与思考[J].宇航学报,2008,29(2):391-396.

[3] 张婷,陈秀万,朱庄生,等.GNSS软件接收机的框架结构及原型系统开发[J].计算机工程,2008,34(7):266-268.

[4] 王尔申,孙晓文,胡青,等.卫星定位信号接收机系统研究与设计[J].微计算机信息,2008,24(13):200-202.

[5] 中国卫星导航系统管理办公室.北斗卫星导航系统空间信号接口控制文件公开服务信号B1I(2.0版)[EB/OL]. (2013-12-26)[2015-01-12].http://www.beidou.gov.cn/ attach/2013/12/26/2013122604a521b35b7f4a54b44cfbbc 8abd74a8.pdf.

[6] 刘辰.基于北斗收发系统的前端研制[D].合肥:安徽大学,2012:82.

[7] 薛涛,赵伟,李荣冰,等.北斗导航接收机的硬件设计与实现[J].航天控制,2015,33(1):94-98.

[8] 刘竞超,邓中亮.基于ARM+FPGA北斗接收机设计[J].软件,2012,33(12):38-40.

[9] 谢钢.GPS原理与接收机设计[M].北京:电子工业出版社,2009:236-263.

[10] 谷卓,杨皎皎.一种北斗接收机基带处理设计方案[J].信息通信,2013,126(4):55-56.

编辑:曹寿平

Design and implementation of BD2 receiver based on ARM and FPGA

Wang Chao1,Ji Yuanfa1,2,Sun Xiyan1,2

(1.School of Information and Communication Engineering,Guilin University of Electronic Technology,Guilin 541004,China; 2.Guangxi Key Lab of Wireless Wideband Communication and Signal Processing, Guilin University of Electronic Technology,Guilin 541004,China)

In order to receive B2-frequency signal of BeiDou satellites,BD2 receiver based on ARM and FPGA is designed. The design adopts MAX2112 and MAX1003 separation components to build RF front-end modules,combining with the baseband signal processing module,the communication module and the power module,a hardware platform for the receiver is set up.On the basis of the hardware platform,the software function of ARM and FPGA is designed.Testing results show that B2-frequency signal can be accurately acquired and tracked by the designed receiver,longitude standard deviation is 1.5 m,latitude standard deviation is 5.1 m,height standard deviation is 4.4 m,the positioning accuracy reaches the expected effect.

BD2 recevier;MAX2112;ARM;FPGA

TN967.1

A

1673-808X(2015)05-0356-05

2015-04-06

国家自然科学基金(61162007,61271284,61362005);广西自然科学基金(2013GXNSFA019004,2014GXNSFAA118352, 2014GXNSFBA118280);广西无线宽带通信与信号处理重点实验室主任基金(GXKL0614102)

纪元法(1975-),男,山东莘县人,教授,博士,研究方向为信号处理、卫星导航。E-mail:jiyuanfa@163.com

王超,纪元法,孙希延.基于ARM+FPGA的BD2接收机设计与实现[J].桂林电子科技大学学报,2015,35(5):356-360.