Mark5B格式器及10 G网络传输系统在VLBI中的应用

2014-05-12张秀忠朱人杰吴亚军郭绍光

于 威,张秀忠,朱人杰,3,陈 岚,吴亚军,3,郭绍光

(1.中国科学院上海天文台,上海 200030;2.上海应用技术学院,上海 200235;3.中国科学院射电天文重点实验室,江苏 南京 210008)

Mark5B格式器及10 G网络传输系统在VLBI中的应用

于 威1,张秀忠1,朱人杰1,3,陈 岚2,吴亚军1,3,郭绍光1

(1.中国科学院上海天文台,上海 200030;2.上海应用技术学院,上海 200235;3.中国科学院射电天文重点实验室,江苏 南京 210008)

由于遥远的天体发出的无线电信号极其微弱,信噪比极低,VLBI系统要想得到较高的测量精度,必须尽量加大测量带宽和提高采样位数,但是这样会导致VLBI终端(比如数字基带转换器)产生的观测数据激增。传统的VLBI终端数据传输系统采用VSI接口,数据最高传输速率限制在2 Gbps,且数据记录设备必须采用定制的Mark5B设备,极其不灵活,因此已经不能适应现在VLBI系统的观测需求。为了提高数据传输速率,增加数据记录设备的灵活性,上海天文台新研制的基于多相滤波器组和快速傅里叶变换方式的数字基带转换器的数据传输系统采用了高速灵活的10 G网络接口。10 G网络系统中数据传输采用报文交换方式,因此数据到达接收端的时间不是精确可靠的,这要求数据在进入10 G网络接口之前必须已经具有标准的VLBI数据格式,所以在10 G网络前端设计了Mark5B格式器。详细介绍了基于现场可编程门阵列的Mark5B格式器及10 G网络传输系统的设计原理,并在文章的最后通过三组实验验证了其功能的正确性和性能的稳定性。

多相滤波器组;数字基带转换器;10 G网络;Mark5B格式器

CN53-1189/P ISSN1672-7673

数字基带转换器(Digital Base-Band Converter,DBBC)是甚长基线干涉测量技术(Very Long Baseline Interferometry,VLBI)接收系统中最重要的数字设备之一,承担着频段选择、数据采集等任务[1],其把接收机接收的宽带中频信号数字化后分成多个通道并转换为基带信号,以供相关处理机进行后续处理。国际上应用于VLBI系统的数字基带转换器主要有两种实现方式,第一种为混频方式,既数字化后的中频信号与不同频率的本振信号相乘,然后通过特定带宽的低通滤波器滤出所需的基带信号,最后再通过抽取器降低数据速率。第二种采用多相滤波器组的方式,既数字化后的中频信号先做并行快速傅里叶变换(Fast Fourier Transform,FFT),然后经过一个多相滤波器组,并行输出多个通道的基带信号。第一种方式的优点是通道带宽可选,应用起来比较灵活,缺点是各个通道之间时延一致性较差,这会限制VLBI系统最终的时延精度。第二种方式的优点是各个通道之间时延一致性较好,缺点是各个通道带宽大小固定,不够灵活。

上海天文台VLBI技术实验室2007年研制成功基于混频方式的数字基带转换器,并命名为CDAS (Chinese VLBI Data Acquisition System),CDAS接口方式为通过VSI(VLBI Standard Interface)接口连接到Mark5B记录设备[2],目前CDAS已经为嫦娥一号、嫦娥二号的VLBI轨道定位做出了巨大贡献。为了进一步降低各个通道之间的时延,上海天文台VLBI技术实验室新研制了基于多相滤波器组的数字基带转换器(以下称其为Polyphase DBBC)。

VSI接口必须使用Mark5B设备作为数据记录终端,且数据记录速率最高为2 Gbps,这大大限制了数字基带转换器的输出速率和接收设备的灵活性,现在国际上新开发的数字基带转换器,如美国的DBE(Digital Backend)[3]和欧洲的EVN DBBC[4]都不再采用VSI接口,而是采用10 G网络输出,数据记录端采用具有10 G网络接口的Mark5C或Mark6设备,这样数字基带转换器的数据发送速率可以升级到4 Gbps、8 Gbps等更高的速率。DBE主要与Mark5C相配合,使用的是CX4接口的10 G网络,这种接口使用较粗的铜缆作为传输介质,传输距离不如光纤远,使用起来也不如光纤方便,而且具有CX4接口的通用服务器较少,所以如果要使用通用服务器作为DBE的数据记录设备,必须要加同时具有CX4接口和SFP+光纤接口的交换机进行转换。EVN DBBC的10 G网络既支持CX4接口也支持SFP+光纤接口,不过其10 G接口是在一块名叫FILA10G的单独PCB板上。由于前端接口不同FILA10G板不能与Polyphase DBBC相连,所以必须开发自己的10 G网络系统。传统的VSI总线包括32位数据线和1位时钟线,这样数据和时钟可以同步传输到Mark5B设备,然后由Mark5B设备内部的格式器为数据添加上时间码、同步字、校验位等帧头信息并打包成Mark5B数据格式。由于网络传输是基于报文交换的方式,因此报文从数字基带转换器到数据接收设备所经历的时间就变的非常不确定,这样在数据接收设备中为报文添加时间信息显然是不准确的,为了解决这个问题,使用10 G网络接口的数字基带转换器本身要具有格式器功能,其数据格式可以是Mark5B格式也可以是VLBI新的帧格式:VDIF(VLBI Data Interchange Format)格式。由于现在上海天文台开发的相关处理机还只能处理Mark5B帧格式,所以为Polyphase DBBC设计的数据格式为Mark5B格式。成品的Polyphase DBBC设备共有16个通道,每个通道的带宽为32 MHz,数据输出接口在保留VSI总线的基础上主要采用SFP+光纤接口的10 G网络。

1 总体设计

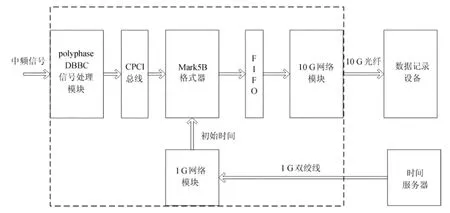

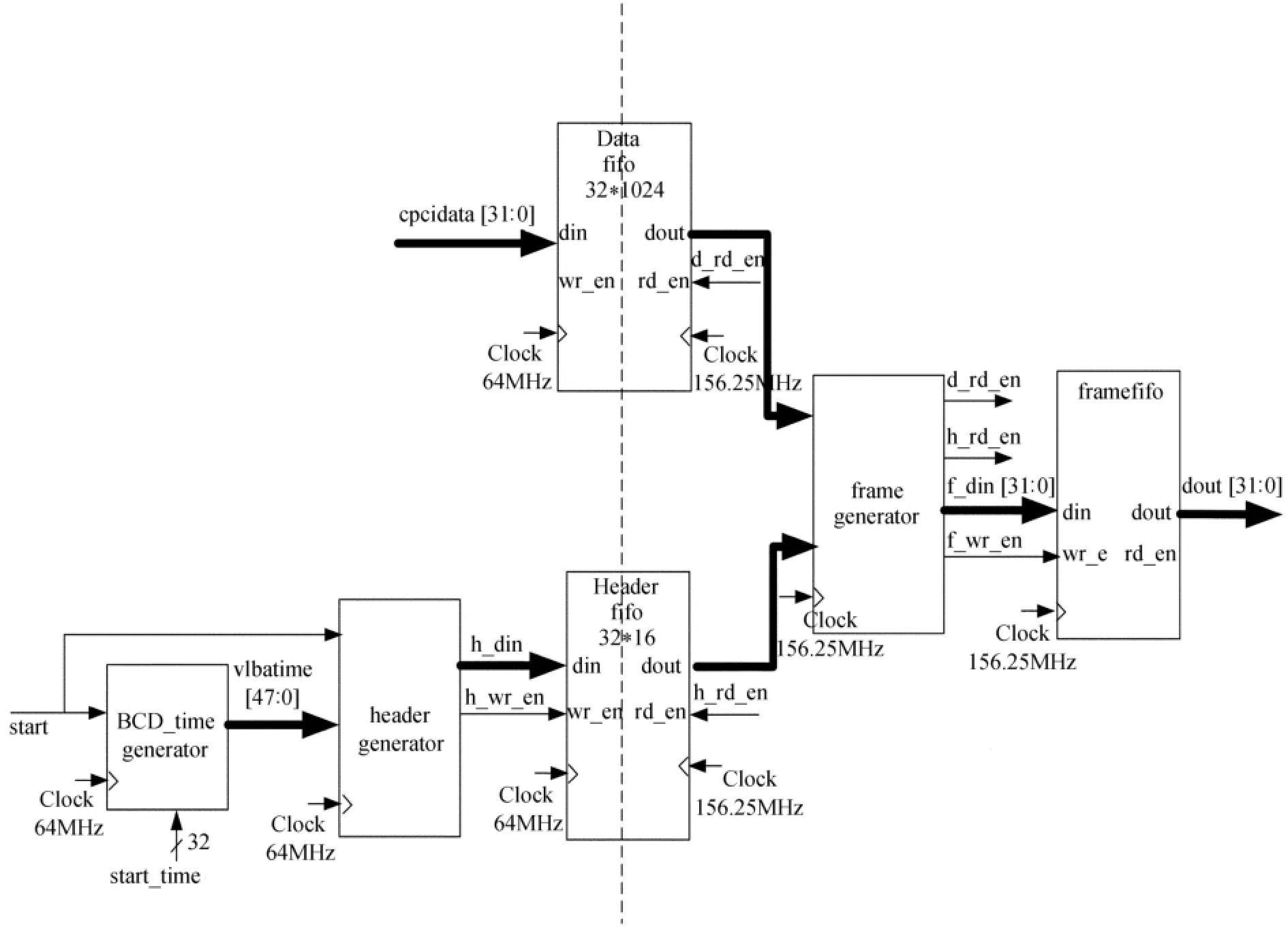

Polyphase DBBC数据流程框图如图1。其数据处理模块通过一系列复杂的数字信号处理算法把输入的512 MHz带宽的中频信号转变为基带信号,然后输出时钟频率为64 MHz的32 bits数据,32 bits包含16个通道,每个通道位宽为2 bits,带宽为32 MHz。Mark5B格式器把Polyphase DBBC数据处理模块输出的数据打包成标准的Mark5B帧格式,然后通过10 G网络模块发送出去。数据记录设备为一台高性能具有磁盘阵列的服务器,它通过10 G光纤网络把数据记录下来存成文件。Mark5B格式器在为数据打格式的时候需要初始时间来与别的DBBC设备进行时间同步,因此设计了1 G网络模块把外部时间服务器的初始时间传送到Mark5B格式器中。本设计中Polyphase DBBC数据处理模块在前面板中实现,前面板的照片如图2,图1虚线框中其余模块在后面板中实现,并且除了10 G网络模块和1 G网络模块中的物理层芯片外全部集成在一片现场可编程门阵列中,现场可编程门阵列的型号为XILINX公司的Virtex6 XC6VLX75T,后面板的照片如图3。前面板通过CPCI总线把数据传输到后面板。

图1 Polyphase DBBC数据流程框图Fig.1 A flowchart of the Polyphase DBBC

2 Mark5B格式器的设计

2.1 Mark5B帧格式

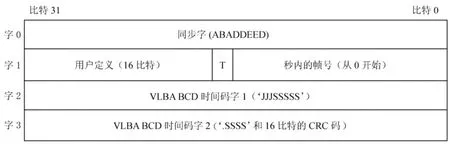

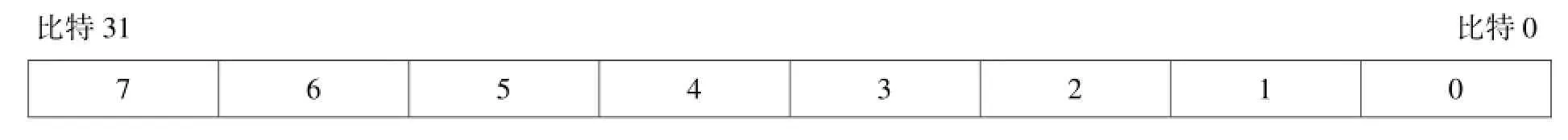

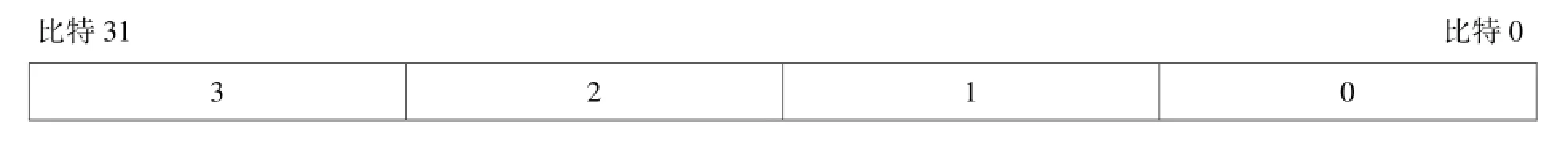

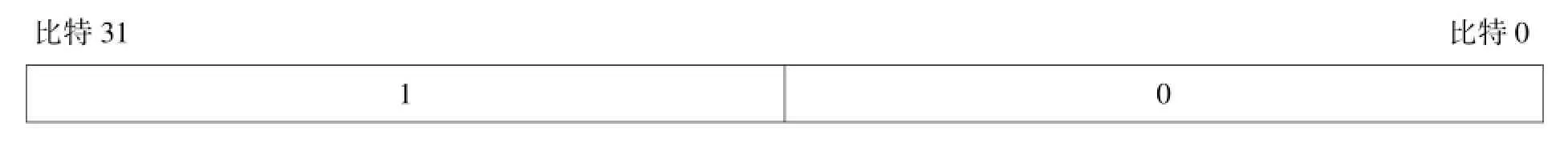

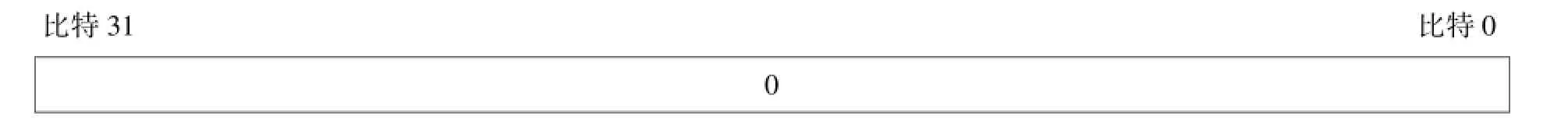

Mark5B帧格式包括4个32位的帧头和紧接着2500个32位的数据队列。帧头格式如图4,包括以下信息:

字0为同步字“ABADDEED”。

字1中比特31~16为用户自定义内容(比如,台站ID号);比特15是测试向量标志;比特14~0是每一秒内的帧序号(当整数秒时刻到来时,帧序号从零开始)。

字2~3为BCD格式的时间码和16比特循环冗余校验码[5]。

图4 Mark5B帧头Fig.4 The header of the Mark5B frame format

表1至表6分别为当系统记录的有效采样位数为1、2、4、8、16和32时每一个32位数据队列的格式,方格代表一次采样得到的数据位数,数字表示采样顺序。可以看到各次采样值按从低位到高位的顺序排列。帧头中记录的时间是此帧第1个数据字中第1个采样值被采样的时刻。

表1 1比特流的数据字格式Table 1 The data string format in a 1-bit stream

表2 2比特流的数据字格式Table 2 The data string format in a 2-bit stream

表3 4比特流的数据字格式Table 3 The data string format in a 4-bit stream

表4 8比特流的数据字格式Table 4 The data string format in an 8-bit stream

表5 16比特流的数据字格式Table 5 The data string format in a 16-bit stream

表6 32比特流的数据字格式Table 6 The data string format in a 32-bit stream

2.2 Mark5B格式器的设计

Mark5B格式器的数据流程框图如图5。由于Mark5B帧格式的帧头是非替代的,既在连续的数据流中每隔一定的时间间隔插入一个帧头,所以Mark5B格式器模块的输出时钟一定要比输入时钟频率高。本设计中Mark5B格式器后面连接着系统时钟为156.25 MHz的10 G网络模块,因此为了方便时钟同步,把Mark5B格式器的输出时钟也定为156.25 MHz。从图5可以看出此模块虚线左边时钟为64 MHz,虚线右边时钟为156.25 MHz时钟,其中64 MHz时钟为Polyphase DBBC信号处理模块输出的时钟。图中cpcidata[31∶0]为Polyphase DBBC信号处理模块输出的32位数据,由于10 G网络的数据传输速率较高,本设计没有添加“比特流屏蔽字”功能(“比特流屏蔽字”主要是为了降低数据输出速率)。

图5 Mark5B格式器流程框图Fig.5 The flowchart of the Mark5B formatter

cpcidata[31∶0]数据首先进入数据缓存器(图5 Data fifo)中缓存起来,然后被帧成型模块(图5 frame generator)在适当的时候输出到帧缓存器(图5 framefifo)中。时间产生模块(图5 BCD_timegenerator)根据初始时间信号(图5 start_time)、秒信号(图5 ppsin)以及64 MHz时钟,通过分频的方式生成BCD码格式的时间(图5 vlbatime[47∶0])供帧头生成模块(图5 header generator)使用。帧头生成模块以起始信号(图5 start)的高电平为起始时刻,每隔2 500个64 MHz时钟生成一个帧头,并存入帧头缓存器(图5 Header fifo)中,每个帧头为4个32位的字,包括同步字、秒内帧序号、VLBA时间和CRC校验码等。帧成型模块产生完整的Mark5B数据帧,其内部包括一个多路选择器,每当帧头缓存器中有数据时,多路选择器就把其中的4个数据读出,写入帧缓存器中,然后切换到数据缓存器,从中读取2 500个数据并存入帧缓存器中,此后多路选择器再次切换回帧头缓存器等待读取4个字的帧头,如此循环进行下去[6]。帧缓存器模块中存入的数据是完整的Mark5B帧格式的数据,接下来只需要把其中的数据按顺序输出到10 G网络模块即可。

3 10 G网络传输系统的设计

本文设计的10 G网络传输系统分为两大部分:数据发送端和数据接收端,数据发送端即为图1中10 G网络模块,这部分除物理层芯片外,全部用现场可编程门阵列硬件实现。数据接收端是运行在图1中数据记录设备上的软件程序。

3.1 数据发送端的设计

图6为10 G网络数据发送模块的结构框图。该模块主要功能是把Mark5B数据帧(以下称其为原始数据)打包成UDP网络数据包发送出去。每个UDP网络数据包包含1 416个字节的原始数据,而每个Mark5B数据帧为10 016个字节(即上文提到的4个32位的帧头和紧接着的2 500个32位的数据队列,总共10 016个字节),因此UDP网络数据包和Mark5B数据帧没有对应关系。协议封装模块把原始数据按照UDP协议、IP协议、以太网MAC层协议等一层层加上头部和尾部,然后发送到XAUI模块,XAUI是一个接口扩展器,可用于把以太网MAC层与物理层相连[7],它扩展的接口是XGMII(与介质无关的万兆接口)。图中xgmii_txd、xgmii_txc、xgmii_rxd、xgmii_rxc四路信号即为XGMII接口。其中xgmii_txd为64位的数据发送信号,xgmii_txc为8位的控制信息发送信号,xgmii_rxd为64位的数据接收信号,xgmii_rxc为8位的控制信息接收信号。由于本设计中只用此模块发送数据,因此xgmii_rxd和xgmii_rxc暂时没有用到。

图中GTX0、GTX1、GTX2、GTX3为相同的高速串行总线,10 G网络发送模块通过使用XAUI和GTX来减少与外部物理层芯片连接的信号线数量,因为物理层芯片与10 G网络实现上层协议的芯片通常是分离的元器件,如果两者之间连接的信号线太多使用起来会非常不方便。从图6可以看出,如果协议封装模块和物理层芯片直接连接总共需要144根信号线,而通过XAUI和GTX扩展后只有16根信号线。

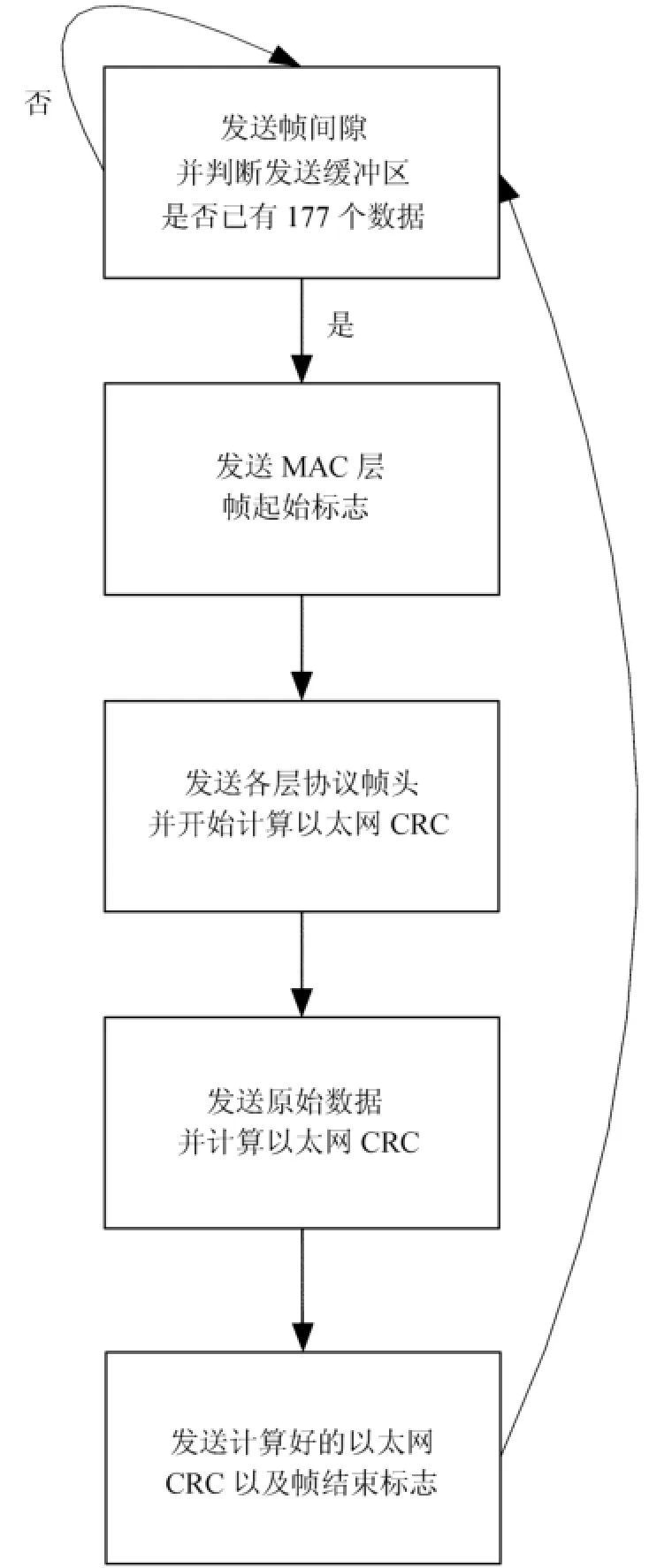

图7为协议封装模块发送数据流程图。本设计中各层网络协议的头部全都固定不变(如MAC层源地址和目的地址,IP层源地址和目的地址,UDP协议源端口号和目的端口号,这样做的好处是不用每次都为其计算IP校验,节约逻辑资源。但是这种方式下有两个问题需要解决:

(1)不同的数据接收设备MAC地址不同,那么在Polyphase DBBC发出的网络包目的MAC地址已经固定的情况下,如何更换不同的接收设备?

(2)UDP校验和校验的内容包括UDP头部和UDP数据,不同的UDP数据包数据部分是变化的,那么UDP的校验和该如何固定不变?

在本设计中的解决方法是:

(1)把发送模块的目的MAC地址设置为全1的广播地址,这样任何与Polyphase DBBC相连的接收设备都可以接收其发出的网络包。

(2)UDP校验和字段其实是可选的,如果把其配置成全0,则接收设备运行标准的UDP接收程序时默认不计算接收的UDP校验和,所以本设计把这个字段设置为全0。

协议封装模块主要由一个发送状态机实现,其发送数据流程如图7。状态机有IDLE、START_SEND、HEADER_SEND、DATA_SEND、FINISH 5个状态。发送状态机首先进入IDLE工作状态,此状态下不断发送帧间隙。IDLE工作状态一旦判断到发送缓冲区中已有177个数据,就把发送状态机切换到START_SEND状态,在这个状态下xgmii_txd发送以太网帧起始标志,xgmii_txc发送的控制信息为0x01。此后发送状态机切换到HEADER_SEND状态,在此状态下,xgmii_txd发送网络数据包包头中的前40个字节,xgmii_txc发送的控制信息为0x00,同时64位的CRC计算模块启动计算。发送完40个字节的包头后,状态机切换到DATA_SEND状态,在此状态下,xgmii_txd首先发送2字节的包头与前6个字节的原始数据拼成的64位数据,接下来每次发送8字节的原始数据,xgmii_txc发送的控制信息一直为0x0。DATA_SEND状态下循环发送了177次以后状态机切换到FINISH状态,在此状态下xgmii_txd以太网帧结束标志以及FCS字段。xgmii_txc发送0xC0,意思是xgmii_txd中的后面6个字节是有效的,之后状态机切换回IDLE状态。

图7 协议封装模块发送数据流程图Fig.7 The flowchart of the protocol encapsulation module

3.2 数据记录设备接收程序的设计

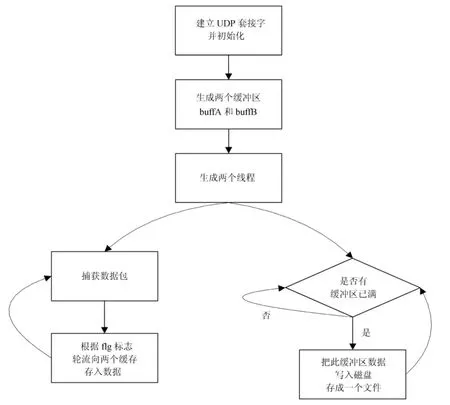

图8为接收端接收数据的流程图。接收端是基于Linux操作系统由C语言编写的应用程序。工作流程如下:

(1)建立UDP套接字并初始化。

(2)建立两个缓冲区buffA和buffB,这两个缓冲区此后用乒乓操作的方式交替缓存数据包,缓冲区的大小都为1 416×20 080字节(DBBC发送的数据包每包的有效原始数据为1 416字节,实际上一个缓冲区存放20 000个数据包,缓冲区开的稍大是为了防止出现意外而溢出)。

(3)生成两个线程(th1和th2),th1用来接收UDP数据包,th2用来把缓冲区的数据写入磁盘存成文件,两线程并行工作。

线程th1工作流程如下:

(1)用建立的UDP套接字接收UDP数据包。

(2)接收一个UDP数据包后根据flg标志判断把数据填入哪个缓冲区。判断方式为:当flg为0时,往缓冲区buffA中填入数据;当flg为1时,往缓冲区buffB中填入数据,flg初始值为0。当每个缓冲区中填入的数据达到20 000个UDP数据包时,把这个缓冲区的满标志置为1(buffA的满标志为fullA,buffB的满标志为fullB)。

线程th2工作流程如下:

(1)根据buffA和buffB的满标志判断是否有缓冲区已满,如果有则进入步骤(2),否则一直循环判断。

(2)把已满的缓冲区中的数据写入磁盘,存成一个单独的文件,并把满标志置为0,返回步骤(1)。

图8 接收端接收数据的流程图Fig.8 The flowchart of the data-receiving program

4 结果测试及分析

本文共做了3组实验进行结果测试,每组实验都做了48 h的长时间测试。实验中用一台噪声仪产生宽带射频白噪声信号,然后通过模拟下变频器产生512 MHz带宽的中频信号,中频信号通过功率分配器后一分为二分别输入两台Polyphase DBBC的中频信号输入端。第1组实验用一台高性能10 G服务器和一台Mark5B设备同时记录同一台Polyphase DBBC产生的数据,Polyphase DBBC中的格式器和Mark5B设备中的格式器在记录前用时间服务器进行时间同步。第2组实验用一台高性能10 G服务器和一台Mark5B设备分别记录两台Polyphase DBBC产生的数据,Polyphase DBBC中的格式器和Mark5B设备中的格式器在记录前用时间服务器进行时间同步。第3组实验用两台高性能10 G服务器分别记录两台Polyphase DBBC产生的数据,两台Polyphase DBBC中的格式器在记录前用时间服务器进行时间同步。最后用MATLAB程序分别解算每组实验中两路数据的自相关结果和相应通道间的互相关结果,解算自相关的MATLAB程序快速傅里叶变换长度为4 096点,积分时间为1 024个快速傅里叶变换周期,解算互相关的MATLAB程序快速傅里叶变换长度为16 384点,积分时间为1 024个快速傅里叶变换周期。

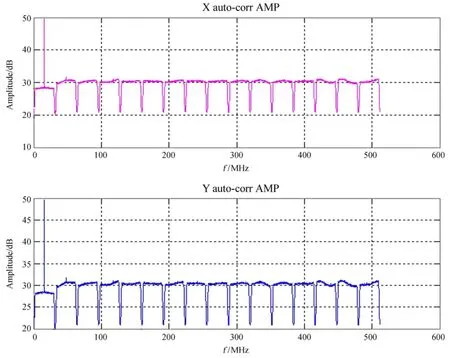

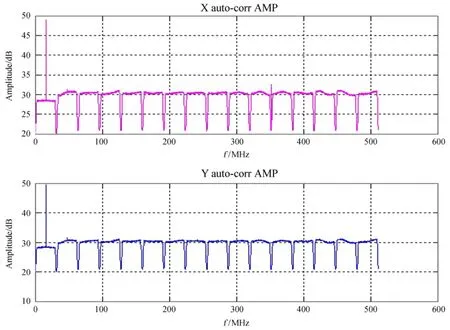

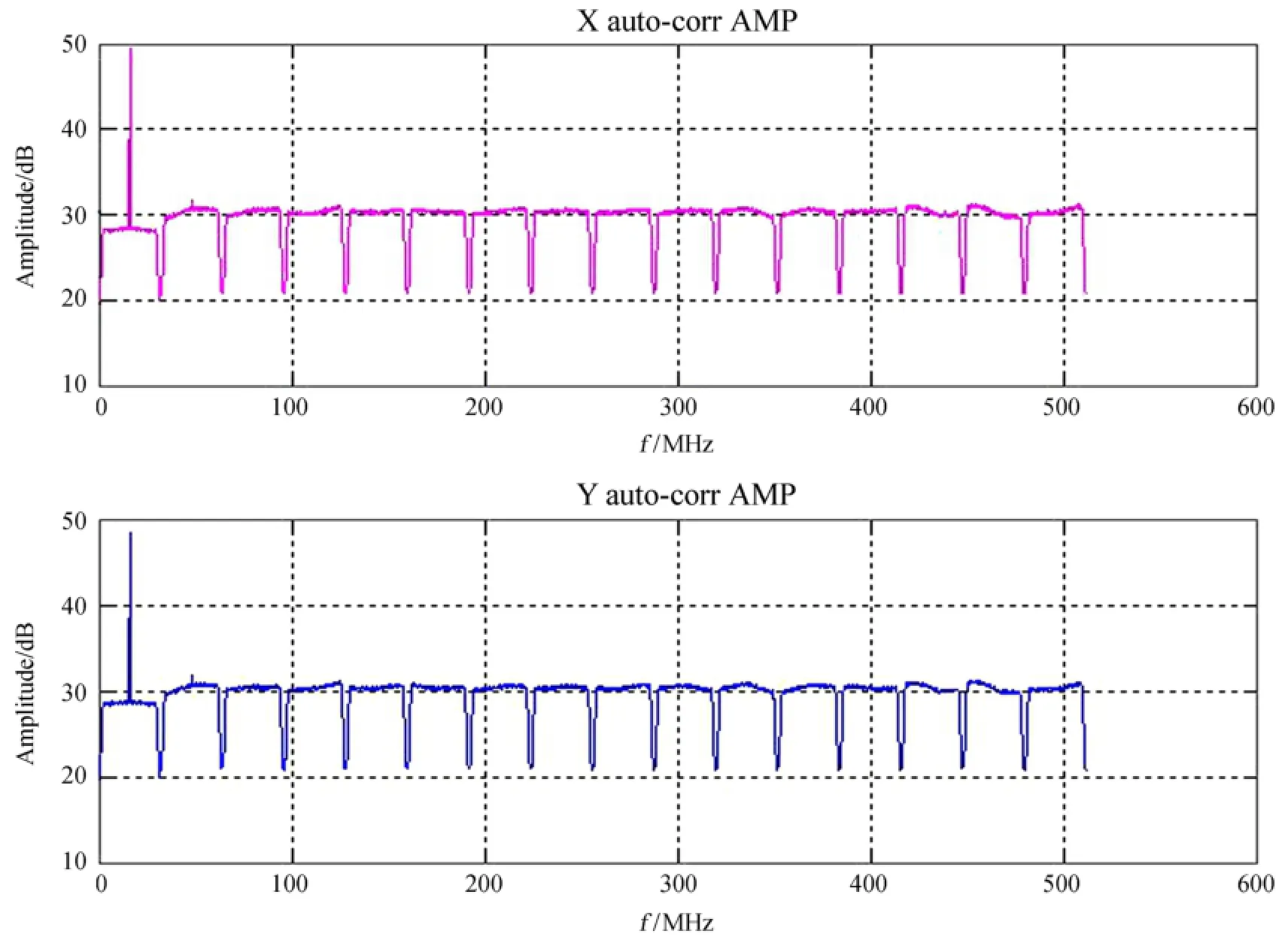

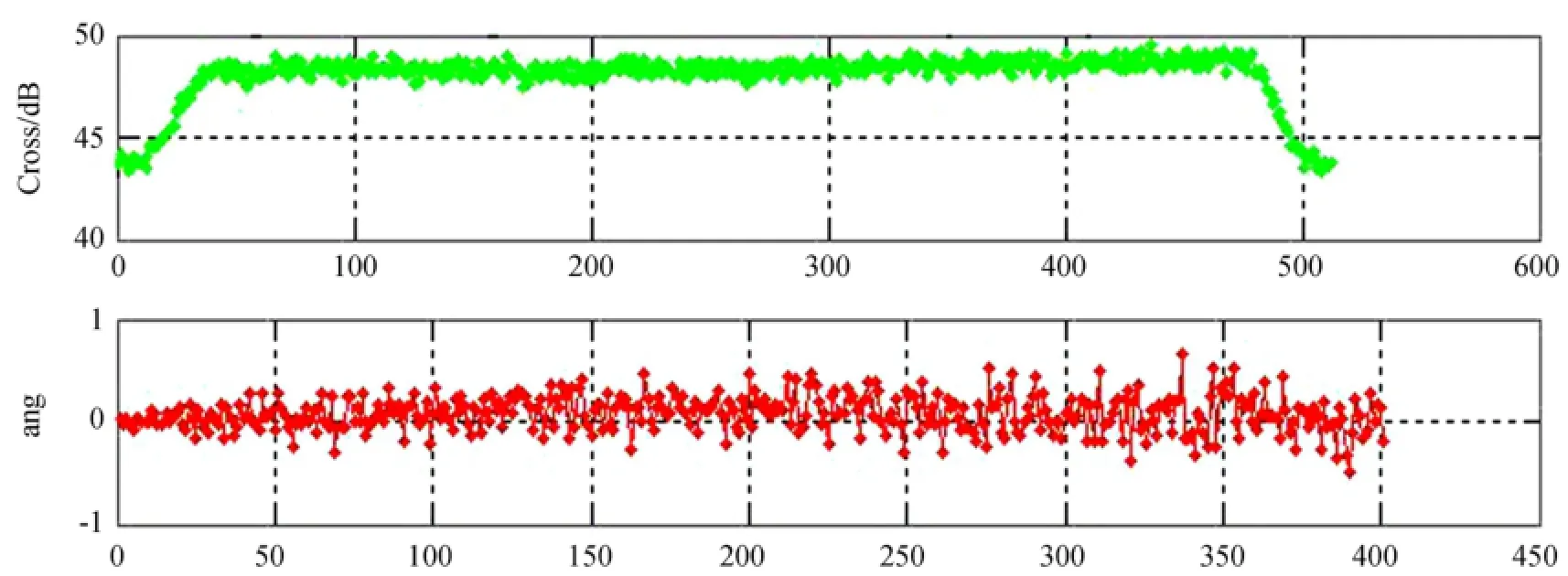

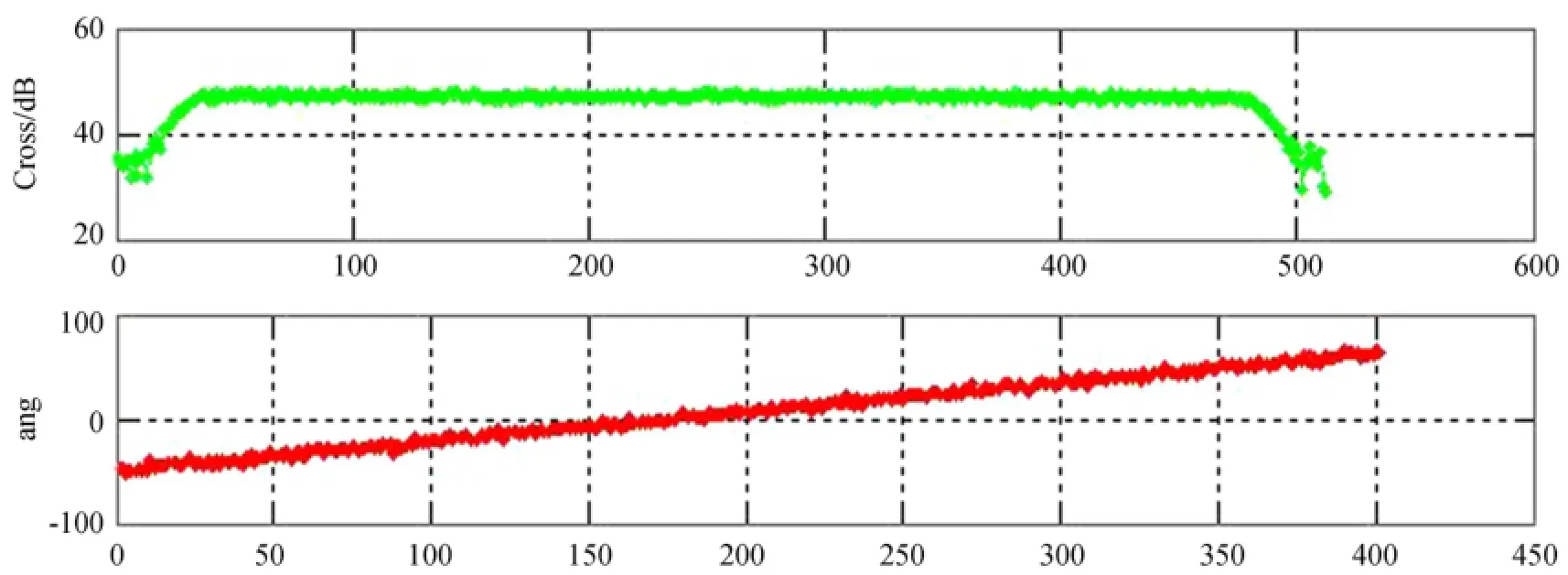

图9、10、11分别为3组实验两路数据各自16个通道的自相关幅度谱,由图可知除第一个通道外其余通道幅度较为平坦,且两路数据对应通道幅度一致性较好。图12、13、14分别为3组实验两路数据第8个通道的互相关幅度和相位谱(上图为幅度谱,下图为相位谱)。通过48 h长时间测试,发现每组实验的互相关时延都稳定不变,图中第1组实验几何时延为39.265 6 us,残余时延约为0 ns (这与两路数据来自同一台Polyphase DBBC相吻合)。第2组几何时延为39.265 6 us,残余时延约为9.6 ns,第3组几何时延为0.062 5 us,残余时延约为-12.1 ns(后两组实验残余时延不为0与两路数据来自于不同的Polyphase DBBC相吻合)。

图9 第1组实验自相关幅度谱Fig.9 The spectra of self-correlation amplitudes in the first set of experiments

图10 第2组实验自相关幅度谱Fig.10 The spectra of self-correlation amplitudes in the second set of experiments

图11 第3组实验自相关幅度谱Fig.11 The spectra of self-correlation amplitudes in the third set of experiments

图12 第1组实验互相关幅度和相位谱Fig.12 The spectra of cross-correlation amplitudes and correlation phases in the first set of experiments

图13 第2组实验互相关幅度和相位谱Fig.13 The spectra of cross-correlation amplitudes and correlation phases in the second set of experiments

图14 第3组实验互相关幅度和相位谱Fig.14 The spectra of cross-correlation amplitudes and correlation phases in the third set of experiments

通过以上实验可知,本文设计的Mark5B格式器以及10 G网络传输系统工作正常,性能稳定,已经完全可以取代原有的DBBC通过VSI总线与Mark5B相连的老系统。本系统数据接收端只需要通用的具有10 G网口的服务器即可,也可以是Mark5C或者Mark5B,应用非常灵活,且由于使用了10 G网络,数据传送速率有很大的提升空间。后续所要做的工作主要有:(1)开发VDIF格式器,通过外部参数控制DBBC数据格式在VDIF与Mark5B之间切换;(2)优化接收端接收程序,提高接收速率。

参考文献:

[1] 项英.VLBI数据采集终端中数字基带转换器的研究和设计[D].上海:中国科学院研究生院(上海天文台),2005:28-29.

[2] 朱人杰,张秀忠,韦文仁,等.我国新一代VLBI数字基带转换器研制进展[J].天文学进展,2011,29(2):207-217.

Zhu Renjie,Zhang Xiuzhong,Wei Wenren,et al.The progress of modern Chinese Data Acquisition System[J].Progress in Astronomy,2011,29(2):207-217.

[3] Navarro R,Wang D,Soriano M,et al.Digital backend for JPL deep space communications complex VLBI processor[Z].American:California Institute of Technology,2010.

[4] Tuccari G,Alef W,Bertarini A,et al.DBBC Development Status[C]//Progress in Technology Development and the Next Generation VLBI System:The 5th IVS General Meeting Proceedings. 2008:376-380.

[5] Whitney A R,Cappallo R J.Mark 5B design specifications[EB/OL].(2004-11-24).www. haystack.mit.edu/tech/vlbi/mark5/mark5_memos/019.

[6] Aldrich W.Data input module Mark 5B I/O board theory of operation[EB/OL].(2006-02-03).www.haystack.mit.edu/tech/vlbi/mark5/mark5_memos/032.

[7] LogiCORE IP XAUI v9.2 User Guide[M/OL].(2006-04-19).www.xilinx.com/support/ documentation/ip_documentation/xaui_ug150.pdf.

A Mark5B Formatter and a 10G Network Transmission System Applied to VLBI

Yu Wei1,Zhang Xiuzhong1,Zhu Renjie1,3,Chen Lan2,Wu Yajun1,3,Guo Shaoguang1

(1.Shanghai Astronomical Observatory,Chinese Academy of Sciences,Shanghai 200030,China,Email:yuwei001@mail.ustc.edu.cn;2.Shanghai Institute of Technology,Shanghai 200235,China;3.Key Laboratory of Radio Astronomy,Chinese Academy of Sciences,Nanjing 210008,China)

Radio signals from distant radio sources are extremely weak and have very low signal-to-noise ratios when observed with current radio telescopes.In order for VLBI data to reach high measurement accuracies,large measurement bandwidths and sampling bits need to be adopted,resulting in huge amounts of observation data produced by the VLBI terminals(such as Digital Base-Band Converters).Traditional data transmission systems of VLBI terminals use VSI interfaces,which cannot meet the requirements of broadband VLBI observation.The limitation of VSI interfaces is due to two factors:First,their data transmission speeds do not exceed 2Gbps,and second,their data-recording equipments are conformed to the rather rigid Mark5B format.We have designed a 10G network system for a new Digital Base-Band Converter(which is developed by the Shanghai Astronomical Observatory based on polyphase-filter banks and the FFT)to enhance its flexibility and transmission speed.The data-transmission method of this system is the packet switching,so a data arrival time at the data receiver is not accurate and reliable.This requires that data must be of a standard VLBI format before being processed by the 10G system.To achieve this we have also designed a Mark5B data formatter to convert data before being sent to the 10G system.This paper describes the principles of the Mark5B formatter and the 10G network system,which are both based on FPGA.The final part of the paper describes three sets of experiments verifying the accurateness and stableness of our designs.

Polyphase-filter banks;Digital Base-Band Converter;10G network interface;Mark5B formatter

TN713

A

1672-7673(2014)03-0287-12

2013-10-29;

2013-11-16

于 威,男,助理工程师.研究方向:深空探测,射电天文,FPGA数字电路.Email:yuwei001@mail.ustc.edu.cn