基于FPGA的基带信号发生器的设计

2011-11-06张祥丽张慧敏李方健

张祥丽,张慧敏,李方健

(重庆电子工程职业学院 通信系,重庆 401331)

基于FPGA的基带信号发生器的设计

张祥丽,张慧敏,李方健

(重庆电子工程职业学院 通信系,重庆 401331)

采用基于DDS模块的硬件实现方法设计基带信号发生器,在FPGA内部用DDS模块进行频率合成和叠加,利用EDA技术和FPGA实现直接数字频率综合器DDS的设计。可以完成快速的频率切换,并且在改变时能够保持相位的连续,很容易实现频率、相位和幅度的数控调制。实验结果表明该信号发生器达到了一个比较好的设计精度。

FPGA;信号发生器;DDS

1 引言

基带信号发生器的实现方案主要有采用纯硬件的FFT(快速傅立叶变换)算法实现、基于时域的软件运算和基于DDS(数字频率合成)模块的硬件实现三种方案。纯硬件的FFT算法实现方案是使用基带信号发生器内部硬件进行FFT算法的运算,优点是频谱输出速度快,可以实现跳式方式输出频谱信号,缺点是硬件运算采用FFT算法,需要使用大量的DSP和RAM资源,功耗大,若控制芯片不加散热器,系统不能长时间正常工作。硬件FFT模块无法随机相位,整个频谱在时域上分布不均匀,对后级放大器的动态范围要求高。基于时域的软件运算方案是使用计算机在时域上进行频率信号的运算和叠加,将生成的波形文件加载至基带信号发生器内部的存储器上,此方案的优点是使用计算机进行运算,节省系统硬件资源,并且运算数据精确,缺点是计算机在时域上进行频率信号的运算和叠加的计算时间长。基于DDS模块的硬件实现方案是在FPGA内部用DDS模块进行频率合成和叠加,优点是输出频谱的频率点可以很精确的进行调整,频率稳定性好,适合用分段跳时的方式来进行宽带干扰,缺点是合成频谱的频点数量受FPGA容量的限制。

综合以上三种方案的优缺点,并结合设计要求,我们选择与第三种方案相近的,但DDS模块用EDA技术和FPGA通过软件实现,即利用EDA技术和FPGA实现直接数字频率综合器DDS的设计。直接数字频率综合技术,即DDS技术,是一种新型的频率合成技术和信号产生方法。其电路系统具有较高的频率分辨率,可以实现快速的频率切换,并且在改变时能够保持相位的连续,很容易实现频率、相位和幅度的数控调制。

2 硬件电路设计

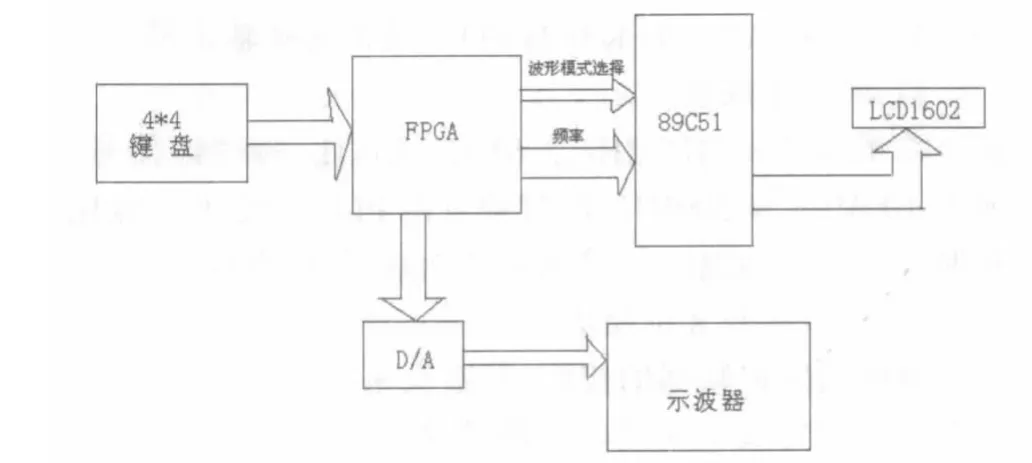

本系统以51单片机及FPGA为控制核心,硬件电路主要由 FPGA 核心板、4×4 键盘、89C51 芯片、LCD1602,D/A转换芯片和一些电容电阻组成。通信基带信号发生器的原理如图1所示。

图1 硬件电路框图

系统的工作原理是FPGA接收矩阵按键的控制信息,经内部数据处理,生成指定频率的特定数字波形,再经D/A芯片转换成模拟信号,输出到示波器进行显示。同时,FPGA将键盘输入的控制信号输出给单片机,分别通过3线传输波形信息,8线传输频率信息。

3 软件模块设计

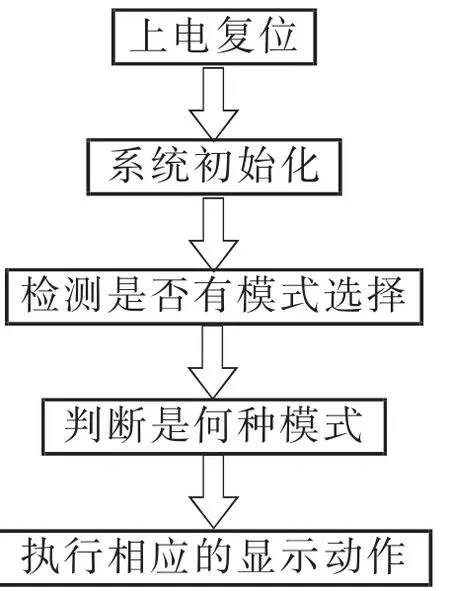

系统设计主要由FPGA控制按键,在FPGA内部进行DDS模块的设计,然后由51单片机来控制LCD显示。软件设计分为三个部分,分别是单片机(MCU)控制LCD程序的设计、FPGA数据采集、数据处理程序和计算机在频域上进行频谱信号运算程序的设计。单片机控制系统程序流程如图2所示。

图2 软件流程图

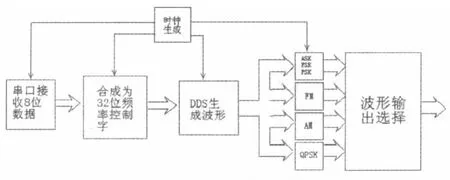

该程序采用C语言,运用Keil C软件进行编程,使用软件和伟福仿真器进行仿真调试,然后再将程序烧写进51芯片进行脱机调试。程序部分主要包括:延时1ms程序、判断忙否、写地址函数、写指令函数、写数据函数、显示字符的位置函数、LCD初始化函数、指定位置显示函数、全屏填充函数、固定行显示字符串函数、频率显示程序和模式选择函数。FPGA系统设计框图如图3所示。

图3 FPGA系统总体框图

系统共分为六个主模块:时钟生成模块,串口接收模块,合成32位的频率字模块,DDS生成波形模块,ASK、FSK、PSK、FM、AM、QPSK生成模块,波形选择输出模块。

(1)时钟生成模块

该模块生成 100MHz、200MHz、10KHz的时钟信号,其中100MHz和200MHz的时钟可由PLL生成,而10KHz的时钟直接由20Mhz的输入时钟2000分频得到。

(2)串口接收8位模块

该模块完成数据的接收,其数据来自单片机,该模块与单片机只完成单向通信,即单片机向FPGA传送频率控制字,每收到8位数据,即输出一个上升沿通知其他模块8位数据接收完成。

(3)合成为32位频率控制字

由于DDS的频率控制字由32位数据控制,但是单片机串口每次只能发送8位的数据,所以每个控制字分成4次发送,于是在FPGA中将每四次接收的数据合成一起成为32的频率控制字。

(4)DDS 生成波形模块

此模块中共有3个DDS,分别是正弦波、三角波、方波,其中三角波与方波可以直接输出,而正弦波则输入到其他的模块进一步处理。

(5)信号生成模块

(a)ASK、FSK、PSK 生成模块

该模块中包括一个随机信号产生模块和数字键控信号模块,其中随机信号产生模块用于产生一个随机信号,其内部是固化了一串二进制数据,只需顺序输出这些二进制数据即可。

ASK:当输入1时输出正弦波,当输入0时输出0;FSK:当输入1时输出某种频率的正弦波,当输入0时输出另外一种频率的正弦波;PSK:当输入1时输出某种频率的正弦波,当输入1时输入对该种频率正弦波反向的波形信号。

(b)FM生成模块

FM的波形可由某种频率的正弦波去控制DDS频率字输入,使频率字随调制信号改变而生成FM波形。

(c)AM生成模块

AM可由两种正弦波信号相乘,其中一个正弦波为调制信号,另外一个正弦波为载波信号。

(d)QPSK生成模块

该模块由两个主要部分组成,包括串并转换、四相位正弦信号生成模块,串并转换模块将二进制转换成两位的二进制数据,该两位的数据有四种情况:00、01、10、11,其中00选择输出相位0°的正弦波,01选择输出相位90°的正弦波,10选择相位输出180°的正弦波,11选择输出相位270°的正弦波。

(e)波形选择输出模块

0000:方波,0001:三角波,1000:正弦波,1001:ASK,1010:FSK,1011:PSK,1100:AM,1101:FM,1110:QPSK。

4 测试数据及误差分析

采用示波器得到测试数据如表1、表2、表3所示:

表1

表2

表3

液晶显示结果与示波器测试结果相一致,无法通过示波器测试的方式测得误差,认为误差为0,说明该系统的设计精度达到了一个比较好的程度。

5 结语

基带信号发生器的实现方案主要有采用纯硬件的FFT(快速傅立叶变换)算法实现、基于时域的软件运算和基于DDS(数字频率合成)模块的硬件实现这三种方案。本文综合这三种方法的优缺点,采用基于DDS模块的硬件实现方法设计基带信号发生器,在FPGA内部用DDS模块进行频率合成和叠加,利用EDA技术和FPGA实现直接数字频率综合器DDS的设计。该信号发生器可以实现快速的频率切换,并且在改变时能够保持相位的连续,很容易实现频率、相位和幅度的数控调制。实验结果说明了该信号发生器的设计精度达到了一个比较好的程度。

[1]潘松,黄继业.EDA技术实用教程[M].北京:科学出版社,2008.

[2]章彬宏,周正林.EDA应用技术[M].北京理工大学出版社,2009.

[3]贾玉臣,吴嗣亮.正弦信号源直接数字合成的实现[J].北京理工大学学报,2005,(9).

[4]王数明,戴瑜兴.基于DDS技术的可叠加谐波的正弦信号源设计[J].湖南师范大学自然科学学报,2005,(4).

[5]胡晓燕.基于FPGA和MCU的函数波形发生器设计[J].电子测试,2008,(12).

TP39

A

1674-5787(2011)04-0153-02

2011-08-25

张祥丽(1979—),女,四川内江人,重庆电子工程职业学院通信工程系,讲师,研究方向:信号与信息处理。

责任编辑 王荣辉