基于FPGA的多总线可动态重构监测系统

2024-04-30王红亮厉智强王学斌

全 贺,王红亮,厉智强,王 浩,王学斌

1.中北大学,省部共建动态测试技术国家重点实验室;2.北京宇航系统工程研究所

0 引言

目前世界上大约有40种现场总线[1],在工业测试领域系统中多种总线并存[2],不存在适用于所有测试领域的现场总线,各种现场总线都有自身的技术特点和适用范围。传统多总线监测系统将各信道数据融合再传输,不能保证监测数据实时性[3];分时监测系统,各信道轮流传输,由于信道传输协议不同,导致系统程序繁杂,不能保证监测数据可靠性[4]。提高多总线数据监测系统的灵活性、可靠性,对于降低系统复杂度、提升系统的可维修性具有重大的意义。

多总线数据监测系统不仅广泛应用于工业测试领域,而且在航空航天领域也具有举足轻重的作用。本文主要研究在复杂的环境中,实现多总线动态重构,保证各信道数据实时性,降低系统程序复杂度,并结合双冗余传输方式提升数据监测系统的可靠性、安全性。

1 整体方案设计

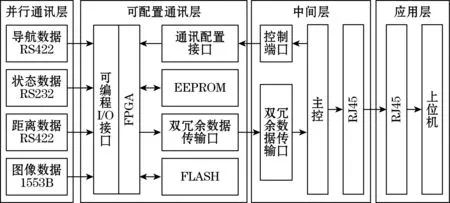

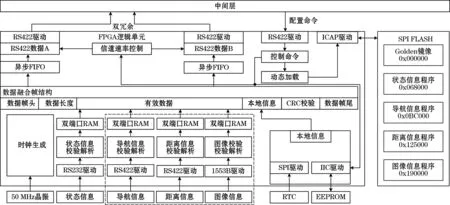

本文对信息识别、信息提取、数据融合、多总线动态重构、双冗余传输等技术提出了设计方案,介绍了系统各部分组成与关键技术,并对多总线动态重构监测系统的性能进行测试。主要由并行通讯层与可配置通讯层构成多总线动态重构监测系统。并行数据通讯层用于获取导航数据、状态数据、距离数据、目标数据;可配置通讯层用于FPGA动态重构、数据融合、动态传输融合数据、信道速率动态配置。与中间层通过双冗余RS422总线接口实现融合数据向上级系统传输,通过通讯配置接口实现程序动态重构与信道速率动态配置。

通过并行通讯层实现外部数据接收功能,可配置通讯层,根据当前加载程序功能通过可编程I/O接口对并行通讯层数据进行选择接收,FPGA将来自并行通讯层的数据与本系统数据进行数据融合,再将融合后的数据通过双冗余数据传输接口,按照与上级系统约定的信道速率进行数据传输。系统整体方案如图1所示。

图1 系统整体方案

2 硬件方案设计

本文主要研究信息识别与提取、动态重构、双冗余传输技术,重点介绍1553B总线接口、RS422总线接口、配置电路、电源电路设计。

2.1 1553B总线接口设计

1553B总线是一种时分、指令响应型串行数据总线,由于其高可靠性和实时性,在航空航天领域得到广泛应用[5]。本系统选用BU-61580接口芯片,BU-61580数据稳定、技术成熟、应用广泛,它实现了所有的MIL-STD-1553B消息格式和双冗余模式代码。BU-61580电路如图2所示。

图2 BU-61580电路

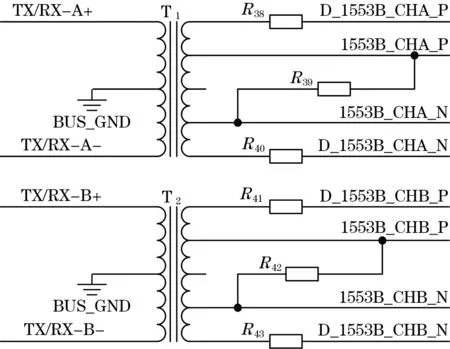

1553B物理连接有直接耦合和变压器耦合,1553B总线通常工作在强电磁干扰、振动冲击大的恶劣环境中,这就需要总线能够进行故障隔离,提高数据传输的稳定性,因此采用变压器耦合方式[6]。变压器耦合电路如图3所示。

图3 变压器耦合电路

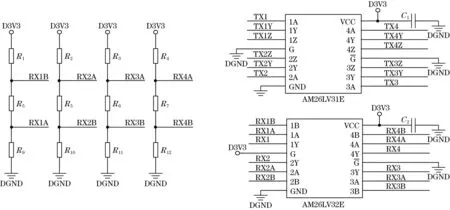

BU-61580与FPGA通信和控制通过地址总线、数据总线、控制总线及状态总线4种总线实现[7]。BU-61580接口电平5 V,FPGA接口电平3.3 V,为保证BU-61580与FPGA正常数据通讯,考虑接口电平匹配电路设计是十分必要的。SN74LVC4245是双向电平转换芯片,既能解决电平转换问题,又能保证数据总线双向传输。

2.2 RS422总线接口设计

本系统通过RS422接收导航数据、距离数据、命令控制;通过RS422将融合编帧数据向上级系统传输。RS422是全双工总线,可将接收数据与发送数据构成完整RS422传输接口,充分利用系统硬件资源。命令控制总线用于接收上级系统指令,保证系统指令的正确接收,采用9 600 bps,停止位1 bit,无校验格式进行指令接收。为了保证数据存储系统数据传输的可靠性,选用AM26LV31E和AM26LV32E作为RS422接口芯片[8],具备四路三态输出BICOMS差分线路驱动器,具有超低功耗、低成本、传播延时低等优点,最高开关切换速率可达32 MHz。RS422总线接口设计如图4所示。

图4 RS422总线接口设计

2.3 配置电路设计

配置电路共由2部分FLASH存储单元组成,其中M25P16是SPI FLASH,容量16 Mbit,最高通讯时钟75 MHz,用于存储FPGA动态重构代码;24LC02是EEPROM,采用I2C总线通信方式,具有2 Kbit存储空间,用于存储上级系统控制信息以及本系统参数信息,当系统接收动态重构命令后,将参数数据进行保存,保证FPGA重构后可重新加载配置参数。配置电路设计如图5所示。

图5 配置电路设计

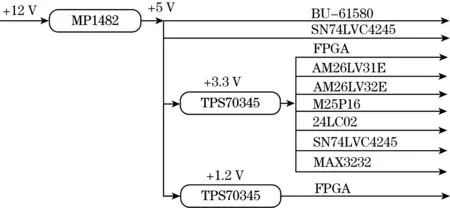

2.4 电源电路设计

系统供电网络图如图6所示,采用12 V输入供电,FPGA电压需求1.2 V和3.3 V,RS232和RS422接口芯片工作电压3.3 V,BU-61580工作电压5 V,存储芯片M25P16和24LC02工作电压3.3 V,SN74LVC424工作电压3.3 V和5 V,本系统选用MP1482 DC-DC电源作为一级电源产生5 V电压用于BU-61580和SN74LVC4245使用,二级电源选用双路LDO TSP70345产生3.3 V和1.2 V电源供系统使用。经计算,MP1482最大输出功率为10 W,TSP70345最大输出功率为5.7 W,能够可以满足系统设计需求。

图6 系统供电网络图

3 软件方案设计

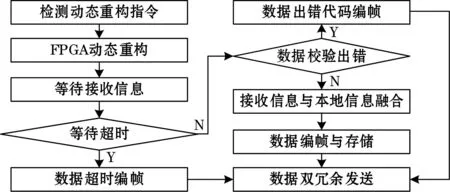

多总线动态重构监测输系统软件逻辑如图7所示。软件逻辑按照其功能可分为时钟生成、数据接收、数据融合、双冗余传输、ICAP动态重构、本地信息获取。时钟生成将50 MHz晶振时钟通过PLL分频或倍频产生时钟供其他部分使用;数据接收用于监测来自于并行通讯层数据,并对接收数据进行校验解析存储至双端口RAM;数据融合将双端口RAM中数据与本地RTC数据和EEPROM数据进行融合编帧,并将其存储至2个异步FIFO中;双冗余传输判断2个异步FIFO中存储数据容量是否满足传输需求,待满足需求按照与上级系统约定的信道传输速率,将信息通过双冗余RS422总线接口传输至上级系统;ICAP动态重构,根据上级系统指令需求,动态读取存储在片外FLASH中不同偏移地址的bit文件,实现FPGA动态重构的功能;本地信息包含本地RTC时钟和EEPROM信息,其中EEPROM包括上级系统参数配置信息和本系统状态信息。

图7 系统软件框图

3.1 动态重构逻辑设计

FPGA通过ICAP实现内部程序动态重构,FPGA动态重构分为动态全局重构和动态局部重构[9],动态局部重构由于不同bit文件中存在不同的时序约束,采用动态局部重构存在系统运行不稳定的风险,本系统各部分功能bit文件较小,两种模式下程序加载重构时间基本一致,本系统采用动态全局重构技术,根据上级指令动态加载bit文件。ICAP动态重构流程如下:

步骤1:系统上电后,FPGA首先加载Golden镜像,检测系统各部分功能是否正常,包括RS422接口、1553B接口、EEPROM以及SPI FLASH,并将自检结果反馈至上级系统;

步骤2:等待上级系统动态重构指令,并持续向上级系统反馈检测结果;

步骤3:接收到上级系统重构命令后,将指令参数存储至EEPROM,根据指令加载SPI FLASH中对应偏移地址的bit文件,待程序加载完成后执行相应程序;

步骤4:系统正在运行时,当接收到上级系统重构命令后,执行步骤同步骤3。

3.2 双冗余传输逻辑设计

采用双冗余传输技术可以保证系统数据传输的可靠性,RS422总线采用双端收发的方式,具有强抗干扰能力和高通讯速率,将RS422总线与双冗余传输技术相结合,系统数据传输速率和可靠性同时得到保证。本系统采用RS422双冗余传输接口,实现向上级系统传输数据。本系统根据当前执行的程序,动态将状态信息、导航信息、距离信息或图像信息与本地信息进行数据融合编帧,将数据帧存储至2个异步FIFO,再根据与上级系统约定的信道传输速率分别将2个FIFO中的重组数据通过2路RS422总线接口发送至上级系统,构成RS422双冗余数据传输总线。数据接收与传送流程如图8所示。

图8 数据接收与传送流程图

4 系统测试与分析

4.1 动态重构性能测试

本系统根据指标要求动态重构时间小于1 s,通过测量动态重构指令下发时间与重构完成后自检信息上传时间间隔,计算动态重构时间。测试记录结果如表1所示。

表1 动态重构时间测试记录

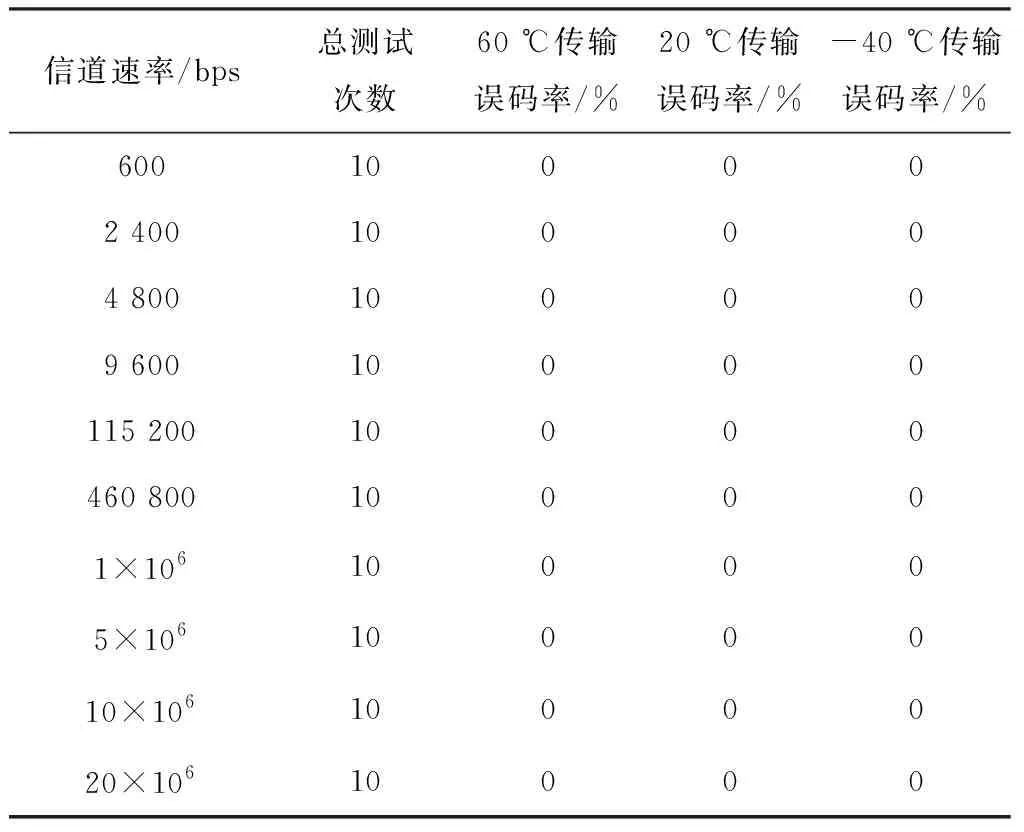

4.2 双冗余信道速率测试

根据技术指标要求600 bps~20 Mbps信道速率速率,本系统选择6种标准波特率和4种非标准波特率进行测试,标准波特率选择600、2 400、4 800、9 600、115 200、460 800 bps;非标准波特率选择1、5、10、20 Mbps。

测试方法借助中间层部件,通过测量融合数据帧结构数据长度到CRC校验传输时间,上位机反算双冗余信道传输速率。波特率9 600 bps速率测试结果如图9所示。

图9 9 600 bps速率测试结果

数据传输误码率与数据传输速率有着举足轻重的作用。多次测试在不同信道速率下数据的可靠性。测试结果如表2所示。

表2 误码率测试记录

5 结论

目前,针对任务书需求实现的基于FPGA多总线动态重构监测系统,在高低温环境下分别对系统重构时间测试,在同一环境下经过多次试验测试获得各信道平均重构时间均小于1 s,满足系统设计需求,降低了系统复杂度,提升了系统可维修性,降低了硬件系统资源占用;双冗余信道传输速率经测试最大波特率可达20 Mbps,满足系统设计需求,在双冗余信道动态波特率下,数据传输稳定,误码率为0,满足系统可靠性需求。