基于FPGA的异步串行通信波特率容错设计

2018-05-16肖鹏屈盼让孙少华李庆楠

肖鹏,屈盼让,孙少华,李庆楠

(中航工业西安航空计算技术研究所,陕西西安,710119)

0 引言

串行通信广泛应用于数字通信和工业控制领域,传统的专用串口通信芯片接口复杂,体积较大,随着微电子技术的发展,FPGA在数字电路设计中被广泛使用,完全可以将串口通信的功能集成在FPGA内,这样不仅减少了外围电路的体积,降低了设计的复杂性,同时可通过设计可以提高数据通信的可靠性。

1 系统概述

如图1所示,异步串行通信系统由传感器/数据模块、电平转换模块、FPGA和上位机组成。核心部分是FPGA。FPGA控制完成串行数据的采集和发送,上位机通过软件读取FPGA中FIFO的数据或向FIFO中发送数据。

2 数据采样波特率容错设计

在数据接收中对数据的接收是在监测到起始位后按照要求的波特率采样,在通信过程中受到干扰的话就会出现监测到假数据起始位,造成数据错误和误码。为了提高接收数据的准确性,减少误码率,应采用数据传输波特率n(n≥1)倍的速率对数据进行采样。

图1 系统原理框图

图2 16倍波特率速率采样示意图

图3 16倍波特率速率采样时情况1

图4 16倍波特率速率采样时情况2

以16倍波特率速率采样为例:采用数据传输速率的16倍进行采样,采样时钟连续采样到8个低电平信号时可以确定此时的低电平信号为正确的数据起始位,这样可以排除干扰信号产生的错误起始位信号。在采集到第8个低电平之后,每隔16个采样时钟对数据采样一次,并将采样到的数据作为接收的数据发送给移位寄存器,最后通过移位存入到接收FIFO中。采样过程如图2所示。

采用n倍波特率速率采样的方法的关键是采样到次低电平信号确定起始位,此时可以保证该位为起始位数据波形的中点,这种采样方法可以提高对串行数据波特率的容错性。当采用n倍波特率速率采样时保证数据采集的两种极限情况,一种情况是数据采样的最后一次采样在实际数据最后一位有效的最开始时,如图3所示。另一种情况是数据采样的最后一次采样在实际数据最后一位有效的最后时刻,如图4所示。根据这两种情况可计算出采用n倍波特率速率采样的比特率容错范围。

假设标准波特率为,实际波特率为,则对于图3情形有式(1)。

可得出实际波特率 BRmin=0.952Bs

对于图4情形有式(2)。

可得出实际波特率 BRmax= 1 .048Bs。那么采用n倍波特率速率采样串行数据,FPGA设计实现的波特率的误差在正负4.8%之内就可以准确的采样到数据,考虑到远端传输可能出现误差,将设计的波特率误差控制在2.5%以内以保证数据的准确。

上述计算忽略了波特率速率倍数n的影响,实际应用中发现n的值越大,波特率的容错范围会更宽。

3 实验验证

以UART RS422为例,使用VHDL语言编写UART RS422收发控制逻辑。波特率发生器使用独立的时钟且波特率可配置。接收数据采样使用FGPA系统主时钟,则采样速率相对波特率的倍数即位时钟频率相对波特率的倍数。硬件平台资源:FPGA使用Xilinx Virtex-4,串行通信协议芯片使用MAX3490,系统主时钟频率20MHz,异步UART收发波特率发生器使用时钟频率16MHz。

3.1 实验设计

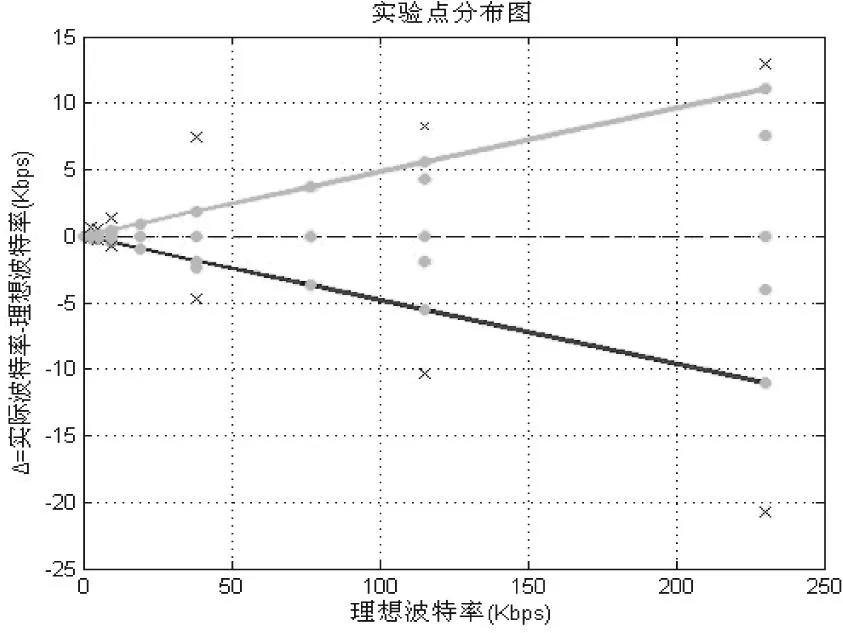

试验中将PC机作为上位机,通过UART RS232与 FPGA通 信,RS232的 通信是FPGA开发板接口电路实现。UART RS422发送的数据通过外部回绕接收回来以观察数据的正确。通过分析计算的能够准确接收数据的实际波特率与对应理想波特率差的范围如图5中两条实线包含的范围。

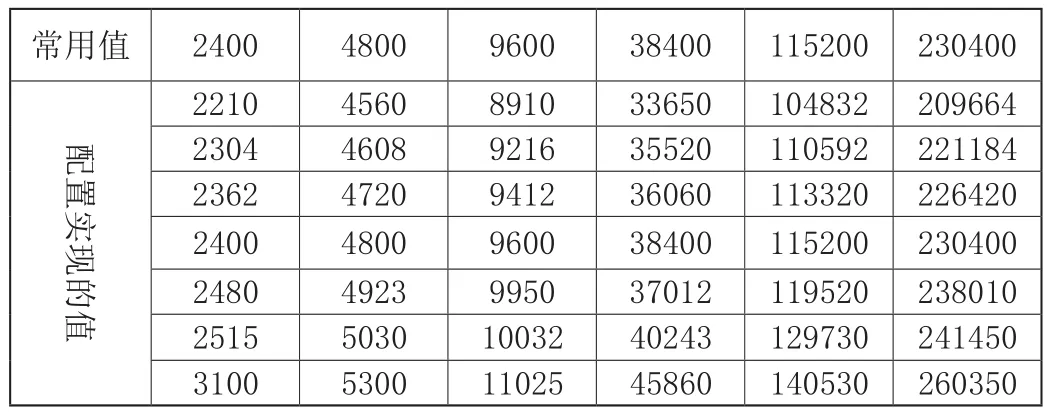

实验中通过配置分频因子寄存器配置波特率,在不同的波特率下观察接收的数据是否与发送的数据一致,实验中选取常用的波特率及常用波特率附近的波特率进行试验,配置的UART RS422波特率如表1所示。

图5 波特率容错范围

表1 实验使用波特率对应表(bps)

3.2 实验结果

在上位机PC上通过串口调试助手发送配置寄存器地址和数据读写地址。实验结果如图6所示。

图6 实验结果数据

图中圆点表明实验中FPGA接收的数据正确,叉点表明实验中数据不正确。从图中可以看出,实际波特率与对应波特率差在两条实线范围内的实验点FPGA接收到的数据均是真确的,而实际波特率与对应波特率差在两条实线范围外的实验点FPGA接收的数据都不正确。

4 结论

本文设计一种基于FPGA的异步串行通信模块,并设计一种通用的异步串行通信数据接收模块的数据采集方法以提高对异步串行传输波特率的容错度。设计实验进行波特率容错的验证。通过对实验的结果可以得出,实际波特率与对应理想波特率的差在±4.8%的范围内的,FPGA采集到的数据均是正确的,实际波特率与对应理想波特率的差超出这个范围的,FPGA采集到的数据都不正确。以此验证了设计的方法可以提高异步串行通信中对数据传输波特率的容错性,当电路受到干扰使得晶振输出的时钟频率发生微弱变化的时候能够继续保证串行数据的准确性,提高了异步串行通信的抗干扰能力。

参考文献

[1]党俊博,李哲,李雅俊.基于FPGA的串口通信电路设计与实现[J]电子科技,2016,29(07): 106~109.

[2]韩佩富,潘峰,赵新秋 基于VHDL的异步串行通信电路设计[J].微电子技术,2003,31(04): 29-33.