电子封装金属微凸点制备技术研究进展*

2024-01-02王凌云

王凌云,郑 康

(厦门大学萨本栋微米纳米科学技术研究院,福建厦门 361102)

引 言

随着电子信息技术的飞速发展,电子产品不断向微型化、多功能化和高集成化的方向发展。在不断增长的需求推动下,微电子封装技术经历了插孔元件时代、表面贴装时代、面积阵列时代和2.5D/3D封装时代。

自20世纪90年代以来,集成电路进入了超大规模阶段,单颗芯片的引脚数高达上千个。传统的双列直插封装(Dual In-line Packaging, DIP)和方形扁平封装(Quad Flat Packaging, QFP)在不增加整体尺寸的情况下只能不断缩减引脚尺寸及间距,当引脚数超过500时,微小的安装误差就可能导致焊锡桥接和断路。在此背景下,以面积阵列排布输入/输出(Input/Output, I/O)凸点的封装形式—球栅阵列封装(Ball Grid Array Packaging, BGA)、芯片尺度封装(Chip Scale Packaging, CSP)、晶圆级芯片尺度封装(Wafer Level Chip Scale Packaging,WLCSP)以及倒装芯片封装(Flip Chip Packaging, FCP)陆续登上历史舞台,它将有源区面上制有凸点电极的芯片朝下放置,与封装基底/基板布线层直接键合实现冶金连接[1–2]。这种基于面积阵列的封装方式不仅提高了硅片的利用率,还具有互连路径短、信号传输延时短、寄生参数小等优点。进入21世纪后,芯片中的晶体管数量仍在急剧上升,传统二维芯片的尺寸不断逼近摩尔定律的极限,因此人们寻求在垂直方向进行芯片集成,于是出现了3D封装,又叫叠层芯片封装。

不论是对于当下的面积阵列封装还是未来的3D封装,以金属微凸点作为电互连和机械支撑非常普遍并将延续很长时间。然而,不同封装层级间微凸点的尺寸跨度大、材料范围广,很难有一种技术能覆盖全尺寸范围内微凸点的制备,微凸点的制备工艺将决定该技术未来几十年的发展。

1 金属微凸点制备工艺

微凸点阵列的制备方法主要有2类:一类是通过专用设备将预成型精密焊球放置在基板上特定位置来形成凸点阵列,典型工艺有植球法;另一类是凸点阵列直接制备法,主要有钉头凸点法、丝网印刷法、蒸镀法、电镀法(化学镀法)、可控塌陷芯片连接新工艺(Controlled Collapse Chip Connection New Process,C4NP)以及喷射法。如图1所示,凸点工艺主要包括凸点下金属层(Under Bump Metallization, UBM)的制备以及凸点的制备,涵盖了不同微凸点的制备方法。

图1 微凸点制备技术[3]

1.1 植球法

有多种植球法,其中一种是将带有微孔阵列的吸盘置于容器上方,通过振动容器使焊球跳动,从而使其吸附于小孔之上(为去除多余焊球,可采用超声振动工艺);随后通过光学手段来检测吸孔与焊球位置的准确性,紧接着将吸盘与晶圆/基板焊盘对齐,缓慢降低吸盘,使焊球置于焊盘之上,去真空释放焊球,使吸盘与焊球分离;最后对晶圆/基板进行加热回流形成焊锡凸点。其工艺流程如图2所示。该方法简单快捷,生产效率高,可灵活应用。与电镀法相比,其成本较低且无化学污染[4],但也存在以下不足:1)对焊球的一致性要求较高,否则容易出现卡球、丢球或漏球现象;2)对助焊剂及回流温度设定的依赖度较高,助焊剂挥发产生的气流扰动容易使焊球位置偏移,不当的回流温度容易造成凸点连焊;3)较难应用于细节距产品,因为难以涂布助焊剂和拾取极小的焊球;4)不适用于多尺寸焊盘的情况,如果将大小相同的焊球置于不同尺寸的焊盘上,就会降低焊锡凸点高度的共面性[5]。

图2 基于真空吸盘植球的微凸点制备工艺流程图[6]

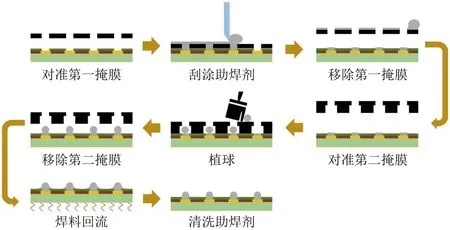

另一种是先利用第一漏印掩膜在基板焊盘上涂刷黏性助焊剂,随后在第二漏印掩膜上均匀散布直径相同的焊球,掩膜通孔与基板焊盘对齐,紧接着采用挤压刷将焊球压入掩膜通孔中,从而使焊球黏附于涂有助焊剂的焊盘上,完成植球后移除第二漏印掩膜,最后加热回流,使焊球熔化形成凸点。其工艺流程见图3。

图3 基于漏印掩膜植球的微凸点制备工艺流程图

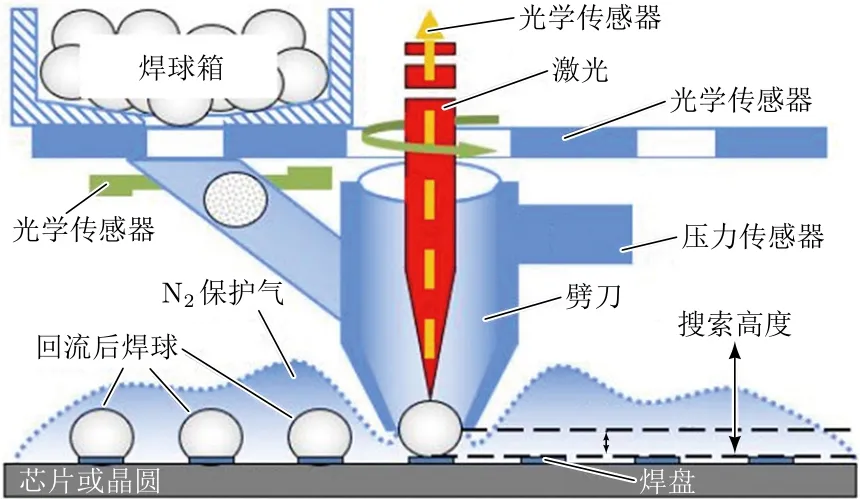

德国Pactech公司提出的激光植球技术可一步实现植球与回流工艺,其原理如图4所示。在氮气气氛下利用激光束将焊球熔化在焊盘上形成凸点。该方法可用于晶圆或芯片焊盘上焊料凸点的制备,灵活性强[7]。由于激光局部加热产生的热影响区小,因此可以避免周围元件的损伤,减少植球过程中金属化合物层的形成,有利于提高焊点质量。激光植球技术可以实现焊球直径为40~760 μm的可靠连接[8],但文献[9–11]指出,该技术在焊点制备过程中会出现焊球润湿不良、焊球凹陷、局部烧蚀等缺陷,造成焊点可靠性差。

图4 Pactech公司的激光植球法原理图[12]

1.2 钉头凸点法

钉头凸点键合技术由Matsushita公司于1997年提出[13]。该方法借鉴了引线键合工艺[14–15],在第一焊点完成后劈刀继续向上拉伸,使金丝颈缩断裂形成金凸点,具体工艺(图5)如下:

图5 钉头凸点法工艺流程图

1)首先利用电火花放电在金丝末端形成金球,金球尺寸可通过设置打火杆的电流、打火杆与线尾的间距以及放电时间来控制;

2)随后在加热、加压和超声的共同作用下,将金球键合到芯片的焊盘上;

3)当第一焊点完成后,劈刀垂直向上运动,此时线夹处于打开状态,送出一段尾丝;

4)线夹关闭,劈刀向上运动,金丝在拉力的作用下断裂形成带有尾尖的凸点;

5)当所有凸点制作完毕后,通过研磨、石英板拍平等工艺去除尾尖,使其成为高度、平整性一致的芯片凸点。

在一般情况下,为了提高倒装焊金凸点与铝焊盘连接的可靠性,通常会预先在铝焊盘上溅射/蒸镀一层UBM,而后再进行钉头凸点制作。

钉头凸点法只适合引脚较少、焊盘节距较大、品种多但数量相对不多的芯片封装,具有简便易行、方便灵活、可在单芯片上制作凸点、成本低廉等优点,但也存在凸点高度一致性较差、效率低等缺点。此外,由于金是贵金属材料,当封装器件的引脚数较多时,其成本要比焊料凸点高。文献[16]尝试使用带有铜凸点的芯片与焊盘印刷有无铅焊料的基板互连,意欲取代成本高昂的金凸点与导电胶键合的传统互连工艺,获得了不错的效果,但由于铜凸点抗氧化、抗腐蚀能力差,目前很少使用。随着键合工艺以及材料技术的提升,铜丝有望取代金丝成为新一代凸点键合材料。

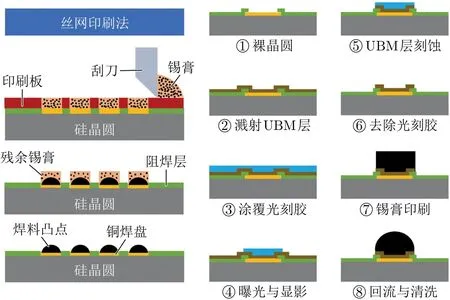

1.3 丝网印刷法

丝网印刷法是通过涂刷器和网板将锡膏涂刷在焊盘上的凸点制备技术,适用于间距为200~400 μm的焊盘。其工艺主要包括UBM制备、锡膏丝网印刷、锡膏回流和焊盘清洗等步骤。图6所示是目前应用较广的低成本钎料凸点制备方法,具有效率高、成本低、适用于不同种类钎料合金的优点[17]。然而,该方法在节距小于150 μm的高密度互连中面临较大的挑战。在细节距产品中,印刷后助焊剂容易桥接,这为回流后焊料的桥接埋下了较大隐患。在回流过程中溶剂挥发,空洞数量和凸点高度变化较明显,降低了芯片贴装良率。为提升贴装良率,需采用压印工艺保证所有焊锡凸点的共面性。此外,由于小节距焊盘掩膜的制备成本较高,因此其应用受到了一定的限制[18]。

图6 丝网印刷法工艺流程

随着掩膜加工技术的提升、纳米材料制备技术的日趋成熟以及印刷工艺的优化,丝网印刷工艺在制备节距小于100 μm的倒装芯片焊料凸点领域愈发成熟。文献[19]在优化工艺参数的基础上成功实现了在晶圆上制备节距为90~100 μm的焊料微凸点。

1.4 蒸镀法

20世纪60年代IBM公司最早提出采用蒸镀法制备凸点,主要应用于大型计算机中的多芯片模块[17]。在蒸镀工艺中,先利用光掩膜制作UBM,然后将钎料蒸发到UBM上得到锥形凸点,最后对锥形凸点进行加热回流使之成为半球状,如图7所示。

该方法与集成电路(Integrated Circuit, IC)工艺相兼容,可充分利用现有设备且工艺成熟,但需要制作掩膜,且一种掩膜只能针对一种IC芯片。蒸镀工艺的缺点主要表现在:1)投资高,生产效率却不高,因此该方法仅用于要求凸点材料纯度高、制备的凸点密度高或制备的凸点材料不能使用电镀或印刷工艺等场合;2)由于大部分焊料被蒸发到掩膜和反应腔室的内壁上,因此该工艺的材料利用率极低;3)每次蒸镀结束后,必须对附着在金属掩膜上的焊料予以清除,而清除操作会降低掩膜质量,改变开孔尺寸,从而缩短了掩膜的寿命。UBM的制作通常使用多个蒸发器,这使得焊料成本进一步增大。蒸镀工艺一般可接受的面阵列节距极限是225 μm,当节距低于200 μm时,原先采用蒸镀工艺的公司都转向采用电镀工艺[6]。

1.5 电镀法

电镀法是微电子封装企业普遍采用且工艺成熟的凸点制作方法[20],常用于晶圆凸点的制备。电镀凸点所需的UBM同样是采用蒸发/溅射的方法,但比UBM厚许多倍的凸点则采用电镀工艺制备。电镀法制备的凸点主要有铜柱凸点和焊料凸点2大类。铜柱凸点一般是在芯片焊盘上电镀一定尺寸的铜柱后,再在铜柱上表面电镀可焊性镀层(SnPb、SnAg、Sn等),以便实现后续的互连或组装,是当前凸点应用的主流方向。铜柱凸点被认为是可以实现窄节距凸点互连的主要材料,其特点是高度一致性好,可靠性高,节距可低至20 μm甚至更低。焊料凸点则是直接在芯片上电镀焊料层,经回流后形成焊料凸点。图8为电镀低温钎料凸点的制作工艺流程图。

图8 电镀低温钎料凸点工艺流程

电镀工艺具有重复性好、一致性高的优点,同时制备工艺与IC、微机电系统(Micro-Electro-Mechanical System, MEMS)工艺相兼容,可用于批量生产各类规格芯片及不同材料、不同高度的凸点,但由于资金和运营成本高,电镀技术在小型设施中的使用受到了一定的限制。此外,三元合金(如SnAgCu)很难以一致的结果进行电镀[18,21]。

1.6 C4NP法

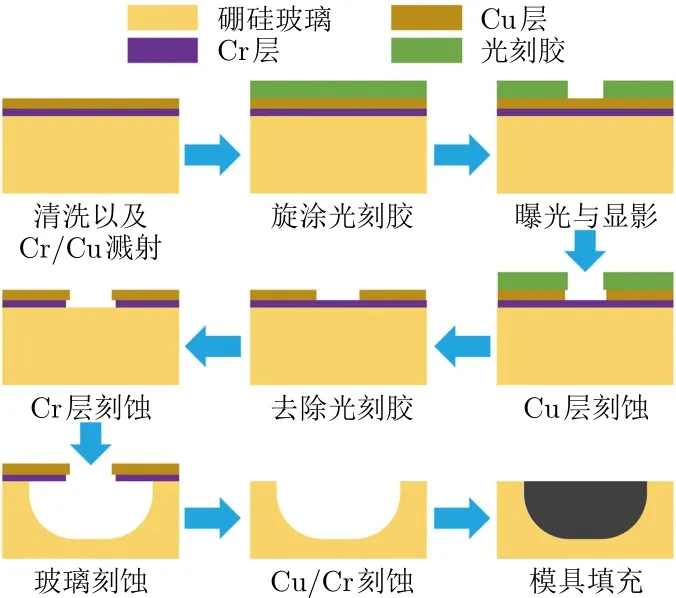

C4NP法是IBM公司研发的低成本细节距焊锡凸点制作技术,克服了现有技术的局限性,可采用多种无铅焊料合金[22]。它是一种焊料转移技术,需将熔融焊料注入预制的可重复使用的玻璃模具中,主要包括5个环节:模具制造、焊料填充、模具与晶圆对准、焊料转印与脱模以及加热回流。其中,模具制造是该工艺的关键,它包含了晶圆凸点图形的刻蚀空腔,考虑到焊料在硼硅玻璃表面的非浸润性,通常采用硼硅玻璃制作。图9为模具制造及焊料填充工艺流程图。

图9 模具制造及焊料填充工艺流程图

将焊料转移至晶圆之前,需对已填充的模具进行检查以确保较高的良率。然后在回流温度下将填充好的模具软接触贴近晶圆,所有的焊料凸点将一次性全部转移至晶圆上。该过程并无与液体流动相关的复杂问题,其工艺流程如图10所示。

图10 焊料从模具到晶圆的转移过程[22]

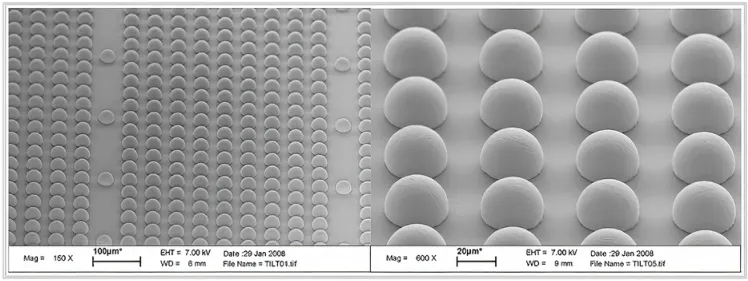

2008年IBM公司以甲酸蒸汽作为助焊剂,利用C4NP技术在直径为28 μm的UBM焊盘上成功实现了直径约为50 μm的SnAg无铅焊料微凸点的制备[23],如图11所示。初步结果显示:C4NP技术能轻易实现直径在50 μm以下的微凸点的制备,以满足I/O密度不断攀升的需求。

图11 50 μm直径微凸点SEM图[23]

1.7 喷射法

喷射法能实现熔融焊料的高精度、超微细控制,广泛应用于电子封装领域球栅阵列锡球的直接喷射制备、喷射印刷电路、直接金属快速成型、电互连接头以及液滴铅焊等[24–26]。喷射法按原理可分为连续式喷射和按需式喷射。连续式喷射通过离散层流射流来实现均匀液滴的制备,喷射的微滴具有频率高、飞行速度快等优点,但不易对单颗微滴的飞行过程和沉积位置进行控制,故不适用于直接植球,多用于造粒[27–28]。按需喷射因其能精确控制液滴的体积和沉积位置,故可用于直接植球[29]。

喷射法按驱动方式分主要有压电驱动式、热泡式、气动式、应力波驱动式、超声振动式和电磁力驱动式[30]。其中,压电驱动式是目前应用最广且商用最成功的微液滴制备方式,但因压电材料难以耐高温,需要设计较复杂的冷却系统和隔热装置;气动式中的气动膜片式解决了喷射阀不耐高温且可喷射材料熔点受限等问题,但存在频率较低、噪声较大的弊端[31–32];应力波驱动式能获得比喷嘴直径更小的液滴,液滴直径约为喷嘴直径的0.6倍,可大大降低喷嘴的加工难度与成本[33],但存在喷射微滴定位精度差且伴有噪声的缺点;电磁力驱动式被认为是极具潜力的驱动方式,最早应用于微泵中导电流体的驱动[34],具有结构简单、响应快、不依赖外部气源等优点,但喷射材料必须为导体,且在喷射较高熔点材料时,需做好阀体与永磁铁的隔热,因较高的温度会导致永磁铁退磁。

采用喷射法在芯片/基板焊盘表面直接植球具有效率高、成本低、工艺简单的优势[35–36]。因此,利用微喷技术制造精密焊点成为面积阵列封装领域的研究热点[37–38]。然而,因存在工艺控制困难、一致性较差的不足,喷射法难以实现商业化应用[39]。喷射法一般采用按需喷射模式来实现熔融态低熔点焊料的沉积,文献[40–44]也实现了铝合金、铜等高熔点金属的喷射打印。其最大特点是非接触且无需掩膜,可通过调节气压、脉冲波形、脉宽、喷嘴尺寸等参数轻易控制液滴尺寸。此外,熔融态焊料喷射沉积于芯片/基板焊盘后与UBM直接键合,无需对整个芯片/基板进行较高温度的加热回流,有效保护了温度敏感型电子元器件及内部集成电路。文献[45–46]表明:焊料的多次回流将严重影响焊点的力学性能,而采用丝网印刷、电镀等工艺制备金属微凸点时,回流次数在20次以上[6],这是喷射法的独特优势之一。

2 金属微凸点常见材料

目前通用的凸点按照材料成分来分主要有以铜柱凸点、金凸点、镍凸点、铟凸点等为代表的单质金属凸点、以锡基为代表的焊料凸点、聚合物凸点等。

1)金凸点、铜柱凸点常用于小节距的高端芯片领域,具有电导率高、抗电迁移特性好的优点,通常采用电镀或钉头凸点方式制备。

2)镍凸点和铟凸点通常用于特殊场合。镍凸点常用化学镀方式制备,铟凸点常用电镀或蒸发薄膜的方式制备。

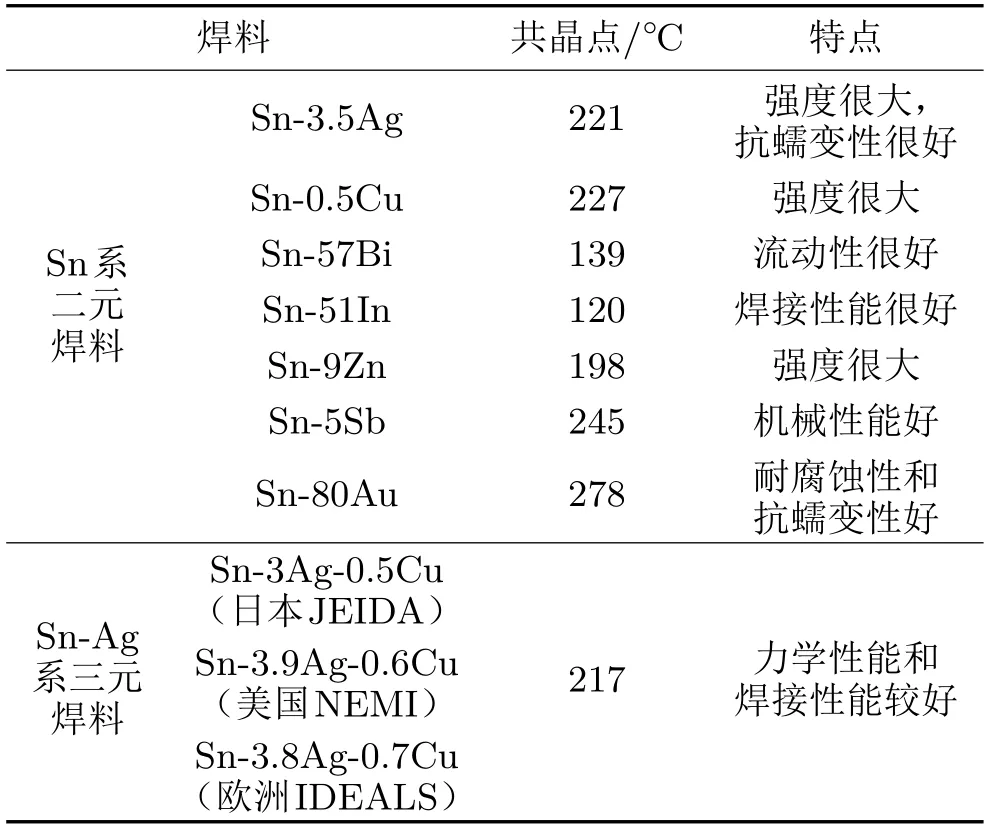

3)焊料凸点一般以锡基焊料为主,多为二元或三元及以上多元合金,其加工过程比锡铅焊料复杂,且熔点普遍较高。表1为可能取代锡铅焊料的无铅焊料。

表1 可能取代锡铅焊料的无铅焊料[7]

4)聚合物凸点一般由导电聚合物制备,主要用于柔性器件封装领域。其互连工艺温度远低于焊料凸点的工艺温度,通常在140°C~170°C范围内。聚合物凸点具有高度一致性好、可靠性高的优点,其设备和工艺也相对简单,但它缺乏焊料凸点的自对中性能,位置容差较小,键合前必须进行高精度对准。

基于成本考虑,当节距较大(≥100 μm)时,焊料凸点仍然是基于面积阵列凸点制备的首选,而采用电镀法制备的铜柱凸点将是高密度、窄节距微器件封装领域当下和未来很长一段时间的主流。这是因为随着封装密度的提高,器件的热流密度不断增大[47],对无铅焊料微凸点互连器件的可靠性构成了严峻的挑战。目前,最先进的铜柱凸点节距低至40 μm,凸点尺寸约为20~25 μm,相邻凸点间距为15 μm[48]。

3 结束语

虽然目前基于无铅焊料微凸点的制备技术比较成熟,但随着芯片特征尺寸的不断减小以及片上系统(System on Chip, SoC)、多芯片集成等技术的发展,I/O互连数量势必激增,这将进一步压缩微凸点的尺寸和节距。然而,当无铅焊料微凸点的尺寸和节距小于一定值时,将出现一系列可靠性问题,如界面反应、热疲劳可靠性、跌落冲击可靠性、电迁移可靠性等。因此,在不久的将来细节距铜柱凸点将逐渐取代无铅焊料凸点成为主流的封装材料。此外,由于芯片三维堆叠封装具有小尺寸、低功耗、低延迟和高带宽等优点,能显著提升集成电路的系统性能。因此,3D集成技术将成为评估晶圆封装企业是否具备核心竞争力的筹码,而与之对应的高密度硅通孔(Through Silicon Via,TSV)互连技术将备受关注。