基于通用异步收发器的高速SerDes 测试

2023-11-13柏娜朱非凡许耀华王翊陈冬

柏娜,朱非凡,许耀华,王翊,陈冬

(1.安徽大学信息材料与智能感知安徽省实验室,合肥 230601;2.安徽大学物联网频谱感知与测试工程技术研究中心,合肥 230601)

1 引言

随着集成电路行业的发展,在传输接口方面,国内外对数据传输速率的要求越来越高[1]。近些年,串行解串器(SerDes)接口因其具有较少的信道需求与器件管脚数目的优势,逐渐取代了传统并行接口芯片成为通信行业的新宠,其跟随通信协议,被广泛应用在电信、IT 和个人消费电子领域[2]。与此同时,随着集成技术和制造工艺的不断进步,专业SerDes 接口的电路结构愈加复杂,性能要求也愈加严格,越来越高的集成度与越来越快的传输速度对测试技术也提出了越来越严格的要求[3]。为保证芯片的成功流片,降低测试所需的成本,针对高速SerDes 的高效调试方法成为了必要的研究课题[4]。

对于SerDes 的相关功能测试,大多数厂商采用仪器仪表与评估板来评估待测器件的方式效率低下,只适用于产品评估阶段[5],采用FPGA 可以覆盖不同层的测试,安全性高但通用性较差[6]。本文利用SerDes 芯片的环回模式,引入内建自测试的方法,可以快速定位故障点,同时降低对测试设备通道和速度的要求[7]。但在常规的内建自测试中,由于SerDes 芯片在封装时有管脚数量的限制,难以把物理层(PHY)的测试点全部引出作为测试芯片的管脚,从而导致测试操作繁琐,调试配置参数的周期延长[8]。而把通用异步收发器(UART)模块与待测IP 级联,将UART 模块作为PHY与外界通信的转换模块,通过UART 模块将SerDes调试所需的配置参数传输到PHY 的控制寄存器,控制寄存器的控制端可以完成对PHY 内部寄存器的读写操作,由此实现了对SerDes 芯片参数的动态调试,极大地减少了测试复杂度和测试时间。该方法方便测试人员进行调试,具有通用性。本文介绍了基于UART的高速SerDes 测试方案,详细阐述测试电路的设计以及前仿功能验证、逻辑综合与静态时序分析、后仿验证等测试具体流程。

2 SerDes IP 结构介绍

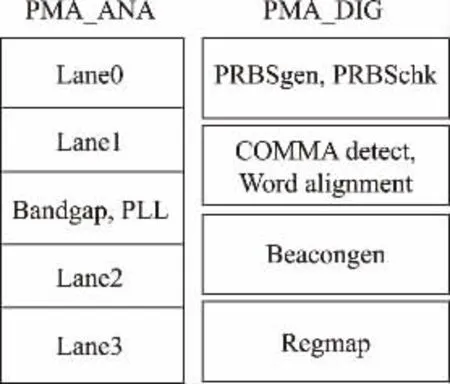

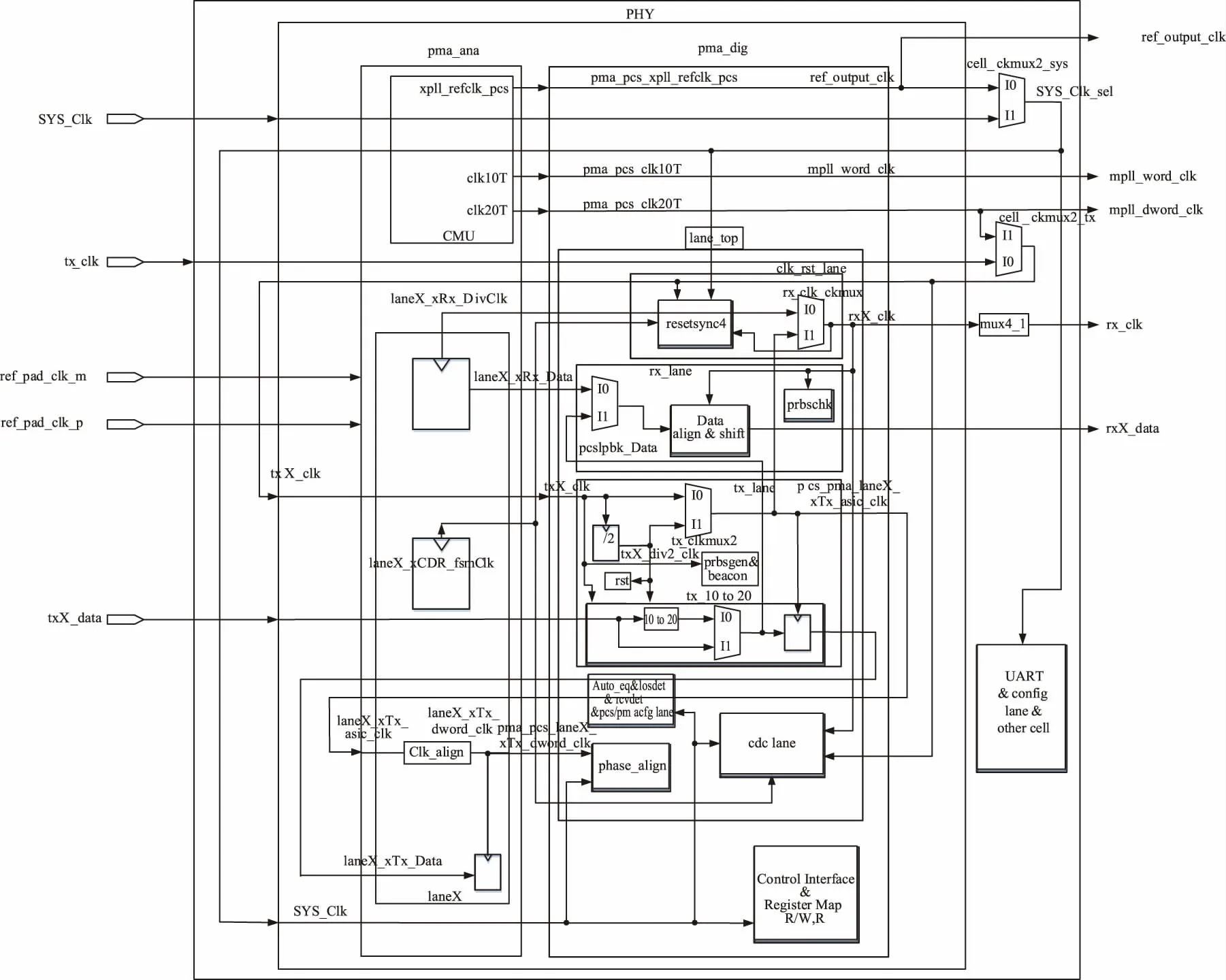

待测SerDes IP 的总体结构如图1 所示,该模块可以满足必要的PCIe 和RapidIO 协议物理介质接入层(PMA)的要求,模块可分为数字和模拟两个部分。其中伪随机序列产生器与检测器(PRBSgen,PRBSchk)、COMMA 检测与字界对齐模块(COMMA detect,Word alignment)、Beacon 产生器(Beacongen)以及控制寄存器(Regmap)组成了数字部分。COMMA 检测与字界对齐模块通过检测串并转换得到并行数据中的COMMA 字符,寻找并行数据的字界边界,对齐字界边界后输出串并转换后的并行数据。Beacon 产生器产生PCIe 协议定义的Beacon 信号,用于低功耗模式下的唤醒操作。控制寄存器存储了SerDes 的所有配置信息,SoC 可以通过其访问通道进行修改配置,调节SerDes 的参数配置。锁相环(PLL)、带隙基准(Bandgap)、四个独立传输通道(Lane0、Lane1、Lane2、Lane3)组成了模拟部分。锁相环给发送端和接收端提供四相时钟,用来恢复对数据进行采样的时钟。带隙基准给其他模块提供与温度无关的偏置电流[9]。

图1 待测SerDes IP 的总体结构

待测IP 内部包含的PRBSgen 与PRBSchk,可以产生lfsr7/15/21/31 格式的伪随机序列,便于通过SerDes 的环回模式进行SerDes 的内建自测试。

3 设计测试方案

3.1 测试难点与解决方案

待测SerDes IP 在测试中面临的问题主要有以下三点。

1)信号衰弱:考虑到信号在传输过程中会发生不可避免的衰弱问题[10],从而导致信号对之后功能单元的驱动能力不足,进而产生新的问题,因此设计了输入输出缓冲单元用来增强信号驱动能力和实现静电保护作用,此单元由大量缓冲器构成,除了差分参考时钟外,其余时钟信号的输入、输出均通过此单元。

2)亚稳态:本设计采用异步复位,特地设计了由触发器构成的复位同步单元,采用双重时钟周期同步方式进行单bit 同步,实现同步复位异步释放功能,确保复位信号的释放依赖于时钟有效沿,避免了恢复时间和消除时间的不足产生亚稳态[11]。

3)测试点过多:SerDes 芯片在封装时管脚数量受限,难以把PHY 的测试点全部引出作为测试芯片的管脚[12]。为了减少测试点的数量,本文引入了UART 作为PHY 与外界通信的转换模块。将UART 等模块与待测IP 级联,通过UART 单元将SerDes 调试所需的配置参数传输到PHY 的控制寄存器,进而完成控制寄存器控制端对PHY 内部寄存器的读写操作,并基于此设计引用了UART 与控制寄存器的桥接单元,使UART 的数据及控制信号通过UART 桥接单元与PHY 内部的寄存器连接,从而进一步减少了管脚数量。

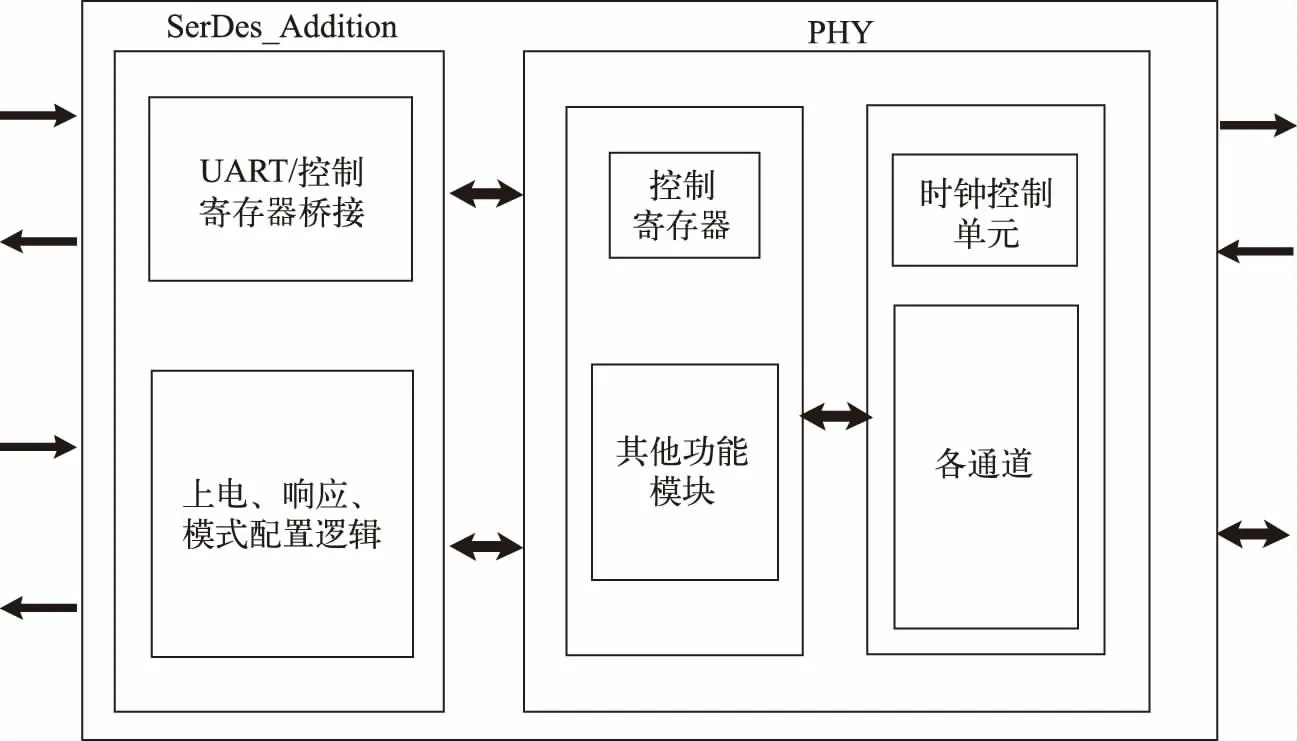

3.2 测试电路结构

利用SerDes 的环回模式进行内建自测试,依照模块设计方案引入UART 单元,设计出包括待测IP 的PHY 和SerDes 附加测试结构(SerDes_Addition)的测试电路,如图2 所示。其中SerDes_Addition 包括输入输出缓冲单元、复位同步单元、通道配置单元、通道默认配置单元、UART 单元和UART 桥接单元。输入输出缓冲单元由大量的缓冲器构成,被用于解决信号衰弱问题;复位同步单元由触发器构成,以打两拍的形式进行单bit 同步,可实现同步复位异步释放功能,避免产生亚稳态;通道配置单元与通道默认配置单元主要实现对SerDes 各个通道的配置;UART 单元、UART 桥接单元作为PHY 与外界通信的转换模块。

图2 测试电路整体结构

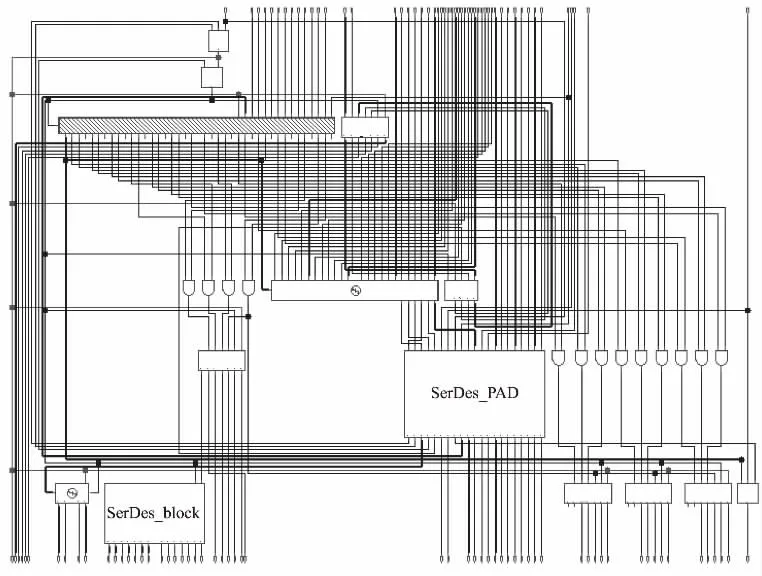

搭建相应模块并与SerDes 进行级联,最后得到的整体电路如图3 所示。

图3 整体电路

4 测试方案验证

4.1 测试电路的前仿验证

前仿验证的测试方案为在依次完成PMA 环回配置、物理编码子层(PCS)环回配置、外环回配置、伪随机序列(PRBS)配置、低频链路层配置等相关配置后,选择PRBS 内建自测试,配置PRBS 产生器开始发送PRBS,PRBS 检测器随之开始检查,首先测试当数据传输正确时PRBS 检测模块是否能够正确地检测,预期检测结果的错误数为0;验证完成后注入错误,观察测试模块是否仍然能够正确地检测,发现注入错误的数量。在此过程中,PRBS 产生器生成的PRBS(在每个周期内PRBS 的数值随机出现,但每个周期的码流完全相同)经过相关配置的选择、转换模块,最终到达PRBS 检测模块。

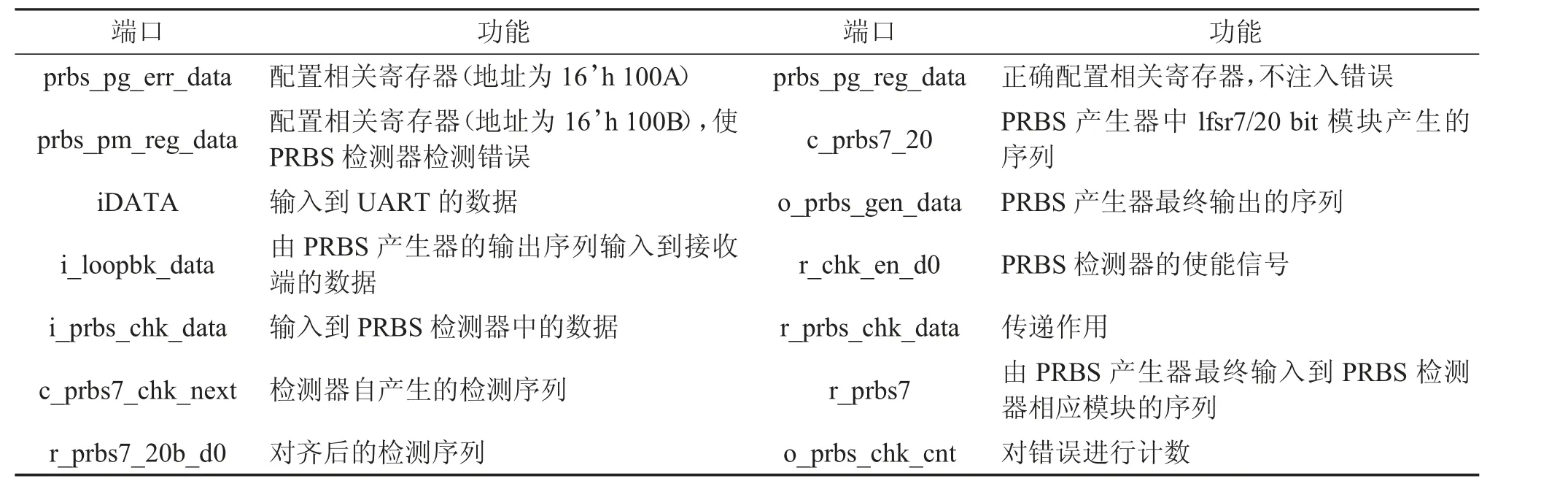

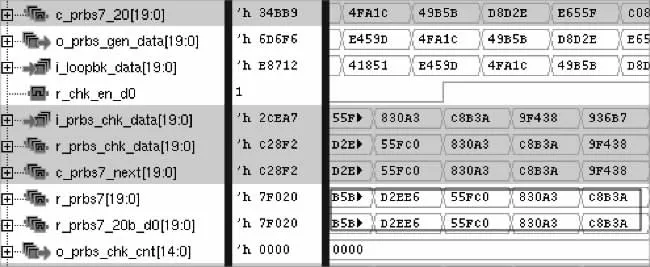

PRBS 检测波形如图4 所示,选择待测SerDes 的工作模式为1.25 Gbit/s、20 bit,配置PRBS 产生器和PRBS 检测器,按照测试方案分别对其端口进行设置,当没有注入错误时,传输到PRBS 检测器的序列与检测器产生的序列一致,r_prbs7(由PRBS 产生器最终输入到PRBS 检测器相应模块的序列)与r_prbs7_20b_d0(对齐后的检测序列)保持一致,所以o_prbs_chk_cnt(错误计数器)显示的计数一直为0,该过程涉及到的端口及其功能如表1 所示。

表1 相关端口及其功能

图4 PRBS 检测波形

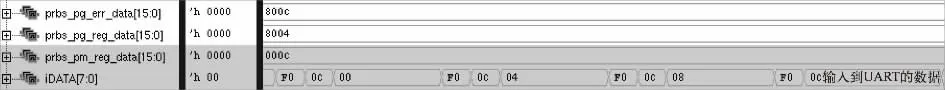

设置PRBS 产生器注入错误,图5 为注入错误后的检测波形图。可以看出,当注入错误时,传输到PRBS 检测器的序列与检测器产生的序列不一致,该过程涉及到的端口及其功能见表1。

图5 注入错误后的检测波形

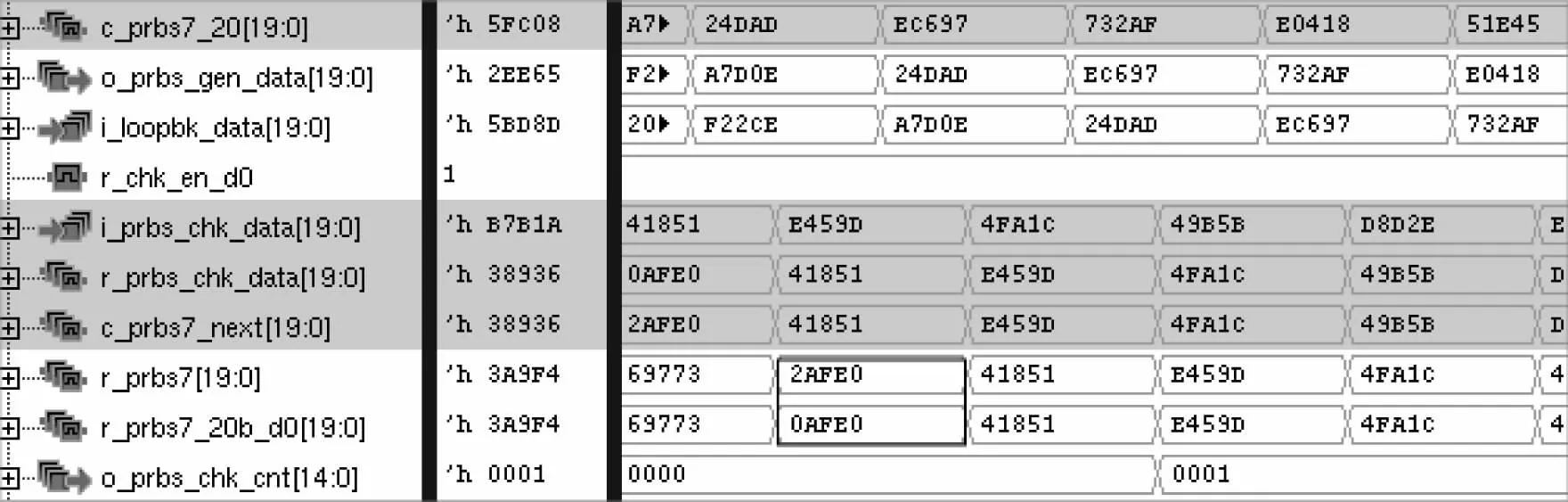

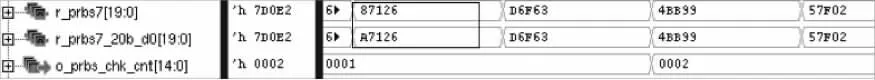

图6 为错误1 的伪随机序列检测波形图,当r_prbs7 为20’h 2AFE0 时,r_prbs7_20b_d0 为20’h 0AFE0,两者不一致,这表示出现了一个错误,此时错误计数器开始计数,显示结果为1;图7 为错误2 的伪随机序列检测波形图,当r_prbs7 为20’h 87126 时,r_prbs7_20b_d0 为20’h A7126,说明再次出现了一个错误,错误计数器的显示结果为2。

图6 错误1 的伪随机序列检测波形

图7 错误2 的伪随机序列检测波形

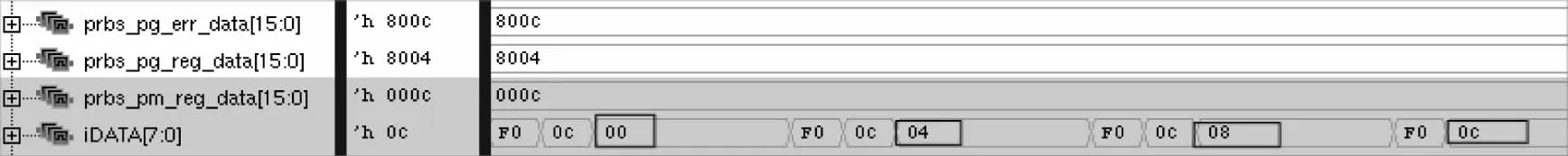

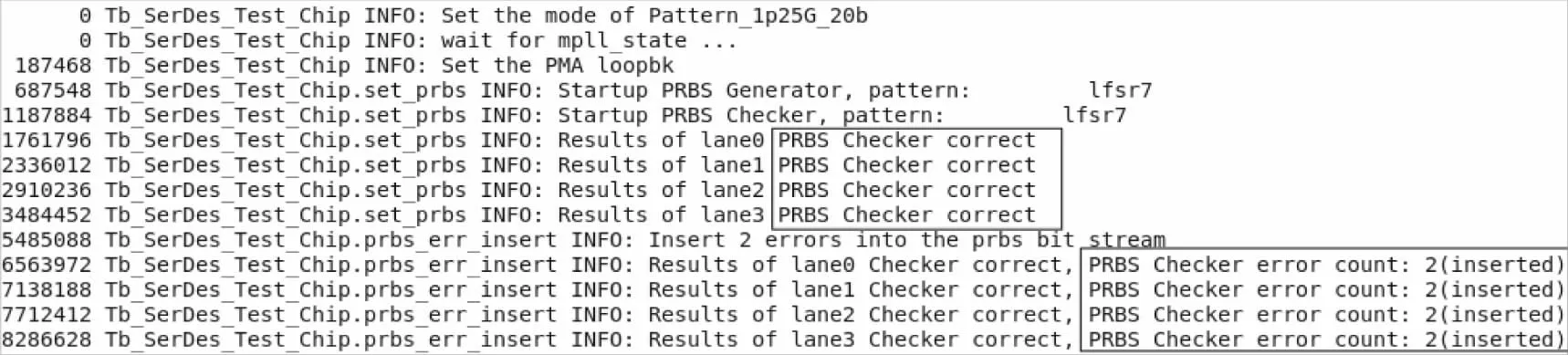

各通道错误数结果如图8 所示,其中16’h 000C、16’h 040C、16’h 080C、16’h 0C0C 分别表示通道0~3通道,共4 条通道。检测报告如图9 所示,测试电路正确地检测出“没有注入错误”和“注入两次单个错误”两种结果,说明在前仿验证中测试电路可以正确地检测出SerDes 是否存在误码。

图8 各通道错误数结果

图9 检测报告

4.2 逻辑综合与静态时序的分析

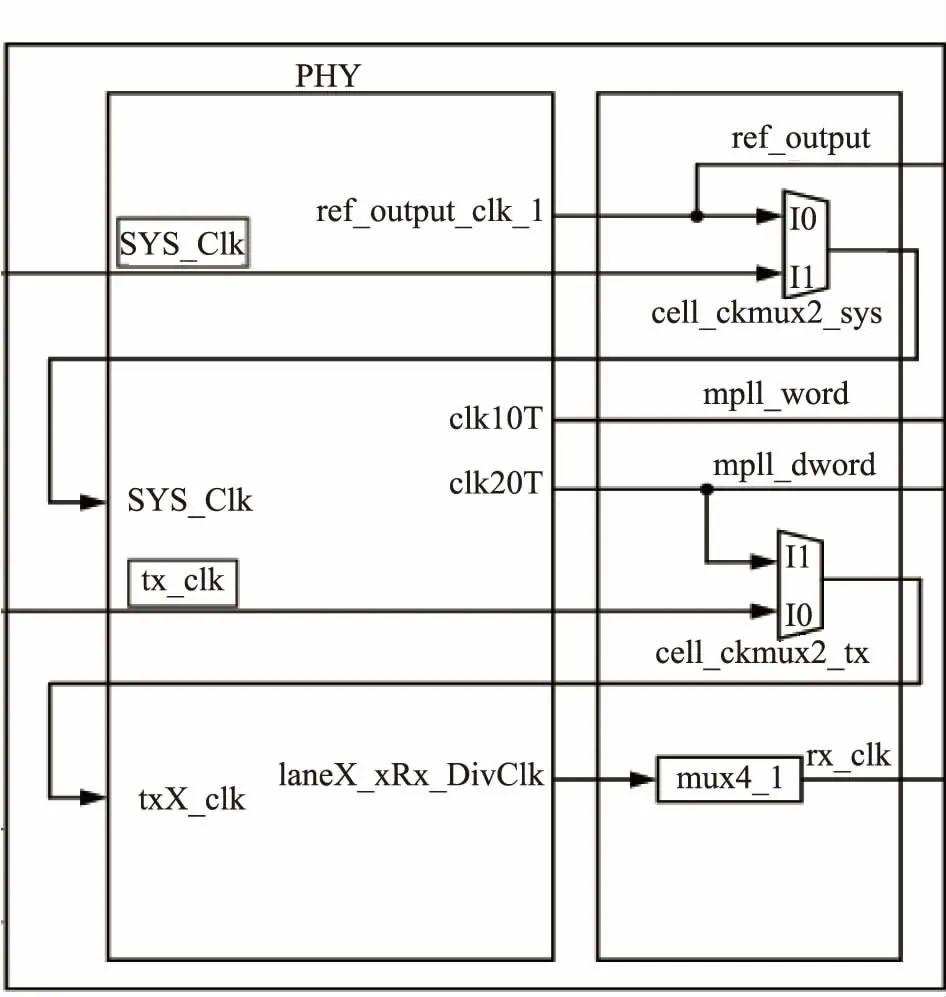

根据测试电路对时钟的要求,写出了时序约束,定义出所有逻辑路径的约束,包括所有输入路径、输出路径、内部(寄存器到寄存器)路径[13],设计出的时钟结构如图10 所示。图10 所示的结构是将PHY 看作一个整体的时钟结构,忽略了PHY 内部的时钟结构,对于PHY 的内部时钟结构,根据导入PHY 的单元库文件将PHY 展平,完整的电路时钟结构(进行后仿验证的电路结构)如图11 所示。将综合后生成的网表与设计的RTL 代码进行功能比较,看结果是否一致[14],通过一致性检查后对电路进行静态时序分析。

图10 测试电路的时钟结构

图11 进行后仿验证的电路结构

4.3 测试电路的后仿验证

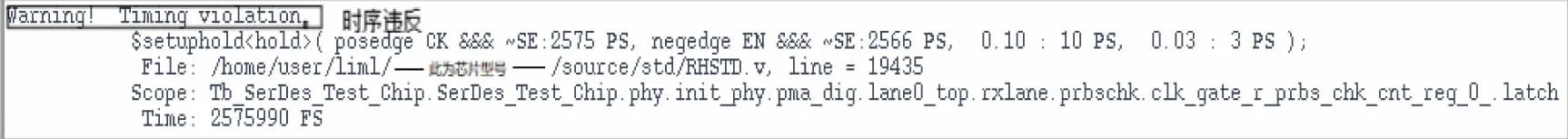

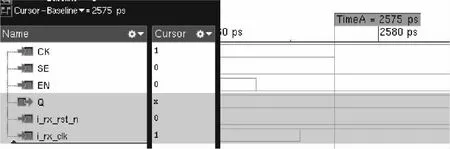

相较于前仿验证,后仿验证具有真实的反标延时,可以采用后端工具产生的标准延迟格式文件对布局布线后的电路门级网表进行时序功能验证,从而达到模拟真实工作中仿真芯片的目的[15]。对完整的电路时钟结构进行后仿验证,在后仿过程中,根据生成报告中的时序违反确定与其相关的寄存器,再根据产生时序违反的具体时间点检查RTL 代码,判断该时序违反是否可以被忽略。后仿时序报告如图12 所示,在2 575 ps 时产生了时序违反,其余时序未发现错误。根据报告信息确定寄存器位置,由寄存器RTL 代码与端口的波形图(见图13)可以判断,在2 575 ps 时,时钟端(i_rx_clk)不处于上升沿,同时复位端(i_rx_rst_n)数据一直为0,未发生变化,表明此时产生的时序违反不会对后续数据产生影响,可以将其忽略。后仿报告表明时序功能正常,测试电路可以正确地测试出SerDes是否存在误码,验证测试方案可行。

图12 后仿时序违反报告

图13 时序违反波形图

5 结论

在1.25 Gbit/s、20 bit 的工作模式下完成了对SerDes 芯片误码率的测试,测试结果符合预期,为SerDes 芯片的测试提供了一种新的解决方案。与传统测试方案相比,本文利用SerDes 芯片的环回模式快速定位故障点,通过引入UART 模块作为PHY 与外界通信的转换模块,实现了对SerDes 芯片参数的动态调试,同时降低了对测试设备通道和速度的要求,减少了为进行SerDes 芯片测试配置的引脚,从而减少了SerDes 芯片测试的复杂度与测试时间周期,进而降低了流片的成本,具有较强的通用性。本文所介绍的测试流程提高了SerDes 芯片测试的可靠性,使测试结果更加准确,为芯片最终的流片成功提供了保障。