数字隔离器的失效分析及解决对策

2023-10-25傅铮翔李飞

傅铮翔,李飞

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

1 引言

隔离电路具有消除不同接地环路噪声、实现中低频信号电平转换等功能,按照隔离原理可分为光电耦合隔离、电感式隔离、脉冲调制变压器隔离、射频调制变压器隔离、电容耦合隔离及数字隔离[1-3]。数字隔离芯片主要用来实现各系统元件间数字信号或者开关量信号的隔离,具有体积小、成本低及外围电路简单等优点,广泛应用在军用电子系统和航空航天电子系统中[4-5]。作为电子系统数据传输的主要载体芯片,数字隔离电路的稳定运行决定了系统的稳定性。当隔离电路失效时,运用失效分析技术对失效问题进行分析并改善,可以提高产品可靠性。失效分析是根据失效现象,通过建立故障分析树对失效原因和失效机理进行定位分析的技术[6]。

某用户采用某型号隔离电路作为信号隔离器,其中一块板卡在上电时隔离电路数据无法传输且输出侧出现高电平异常现象,在运行一段时间后数据传输恢复正常。本文基于该用户反馈的异常问题,建立故障分析树,通过分析失效机理并结合试验验证,定位失效具体原因为带隙基准异常,为同类产品的失效分析和设计优化提供了参考思路和理论支撑。

2 失效原因分析

该隔离器是一种磁性数字信号隔离器,能够实现同向四通道的输入、输出端口间具备额定1 000 V 交流有效值(均方根)隔离电压,同时保证25 Mbit/s 范围内不归零(NRZ)数字信号的正常传输。器件采用塑料隔离封装键合设计,图1 为隔离电路功能框图。应用时,VDD1A 和VDD1B 连接在一起,作为VDD1;VDD2A 和VDD2B 连接在一起,作为VDD2;符号相同的其他端口均连在一起。电路包括编码芯片、变压器芯片和解码芯片三颗芯片。编码芯片将A、B、C、D 4个通道的输入端口信号编码为单、双脉冲,编码信号经过变压器芯片耦合后,由解码芯片将耦合后的脉冲信号解码还原。VDD1 直接给编码芯片供电,VDD2 通过内部LDO 给解码芯片输入级供电。当VDD2 在3.0~5.5 V 变化时,LDO 输出2.6 V 的固定电压,给解码芯片4 个通道的输入级供电,解码芯片其他电路仍由VDD2 供电。

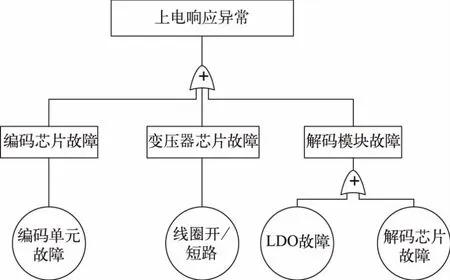

由于输入信号在传输过程中需要经过编码芯片、变压器芯片、LDO 及解码芯片,其中任一电路出现故障将直接导致输出异常。根据问题现象和排查结果,将故障树顶事件设置为电路“上电响应异常”,上电响应异常故障分析树如图2 所示,对各分支进行分析排查。

图2 上电响应异常故障分析树

2.1 编码芯片故障排查

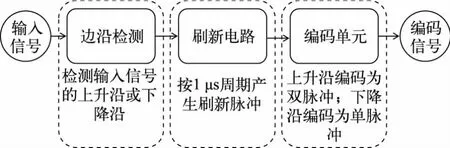

编码芯片内部工作原理如图3 所示,包括边沿检测、刷新电路和编码单元。由于编码芯片由数字组合逻辑构成,一旦出现故障,异常现象将一直存在,与用户现场发现的工作一段时间后恢复正常的现象不一致,故编码芯片故障可以排除。

图3 编码芯片内部工作原理

2.2 变压器故障排查

变压器芯片为无源器件,因用户现场调试中未作任何改变,异常电路在一段时间后工作正常,说明变压器的初、次级线圈不存在开路或短路的情况,变压器芯片故障可以排除。

2.3 解码模块故障排查

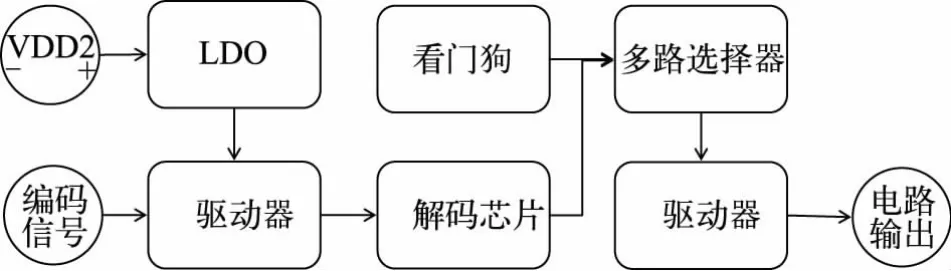

解码模块内部工作原理如图4 所示,包括信号传输通路和故障保护通路两条路径,多路选择器(MUX)二选一后输出解码信号。

图4 解码模块内部工作原理

如果超过了看门狗(WDT)计时周期,故障保护通路有效,电路输出高电平,与异常电路在用户现场一开始输出高电平的现象一致,因此需对LDO 进行进一步排查。

2.3.1 LDO 故障排查

LDO 电路为模拟电路,影响模拟电路正常工作的主要因素包括电压及电流偏置、环境温度和电源上下电快慢程度[7]。因用户使用环境已明确环境温度和电源电压(3.3 V),可以通过改变电源上下电的速度来逐一确认电流偏置(BIAS)、带隙基准(BGR)和误差放大器是否工作正常。经验证,该电路VDD2 上下电斜率为10 V/μs 时,BGR、LDO 测试值接近于设计值,说明此时LDO 工作正常;VDD2 上下电斜率为40 V/s 时,BGR、LDO 测试值均为0,说明此时BGR、LDO 工作异常。

2.3.2 解码芯片故障排查

通过聚焦离子束(FIB)将LDO 旁路,即由VDD2直接给解码芯片输入级供电,其他不变。在VDD2 上下电斜率分别为40 V/s、10 V/μs 两种情况下,输出均能正常响应,由此可以推断,解码电路没有问题。

2.4 失效分析定位

经以上排查,明确失效原因为LDO 工作异常,进而使得编码信号无法继续传输,触发故障保护通路使能,最终输出高电平。

3 机理分析

3.1 BGR 电路

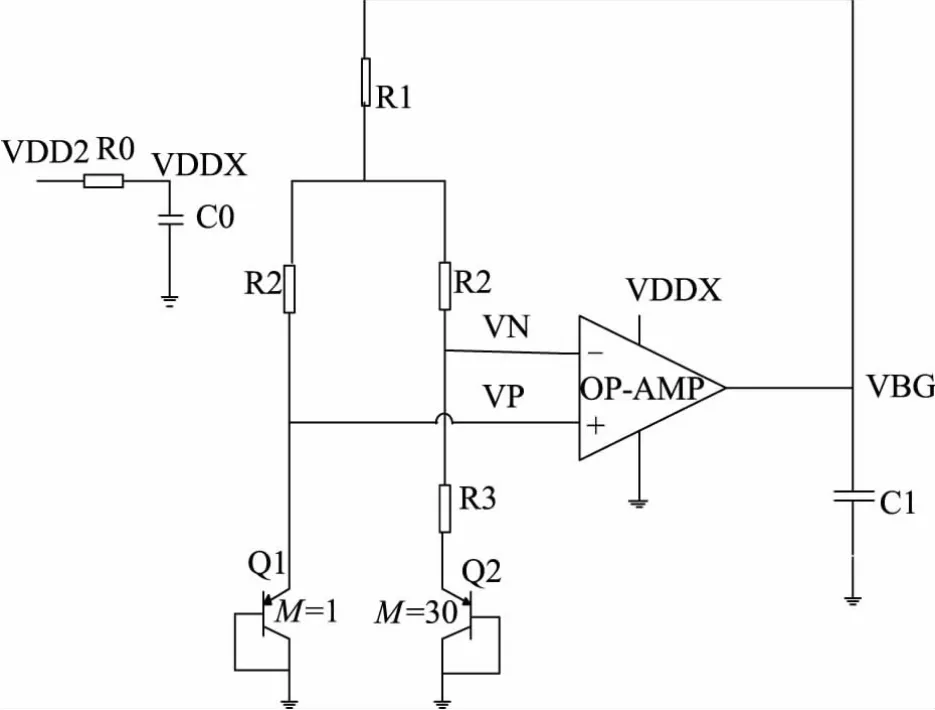

BGR 电路原理如图5 所示,将一个负温度系数的电压(三极管的基极-发射极电压VBE)和一个正温度系数的电压(两个工作在不同密度下的三极管的基极-发射极电压之差ΔVBE)以适当的权重相加,得到一个零温度系数的电压。图中M表示晶体管数量。

图5 BGR 电路原理

由图5 可推导出BGR 输出表达式为

其中VBE2为Q2 的基极-发射极电压,VT为热电压。

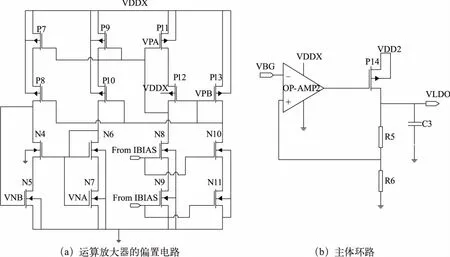

LDO 电路原理如图6 所示,图6(a)为LDO 中运算放大器的偏置电路,由BIAS 电路产生,图6(b)为主体环路。LDO 输出电压的表达式为

图6 LDO 电路原理

由式(1)(2)可知,LDO 输出与BGR 输出成正比,即如果BGR 输出异常,将直接导致LDO 输出异常,这与异常电路在VDD2 上下电斜率为40 V/s 时BGR、LDO 扎针测试为0 的结果相符合。

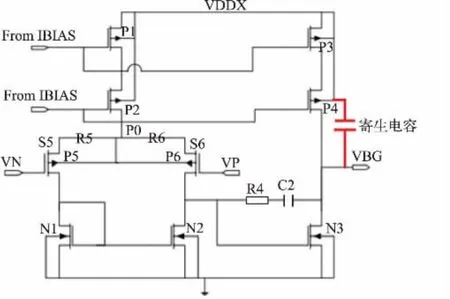

3.2 运放OP-AMP 预置失调电压结构

本电路采用在运放差分对预置失调电压的方式,通过在版图上对差分对管源端进行特殊布局设计来实现,BGR 运放电路结构如图7 所示。

图7 BGR 运放电路结构

3.3 失配模型仿真分析

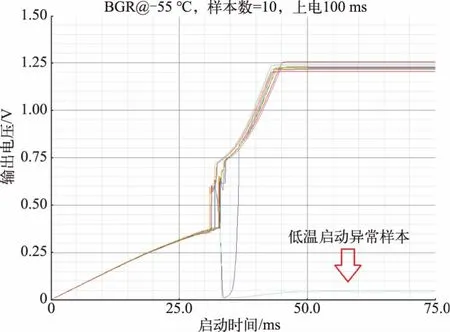

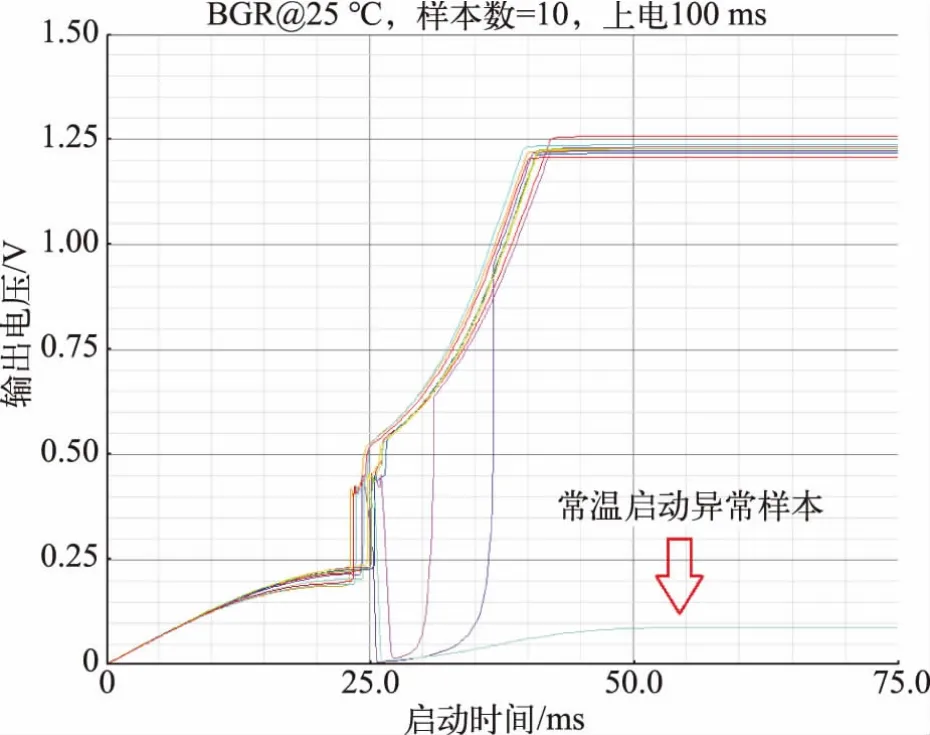

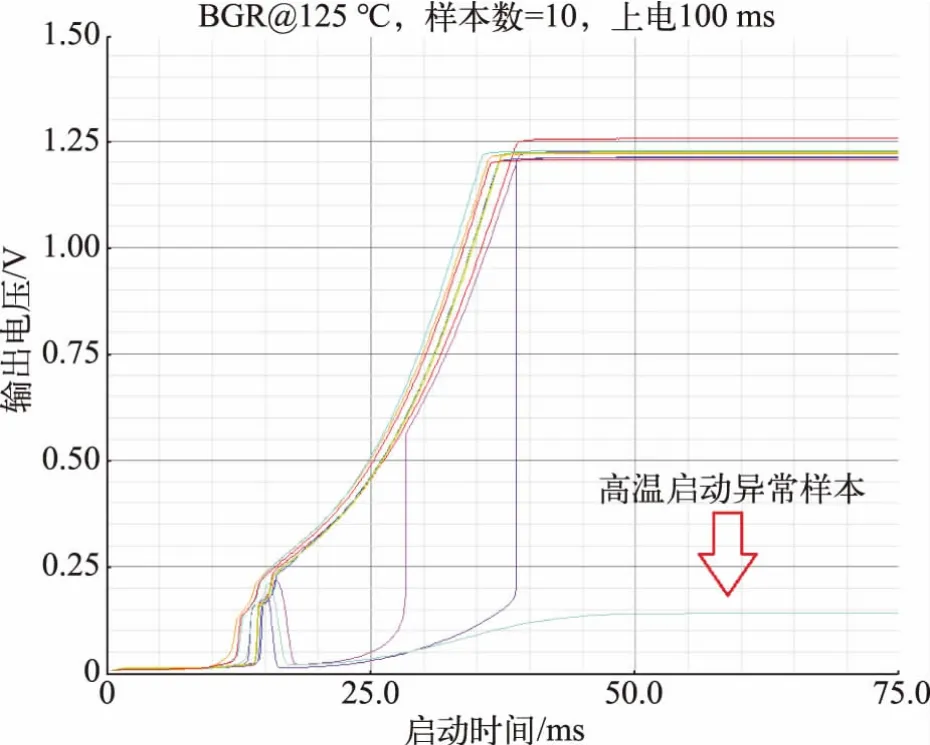

采用厂家提供的三极管及MOS 管的工艺及失配模型,选取10 个样本分别仿真VDD2 上电100 ms 后稳定在3.3 V 的情况,结果如图8~10 所示。

图8 BGR 低温波形

图9 BGR 常温波形

图10 BGR 高温波形

由图8~10 可以看出,在VDD2 上电时间较长时,有一个样本先在低温、常温出现异常,后在低温、常温、高温下均出现异常,说明高温能够改善器件在慢速上电时的响应能力,低温是最恶劣的环境条件。

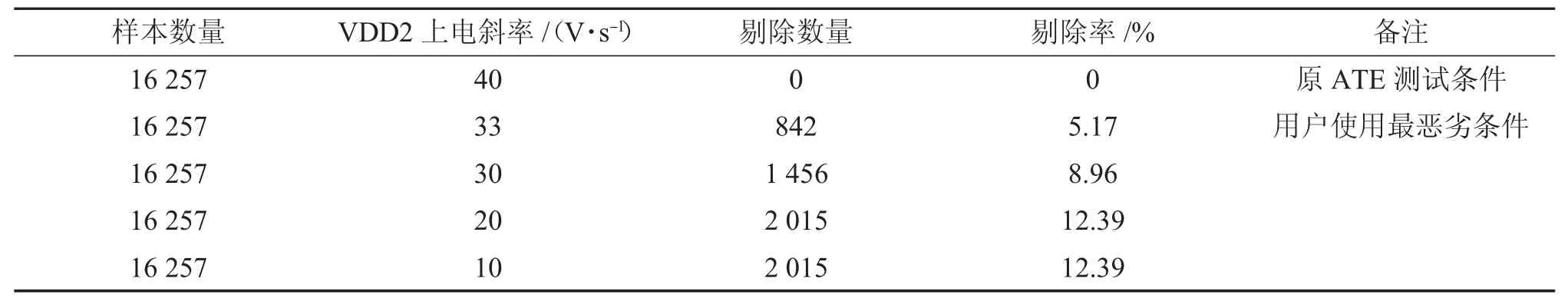

4 失效解决方案

由以上分析及板级验证可知,在使用条件和环境确定的情况下,异常电路的输出只与电源VDD2 上电斜率有关。因此,可通过改变VDD2 上电斜率,以剔除不符合使用要求的电路。VDD2 不同上电斜率的ATE测试失效剔除情况如表1 所示,经测试验证,VDD2 上电斜率在20 V/s 时已可完全剔除存在偏差的电路。最终选择VDD2 上电斜率为10 V/s 的功能测试码,相比用户板级最恶劣的33 V/s 的上电斜率已有足够余量,确保加严测试后的电路满足用户使用需求。

表1 VDD2 不同上电斜率的ATE 测试失效剔除情况

5 结论

针对某型号隔离器在电源上电初期出现响应异常的问题,通过搭建内部电路的BGR 及误差放大器输出关键节点扎针测试平台、进行ATE 上电斜率测试并采用上电仿真等手段多维度复现失效现场,验证失效机理。

经过机理分析及板级验证,故障原因在于个别电路存在制造工艺偏差,导致BGR 不能正确建立,进而在VDD2 上电初期误触发内部故障保护电路,使得电路输出信号一直保持高电平。该类失效可通过加严控制VDD2 上电斜率的方式,并通过ATE 测试进行有效剔除。

本文对某型号隔离器的LDO 失效进行了充分论证,并通过实际板级测试验证了失效机理,为之后的电路改版及同类电路设计提供了理论及事实依据。