一种用于CPLD 擦写寿命验证的设计

2023-10-25顾小明肖培磊唐勇

顾小明,肖培磊,唐勇

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

1 引言

当前常见的复杂可编程逻辑器件(CPLD)在配置数据存储及加载功能设计时一般采用Flash 加SRAM架构[1]。内嵌的Flash 存储器存放配置数据,SRAM 单元与实际的配置点对应。通过联合测试工作组(JTAG)接口将配置数据事先存储在Flash 中,在器件每次加电后,利用内部在线系统编程(ISP)功能[2]将配置数据加载到SRAM 中,从而实现配置数据掉电后不丢失及加电后自动加载的功能。

JTAG 接口、内嵌式Flash 存储器、分布式SRAM存储器及ISP 功能模块构成了CPLD 配置数据擦除、写入及加载的基本机制,是CPLD 能否实现预先设计逻辑的重要保障。本文设计了一种用于CPLD 擦写寿命验证的装置,在产品筛选、考核阶段,对配置数据擦写、加载机制以及内部存储器寿命进行了充分验证。

2 擦写寿命验证装置方案设计

2.1 几种擦写寿命验证方式对比分析

JTAG 负责制定IEEE Std 1149.1 标准,用于芯片内部测试。该标准包含测试接入口(TAP)和边界扫描机制两个基本部分,两部分合在一起又被称作JTAG接口[3]。器件厂商会对标准的JTAG 接口功能进行扩展以满足在线调试及数据配置需求。不同的器件厂商扩展的机制不一样,因此不同厂商提供的配置工具和在线调试软件也不通用。通过JTAG 接口,有两种常见方式可以对CPLD 擦写寿命进行验证。

方式一,使用CPLD 集成开发环境,一般选择后缀名为jed 的配置文件。这种方式对开发工具有严重的依赖性,因为需要解析jed 配置文件后才能控制JTAG接口;虽然支持JTAG 接口的器件可以串行连接成“菊花链”的形式,但是链上器件数量有严格限制,且不能做到多个器件同时配置。

方式二,通过自动化测试机台对CPLD 进行擦写寿命验证。自动化测试机台使用后缀名为svf 的配置文件[4-5],其内容包含了配置过程的擦除、写入及校验。svf 是IEEE Std 1149.1 的一部分,便于自动化测试机台控制JTAG 接口收发数据。svf 类型文件可以通过开发工具由对应的jed 类型文件转换获得。

为提高效率,一般在一块测试板上放置多个CPLD,自动化测试机台通过JTAG 接口对这些器件进行分时测试验证。CPLD 可以在测试板上按照特定的方式连接在一起,既可以保证每个器件的可测性又不会相互影响。客观来说,CPLD 擦写寿命验证装置可以由自动化测试机台来协助完成,但是这种方式有两个明显的弊端:自动化测试机台一般价格昂贵,需要在恒定的湿度、温度环境下运行;需要设计和自动化测试机台对接的专用板卡,且由于自动化测试机台资源有限,很难进行大规模工位扩展。

上述两种CPLD 擦写寿命验证方式均有明显的弊端,不利于多工位同时进行验证,效率低。本设计的思路是进一步提炼、整理svf 类型配置文件,得到配置码并存储在验证装置中,之后可以不依赖开发工具及自动化测试机台进行独立工作。可以根据需要制作多套擦写验证装置,让它们并行工作,提高效率。

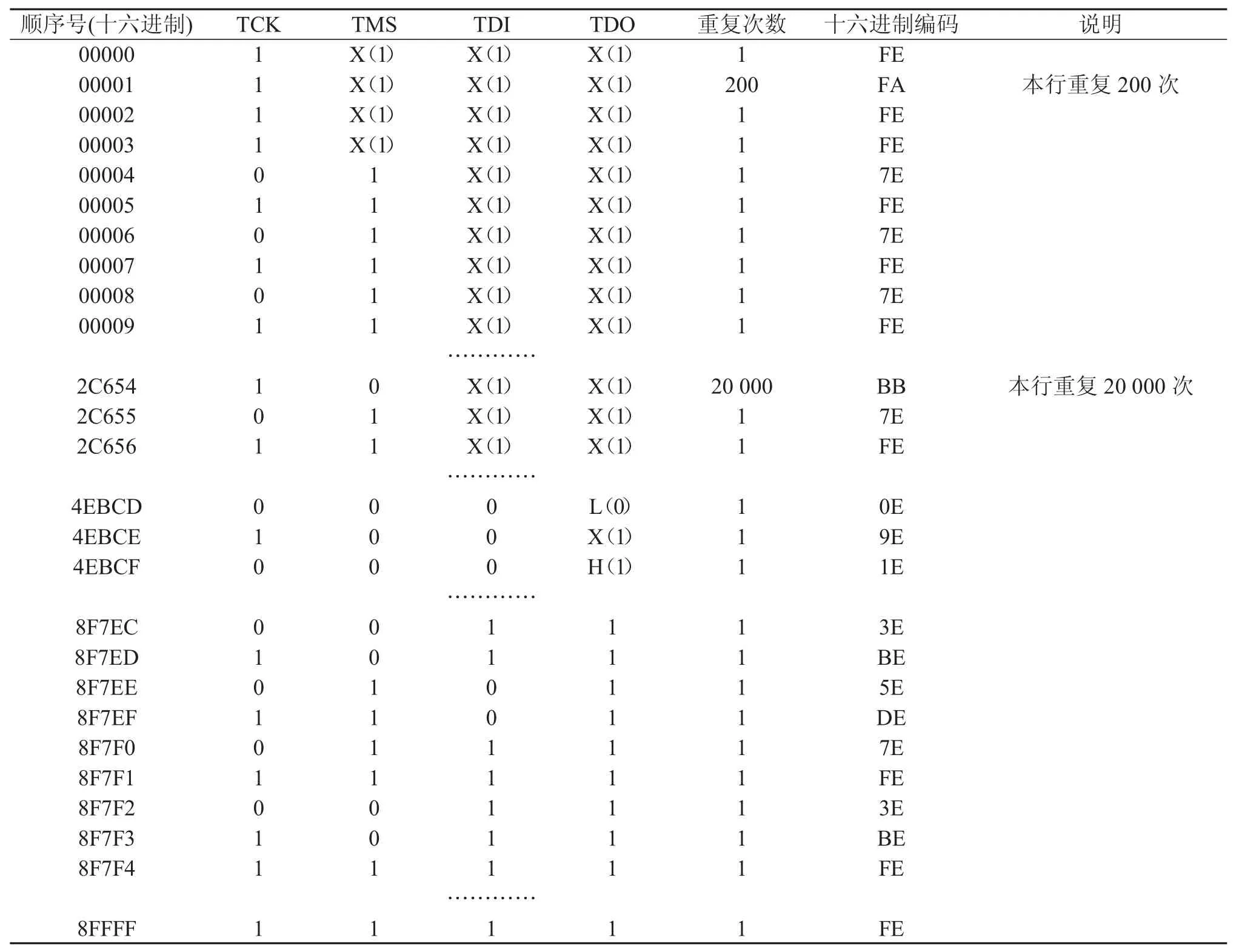

2.2 配置码格式

在svf 类型配置文件中明确列出了JTAG 接口功能引脚(TMS、TCK、TDI 及TDO)的顺序变化关系,但是不能直接存储,因为svf 类型配置文件中存在许多特定意义的字符串。本文采用自行编写的工具软件[6-9],将svf 类型配置文件进一步解析、提炼,去掉多余的字符串,最终只保留JTAG 接口功能引脚应具有的顺序变化关系。示例性顺序配置码如表1 所示,对于不需要的状态(X)一律按高电平(“1”)来编码,这样处理与选择的存储器类型有关。本设计采用的是Flash 型存储器,当对Flash 存储单元擦除后,其默认值是逻辑“1”。

表1 示例性顺序配置码

用一个8 位的二进制码表示JTAG 接口功能引脚特定时刻的状态,Bit7 代表TCK 状态,Bit6 代表TMS状态,Bit5 代表TDI 状态,Bit4 代表TDO 状态,低位Bit3 到Bit0 用于指示本状态需要重复的次数,对应到实际时序为等待时间。对svf 类型配置文件解析后,发现需要重复的状态小于15 种,因此用一个4 位的二进制数对其进行编码。重复次数编码是人为规定的,比如用“E”代表本状态不需要重复,“A”代表本状态需要重复200 次等。这样的一串8 位顺序配置码包含了对CPLD 进行擦写操作的所有信息,是在擦写过程中JTAG 接口功能引脚应该具有的实际高/低电平顺序变化关系。

对于不同逻辑功能的配置码,其长度可能不一致,但最终都会用十六进制编码FE(HEX)补齐到8FFFF(HEX)长度,以保证不同的配置码存储深度一样,便于后续控制逻辑设计。

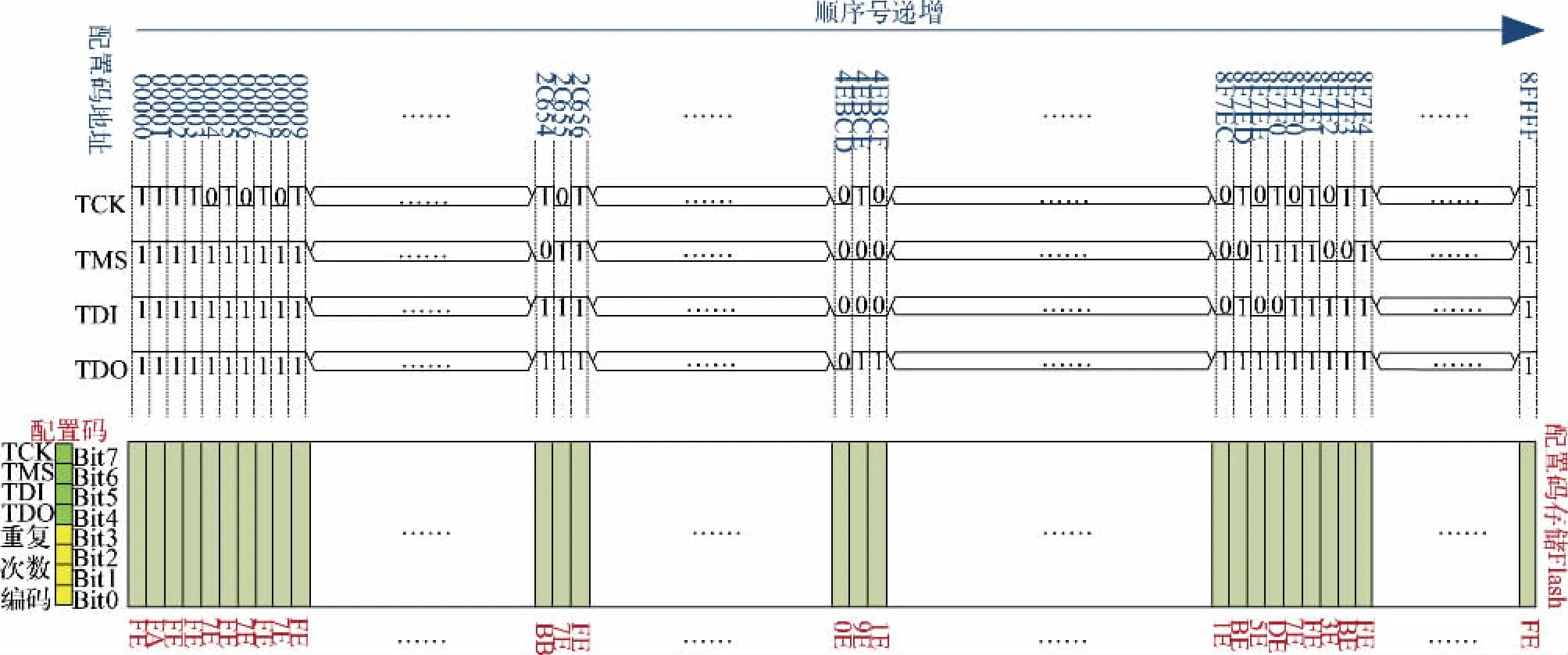

2.3 擦写寿命验证装置的工作原理

擦写寿命验证装置的工作原理如图1 所示。首先,将准备好的一组配置码顺序存储在Flash 单元中;然后,按照一定的速率、顺序每次读取一个配置码,对配置码进行简单解析,将配置码的Bit7 对应到需要擦写的CPLD 功能引脚TCK,Bit6 对应到功能引脚TMS,Bit5 对应到功能引脚TDI,Bit4 对应到功能引脚TDO,通过判断配置码Bit3 到Bit0 的数值决定本次状态是否需要重复(时序等待)。顺序读取、解析完一组配置码,即完成对CPLD 的一次擦写操作。

图1 擦写寿命验证装置工作原理

选取大容量的Flash 存储器,对其存储空间进行合理规划,可以预先存储多组不同的配置码;多组不同的配置码存储块之间插入一定数量的空白存储单元,在对CPLD 进行擦写操作时,只需要从Flash 存储器起始地址开始,顺序读取、解析数据就可以实现不同配置码的交替擦写操作。当最后一组配置码读取、解析结束后,再次回到存储单元的起始地址即可实现多组配置码交替循环擦写操作。

CPLD 擦写寿命验证装置硬件结构如图2 所示,它主要由配置码存储Flash 及一块主控FPGA 构成。通过FPGA 扩展CPLD 的JTAG 接口可以进行多片CPLD 的同时擦写操作。本装置由于所选主控FPGA资源有限,最终一套装置可支持14 片CPLD 同时进行擦写操作。

图2 擦写寿命验证装置硬件结构

配置码存储Flash 可以存储多组不同功能的配置码,本方案根据需求存储了两组配置码,用于交替循环擦写验证。主控时序由一片FPGA 完成。FPGA 外部硬件结构见图2,通过SPI 接口连接Flash 存储器;利用通用I/O 端口扩展CPLD 的JTAG 接口,实现多工位并行擦写。

3 控制逻辑设计

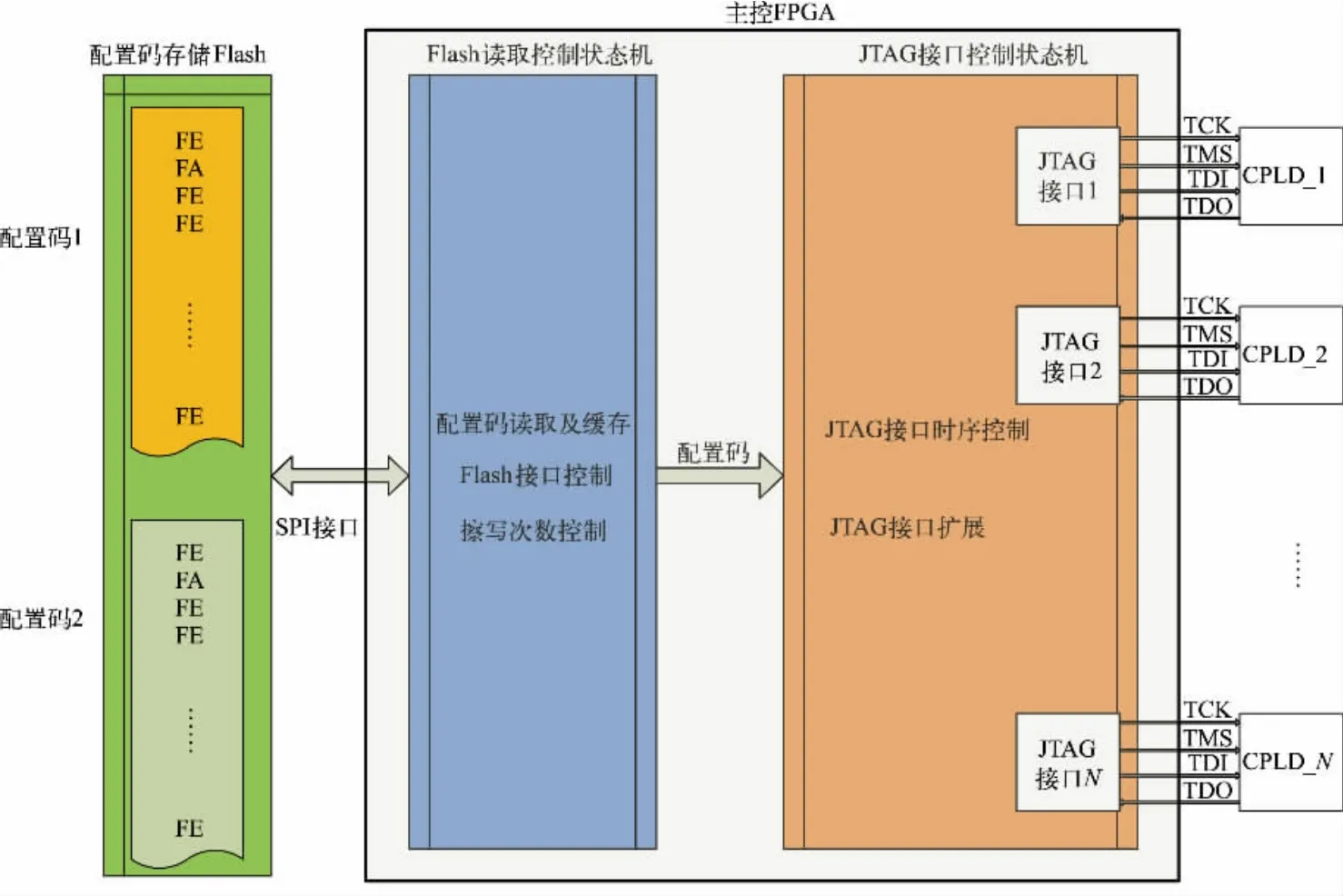

3.1 主控制逻辑设计

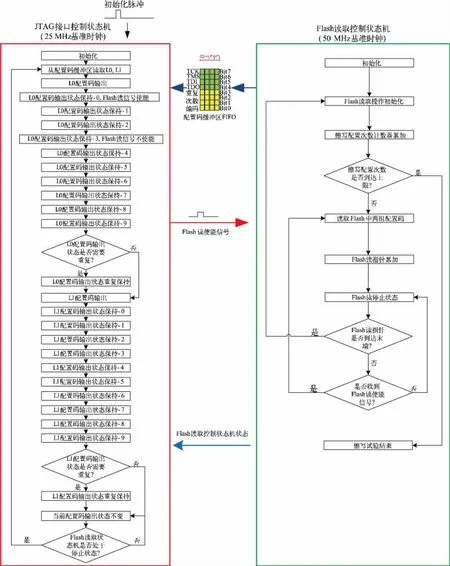

控制逻辑结构及流程如图3 所示。主控FPGA 内部逻辑由Flash 读取控制状态机、JTAG 接口控制状态机及交互机制[10-12]构成。

图3 控制逻辑结构及流程

Flash 读取控制状态机采用50 MHz 高速基准时钟,主要读取Flash 中的配置码,控制擦写次数;JTAG接口控制状态机负责解析配置码,控制CPLD 的JTAG 接口时序,完成实际的擦写操作。两个状态机通过配置码缓冲区、Flash 读使能信号及Flash 读取控制状态机状态信号进行交互以实现协调运行。

当主控FPGA 加电后,JTAG 接口控制状态机首先收到一个初始化脉冲,初始化后向Flash 读取控制状态机输出Flash 读不使能信号,然后从配置码缓冲区读取两组配置码L0 及L1,并对配置码进行解析、输出,同时发出Flash 读使能信号;Flash 读取控制状态机收到Flash 读使能信号后从Flash 存储器中读取两组配置码放到配置码缓冲区,配置码缓冲区设计成先进先出(FIFO)机制,L0 及L1 被L2 及L3 代替,L2 及L3被最新读出的配置码代替;之后Flash 读取控制状态机进入“Flash 读停止状态”。JTAG 接口控制状态机将L1 配置码解析、输出完毕后会判断Flash 读取控制状态机是否已经进入“Flash 读停止状态”,如果是,说明最新的配置码已经准备就绪,JTAG 接口控制状态机读取最新的配置码并解析、输出,同时再次发出Flash读使能信号,一个新的交互周期开始;否则JTAG 接口控制状态机维持当前状态并一直等待,直到Flash 读取控制状态机进入“Flash 读停止状态”。

Flash 读取控制状态机每次读完两组配置码后,Flash 读指针自动累加,当该指针累加到一定阈值后,Flash 中所有配置码被读取完毕,并完成了一个擦写配置周期,此时需要重新初始化Flash 读操作,擦写配置次数计数器自动累加,开始一个新的配置周期。如果擦写配置次数计数器累加到预先设定值,擦写实验结束。

3.2 CPLD 配置速率控制

JTAG 接口控制状态机采用25 MHz 的基准时钟,每组配置码如果没有额外的重复要求将保持10 个基准时钟周期,TCK 时钟信号需要通过两个配置码(一个高电平,一个低电平)拼接得到,因此,CPLD 的擦写时钟TCK 频率约为1.25 MHz。

实际硬件尺寸较大,从主控制FPGA 出来的信号需要经过长线才能到达CPLD 的JTAG 接口,因此擦写时钟TCK 频率控制在1 MHz 左右。相对较低的速率加上等长线控制可以保证配置过程稳定可靠[13]。

4 实际应用效果

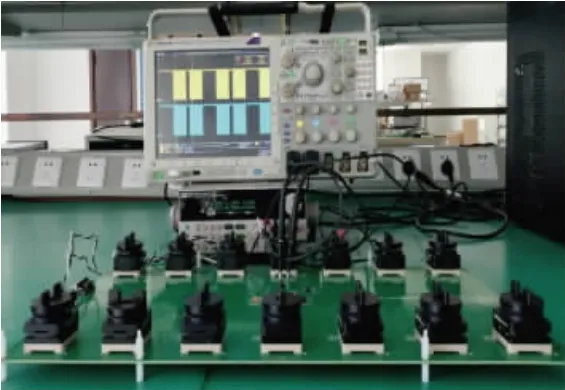

单套擦写验证装置实物如图4 所示,一套装置包含14 个验证工位,所有工位并行工作。可以按照需求制作多套系统以提高CPLD 的筛选效率。

图4 单套擦写验证装置实物

配置时序如图5 所示。图5(a)表明,单组配置码配置时间约为1.5 s,循环配置周期约为4 s。通过控制程序可以自动进行10 000 次的擦写寿命验证,整个过程大约需要5.6 h。从图5(b)中可以看出,TCK 时钟频率为1.137 MHz,与设计值1.25 MHz 接近,只有约10%的误差。

图5 配置时序

与集成开发环境提供的配置机制对比,本装置不具备校验及回读功能,但在一定范围内可以通过控制程序改变TCK 时钟频率。

对同一个功能验证工程文件,分别采用擦写寿命验证装置及集成开发工具对CPLD 进行配置,然后进行功能对比验证,两种配置方式均可以使CPLD 正常工作,逻辑功能一致。

5 结论

本文阐述了一种CPLD 擦写寿命验证装置的设计,主要包括两个关键环节,第一是准备配置码文件,第二是具体方案实现。实际使用效果表明,该装置可用于CPLD 在筛选、考核阶段进行擦写寿命特性验证,且可以根据需要制作多套装置,多套装置并行工作,每套装置内的不同工位并行擦写验证,提高了验证效率。