P-GaN栅结构GaN基HEMT器件研究进展

2023-08-06朱彦旭宋潇萌李建伟谭张杨李锜轩李晋恒

朱彦旭, 宋潇萌, 李建伟, 谭张杨, 李锜轩, 李晋恒

(1.北京工业大学光电子技术教育部重点实验室, 北京 100124;2.中国科学院软件研究所, 北京 100190)

氮化镓(GaN)作为第3代半导体材料,具有禁带宽度大、耐高温高压、电子饱和速度高等诸多优点。GaN基高电子迁移率晶体管(high electron mobility transistor,HEMT)器件通过在异质结处形成高浓度、高迁移率的二维电子气(2-dimensional electron gas, 2DEG)产生导电沟道,从而实现器件的导通。因具备高热导率、低导通电阻、耐受高频高压条件等优良特性,所以近年来GaN基HEMT器件成为高频高功率器件与开关器件领域的研究热点。

在传统的GaN基HEMT器件中,因GaN材料具有强自发极化与压电极化效应,所以往往表现为耗尽型工作模式,即阈值电压为负值,需要额外设计负偏置电压来关闭器件,这对器件的安全运行及简化电路设计十分不利。在电力电子应用领域,增强型器件可避免误开启的风险并降低栅极驱动复杂性,具有更大优势,因此,增强型GaN基HEMT器件成为当前的主要研究方向。目前,实现增强型GaN基HEMT器件的主流技术有:氟(F)离子注入技术、凹槽栅结构、共源共栅级联结构和P-GaN栅结构[1]。相较于前3种方法,P-GaN栅技术可以获得阈值电压稳定、可靠性高且工艺可控性强、重复性好的增强型器件[2],适于投入大规模生产及商业用途,因此,成为当前应用最广泛且最具前景的增强型HEMT器件制备方法。

1 P-GaN栅结构HEMT器件发展需要解决的问题

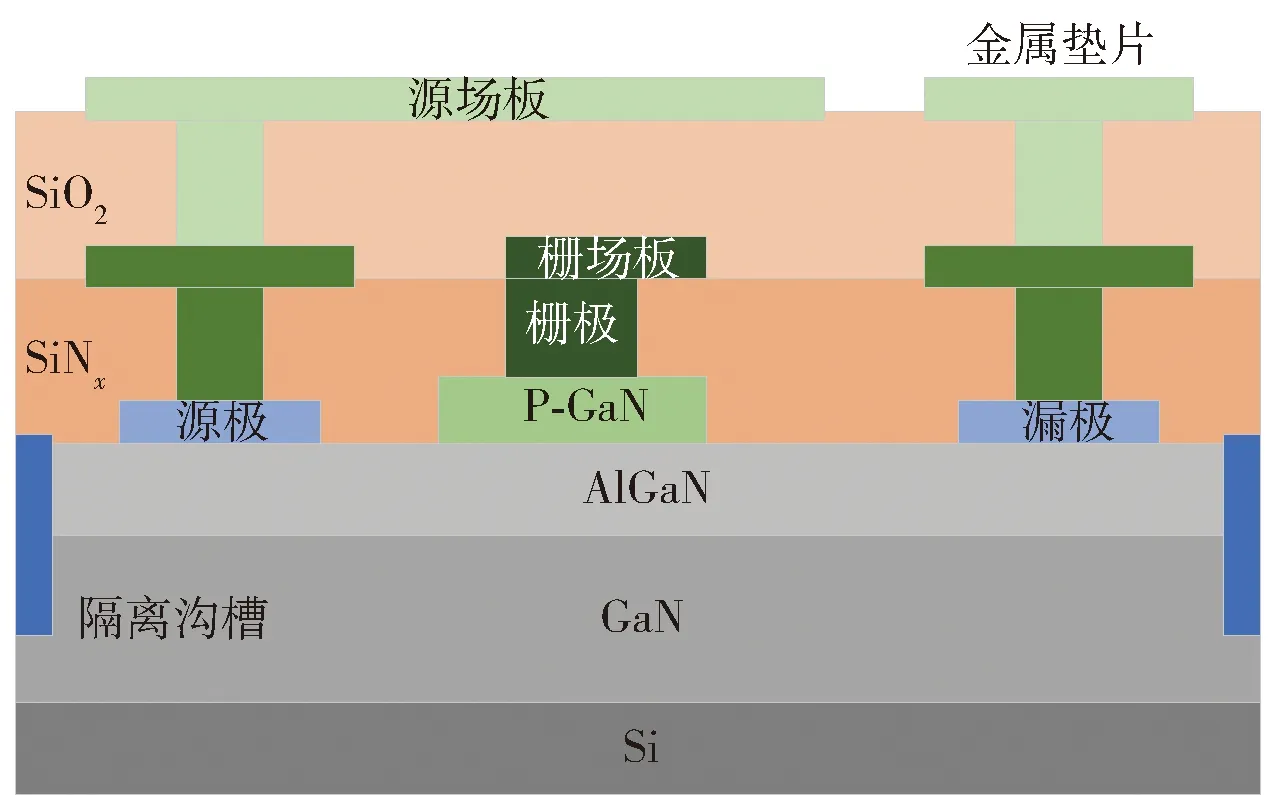

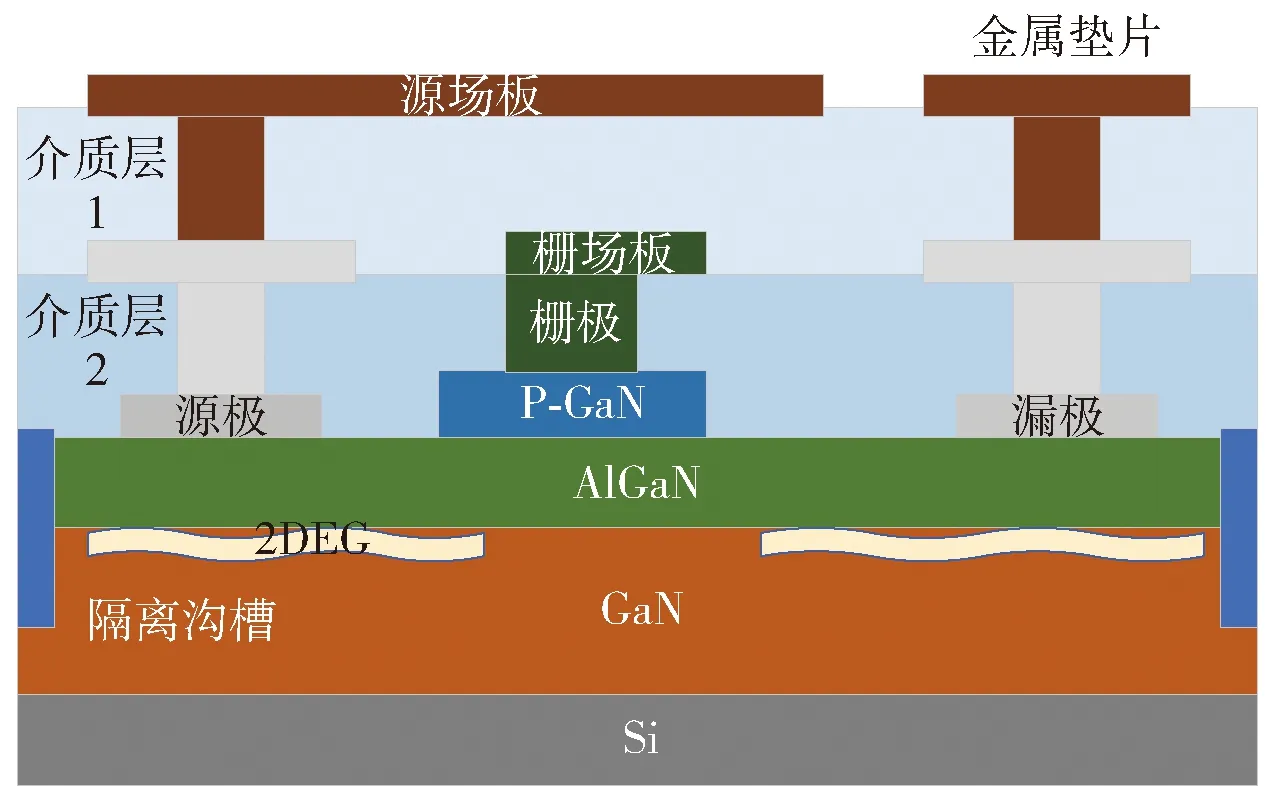

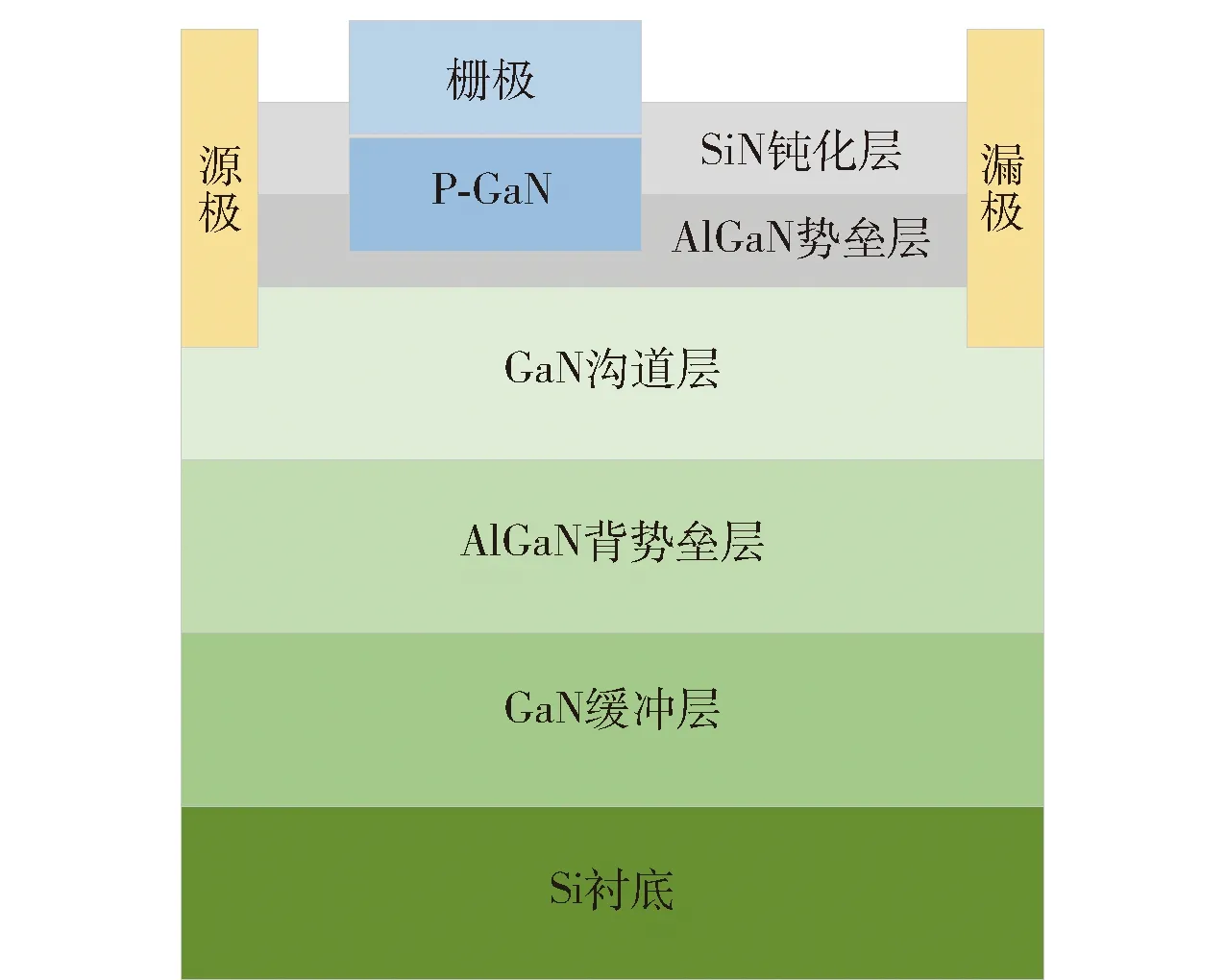

P-GaN栅结构GaN基HEMT器件结构如图1所示,与传统GaN基HEMT器件相比,它在栅极下方与势垒层之间引入了一层P-GaN,该P-GaN帽层可提高AlGaN/GaN异质结界面处的能带,在栅偏压为0 V时,使其高于费米能级,从而耗尽栅极下方区域的二维电子气(2-dimensional electron gas,2DEG),实现常关特性。图2展示了该结构器件的工作原理。图中:EF代表费米能级;Ec代表导带底对应的能级;φB为金属半导体间的势垒高度;d为AlGaN层对应的能带范围长度。

图1 P-GaN栅结构GaN基HEMT器件结构示意Fig.1 Schematic of P-GaN gate structure GaN-based HEMT device

图2 引入P-GaN栅前后GaN基HEMT器件工作原理示意[2]Fig.2 Schematic of working principle of GaN-based HEMT device before and after introducing a P-GaN gate[2]

2000年,Hu等[3]制备了具有P型GaN帽层的GaN基HEMT器件,其阈值电压为2.4 V,这是首个成功制备出的P-GaN栅结构增强型GaN基HEMT器件,它的出现证实了此项技术的可行性,之后便有越来越多的研究人员从事P-GaN栅结构增强型器件的研究,并对该技术进行了不断的改良与优化。目前,仍存在一些问题制约着此项技术的发展,主要的制约因素总结如下。

1.1 Mg激活与扩散问题

为获得P型导电的GaN层,常采用Mg作为掺杂剂对GaN材料进行掺杂,但Mg掺杂剂在GaN中溶解度低,Mg的离化能高[4-6],因此,很难实现足够高的空穴浓度,导致P-GaN层在实际应用中很难完全耗尽栅下的2DEG。同时,高温生长过程中Mg将不可避免地扩散进AlGaN势垒层与GaN沟道层,这些都会极大地阻碍器件阈值电压的提升,损害器件性能,限制其在高压领域中的应用[7]。

2016年,Posthuma等[8]通过优化P-GaN生长条件与Mg的质量分数,获得了阈值电压2.1 V、开启电阻150 mΩ的增强型P-GaN栅结构HEMT器件。此方法在一定程度上改善了Mg扩散问题,提升了Mg激活率,但效果并不显著。目前,针对此问题主要的研究方向在于优化器件栅结构(如引入本征GaN(intrinsic-GaN,i-GaN)复合帽层结构)和改善器件制备工艺(如优化退火条件)。

1.2 P-GaN非栅区域刻蚀问题

非栅区域P-GaN刻蚀是制备P-GaN栅结构HEMT器件最重要的工艺步骤,目前,多采用感应耦合等离子体(inductively coupled plasma,ICP)刻蚀法去除多余的P-GaN。理论上,应当只保留栅极下方区域的P-GaN,但在实际制备过程中,受限于工艺设备精度、操作手法等因素,常常出现势垒层过刻蚀、P-GaN残留、P-GaN侧壁及表面损伤等问题。这些都会导致沟道中2DEG浓度降低,器件栅控能力减弱,并最终影响器件性能。因此,通过优化制备工艺来改善刻蚀效果是十分必要的,这对能否获得性能优良的HEMT器件至关重要。

1.3 P-GaN帽层与栅极接触机制问题

在P-GaN栅结构GaN基HEMT器件中,引入的P-GaN层可以与栅金属形成肖特基接触或欧姆接触。目前,大多数已有报道的器件为肖特基接触模式,在这一接触机制下,栅结构较复杂,相当于由2个背靠背的二极管组成[9],其具体作用机理尚不明晰,而采用欧姆栅电极的器件相关报道较少。因此,有必要进一步探究帽层与栅极间的接触机理,研究2种接触机制下器件的电学特性,这有利于进一步提升器件栅控能力及栅极可靠性。目前,研究的重点集中于栅极材料的选取。

2 P-GaN栅结构HEMT器件的结构优化

以传统的P-GaN栅结构AlGaN/GaN HEMT器件为例,它由Si衬底、AlGaN缓冲层、GaN沟道层、AlxGa1-xN势垒层和源、漏、栅电极以及栅下的P-GaN层组成。对已有的材料层进行诸如厚度、种类、掺杂浓度等结构参数的优化,可以改善器件的性能。下面从材料层结构参数优化角度对近年来的研究进展进行综述。

2.1 材料层结构参数优化

2.1.1 势垒层参数优化

势垒层材料与GaN沟道层形成的异质结是HEMT器件中最重要的结构,因此,对势垒层材料厚度、元素组分、材料种类等参数进行优化十分必要。2019年,南京大学的葛梅[10]探究了AlGaN/GaN HEMT器件中AlGaN势垒层厚度d及Al组分x对器件性能的影响,发现:其他条件一致时,d从10 nm增至20 nm,器件阈值电压从2.3 V降至1.3 V,但最大饱和输出电流IDmax却随之增加,如图3所示;当x从22%增加至24%,器件阈值电压随之减小,从 1.7 V降至1.5 V,而IDmax随x增加而增加。2021年,Huang等[11]也进行了类似的实验,当AlGaN势垒层厚度从10 nm增至30 nm,测得相应阈值电压从2.2 V降低至-0.2 V,IDmax从0.23 A提升到0.52 A。这一变化趋势是由于Al组分的增加可以提高2DEG浓度,但同时将导致势垒层与GaN层间晶格失配加剧,而AlGaN层的厚度过大会引起弛豫现象[12]。

图3 AlGaN势垒层厚度与器件阈值电压和最大输出饱和电流的关系[10]Fig.3 Relationship between AlGaN barrier thickness,threshold voltage and maximum output saturation current[10]

2018年,Chiu等[13]提出了氮化铝(AlN)/Al0.17Ga0.83N/Al0.3Ga0.7N复合势垒层结构,如图4所示。这一复合势垒层结构器件的最大输出电流密度达320 mA/mm,比传统势垒层结构器件提高了17.6%;导通电阻率为5.05 Ω·mm,降低了10.6%。同时,AlN层很好地抑制了反向栅泄漏电流,使其降低了一个数量级,实现了击穿电压从218 V至256 V的提升。

图4 复合势垒层器件结构示意[13]Fig.4 Schematic of the structure of device with composite barrier layers[13]

2021年,为改善传统AlGaN/GaN异质结中存在的晶格失配问题,提高器件可靠性,Huang等[11]采用In0.17Al0.83N作为势垒层,对所制备的器件进行仿真测试,并与传统Al0.2Ga0.8N/GaN HEMT器件对比,发现7 nm厚In0.17Al0.83N势垒层的器件即可获得1.9 V的阈值电压,与30 nm厚Al0.2Ga0.8N势垒层器件达到了近似的水平(2.2 V),同时,具有更低的导通电阻率(5.39 Ω·mm),比AlGaN/GaN HEMT器件降低了23%,饱和输出电流密度提升了161%,达120 mA/mm,截止频率提高了39%,达11.5 GHz。以上现象得益于AlN、InAlN等Ⅲ族氮化物半导体材料的强自发极化与压电极化效应[14-15],将此类材料引入复合势垒层,对提升器件电学特性具有重要意义。

2.1.2 P-GaN帽层参数优化

P-GaN帽层对于整个器件起着十分重要的作用,其中最重要、最值得研究的参数就是空穴掺杂浓度,它直接关系到帽层耗尽2DEG的能力,进而影响器件阈值电压的高低。2017年,Efthymiou等[16]采用与前人实验结果吻合良好的模型研究了P-GaN层掺杂浓度对HEMT器件特性的影响,发现:当掺杂浓度增加时,栅下2DEG强耗尽已形成,其导带会偏离费米能级;当掺杂浓度在一定范围(1×1017~1×1018cm-3)内增加,阈值电压随之增加。

2019年,南京大学的张东[17]也探究了P-GaN帽层空穴浓度对器件性能的影响,在源漏电压VDS=0.5 V、P-GaN层厚度为100 nm时,将帽层空穴浓度从1×1017cm-3增至8×1017cm-3,发现阈值电压随空穴浓度提高而提升,但空穴浓度过高,器件开启时的输出电流有所降低。上述结果表明,高的空穴浓度有利于加强帽层对沟道中2DEG的耗尽作用,但浓度过高则会降低器件开启时的输出电流,因此,P-GaN层掺杂浓度应在合理范围内选取以兼顾阈值电压与输出特性。

2.1.3 栅极材料优化

栅极是P-GaN栅结构HEMT器件中直接与帽层相连的部分,采用何种金属材料制作栅极关系到其与P-GaN之间的接触机制,不同接触机制对器件性能具有直接影响。在已有文献报道中,大多数器件栅极与帽层形成肖特基接触,采用最多的材料为Ni/Au合金、W金属[18-19],但采用欧姆电极的相关报道较少。2017年,Efthymiou等[16]在2×1017cm-3帽层空穴浓度下采用功函数4.50、4.85、5.30 eV的3种金属进行仿真,发现肖特基接触模式下栅金属功函数对器件阈值电压影响较小,但与欧姆电极的器件相比栅摆幅更大。2019年,张东[17]采用Ni/Au金属组合、W金属和欧姆电极,发现肖特基接触模式下的器件阈值电压更高,栅极泄漏电流也较低,但整体输出电流却低于欧姆栅器件。这是因为欧姆接触模式下没有肖特基势垒存在,故栅极漏电现象不可避免,栅极可靠性也因此降低,而在肖特基栅器件中,通过选择功函数小的金属,增大栅金属功函数与帽层材料价带顶的能量差值,即可提高肖特基势垒高度,从而提升阈值电压。

本文归纳总结了P-GaN栅结构HEMT器件在材料层结构参数方面的优化举措,对其特征及优缺点进行了对比,如表1所示。

表1 器件材料层参数优化方法对比

2.2 器件结构优化设计

除了对已有材料层进行结构参数优化,还有许多研究人员通过新结构层(钝化层、场板结构等)引入和提出创新结构,如P-GaN栅结合槽栅、横向耦合栅等,对器件结构进行优化设计,并取得了一定进展。

2.2.1 钝化层结构

钝化层结构可有效抑制GaN基HEMT器件中普遍存在的电流崩塌现象,该技术即在器件表面沉积一层绝缘材料以形成钝化保护层,该层材料种类、厚度等参数都与器件性能息息相关。2016年,Ho等[20]在传统P-GaN帽层AlGaN/GaN HEMT器件上方利用等离子增强化学气相淀积(plasma enhanced chemical vapor deposition,PECVD)方法沉积150 nm的SiO2作为钝化层,与无钝化层的常规器件相比,其归一化动态导通电阻Ron小得多,电流崩塌也得到明显改善,如图5所示。图中VGS为栅源偏置电压。

图5 无SiO2钝化层的器件A与有SiO2钝化层的 器件B的归一化动态导通电阻[20]Fig.5 Normalized dynamic on-resistance of device A without passivation layer and device B with passivation layer[20]

2019年,张东[17]探究了SiO2、SiNx这2种材料钝化层对P-GaN栅结构增强型HEMT器件的影响,发现VDS=0.5 V时两器件均表现为常关特性,阈值电压为0.6 V左右,开关电流比高达109,亚阈值摆幅(subthreshold swing,SS)达70 mV/dec,说明钝化层结构可显著提升栅对沟道的控制能力。与SiO2钝化层器件的最大输出电流密度(227 mA/mm)相比,SiNx钝化层器件的输出电流密度(252 mA/mm)更大,此外,在关态栅漏电压380 V时,SiNx钝化层器件开态电阻更低,仅为静态电阻的1.5倍。2021年,Jiang等[21]在300 ℃条件下采用原子层沉积(atomic layer deposition,ALD)法在P-GaN栅结构HEMT器件上生长了一层40 nm厚的Al2O3钝化层,该器件在VGS=8 V时实现了450 mA/mm的高饱和输出电流密度、3.92 Ω·cm2的低比导通电阻,具有正的阈值电压(1.6 V)和较理想的SS(66 mV/dec),这些优良特性说明相较于PECVD方法沉积的SiNx层,ALD方法沉积的Al2O3钝化层能更好地抑制表面漏电。虽然目前在P-GaN栅结构HEMT器件中关于钝化层结构的研究还不是很多,但就已有结果来看,引入钝化层确实能够有效抑制电流崩塌,并减少表面态[22],提升器件在高压高频条件下的可靠性。

2.2.2 场板结构

场板结构能在抑制电流崩塌的同时大幅提升击穿电压,显著提高器件功率密度、功率附加效率和相关增益,对频率特性亦有改善[23]。近年来,该结构成为GaN基HEMT器件性能优化领域的研究热点。针对P-GaN栅结构HEMT器件,2020年,Hu等[24]提出了由源场板和栅场板组成的双场板结构,如图6所示。该器件获得了超过600 V的击穿电压,饱和电流密度从无场板时的98 mA/mm增至132 mA/mm,阈值电压从3.3 V增至3.7 V,Ron仅比静态值增加50%,展现出对电流崩塌现象的有效遏制,以及对栅附近峰值电场的有效降低和对电场分布的调制作用。

图6 双场板P-GaN栅结构HEMT器件结构示意[24]Fig.6 Schematic of double-field plate P-GaN gate structure HEMT device[24]

2020年,Zeng等[25]在P-GaN栅结构HEMT器件上制备了不同长度的栅场板,发现长度增加时器件泄漏电流随之减小,但超过某一临界长度后泄漏电流增加。随后,分别制备了长1.5 μm栅场板、长3.5 μm源场板及栅源双场板结构的器件(见图7),发现双场板结构对泄漏电流的抑制更显著。由此可见,场板种类、场板长度、场板个数均关系到器件最终性能的好坏,而源漏双场板结构可显著增强对漏电的抑制作用,同时还能修正势垒层中的电场轮廓,但此类结构会对器件微波特性造成损害[23]。

图7 场板结构P-GaN栅结构HEMT器件结构示意[25]Fig.7 Schematic of P-GaN gate structure HEMT device with field-plate structure[25]

2.2.3 栅结构优化设计

合理的栅结构能避免器件短沟道效应、集肤效应等问题,从而获得优良的器件特性,因此,近年来不断有研究人员对栅极结构进行优化设计,也有许多学者提出诸如复合栅、横向耦合栅等新型栅结构。

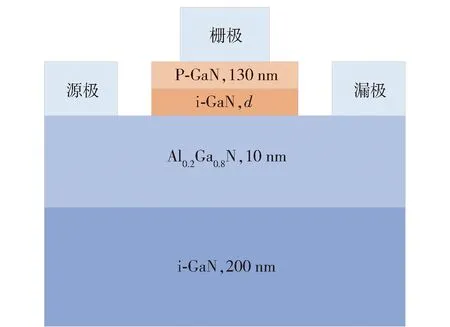

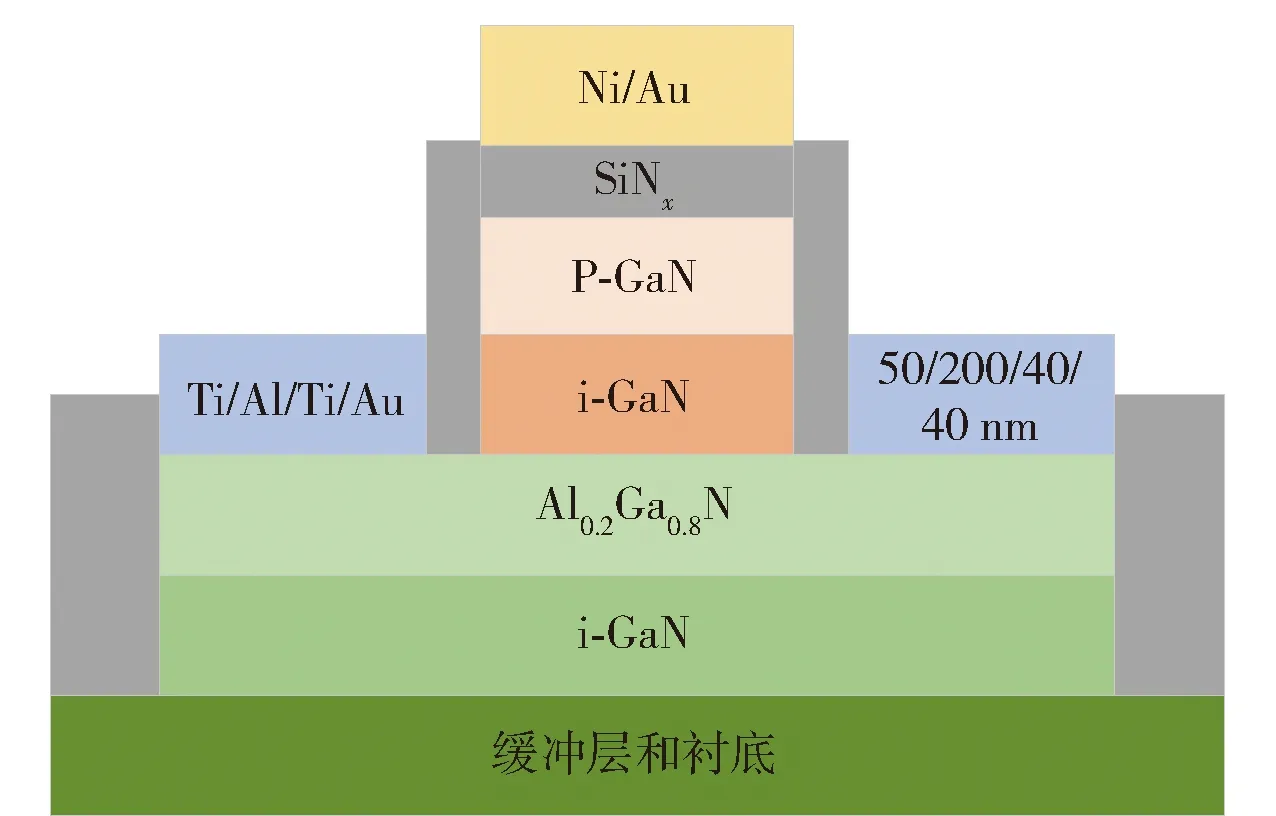

2019年,西安电子科技大学黄倩[26]设计并制备了P-GaN/i-GaN复合栅结构的器件,其基本结构如图8所示,即在传统P-GaN栅结构HEMT器件的栅极与AlGaN势垒层间引入一层厚度为d的 i-GaN。 当P-GaN厚度为130 nm、i-GaN厚度d为 20 nm 时器件取得了正向的阈值电压(0.1 V),此时的峰值迁移率与常规耗尽型P-GaN栅结构HEMT器件相比仅降低5%左右,沟道特性良好,但复合栅结构器件栅漏电较大,阈值电压较低,对此,在栅与复合帽层间插入介质层构成金属-绝缘层-半导体(metal-insulator-semiconductor,MIS)栅结构(见图9),当采取20 nm厚的SiNx栅介质时,器件获得了6.2 V的阈值电压,击穿电压增至26 V,正向栅泄漏电流密度降至10-7mA/mm,在保持器件电流输出能力的同时兼顾了高阈值电压。

图8 P-GaN/i-GaN复合栅HEMT器件结构示意[26]Fig.8 Schematic of HEMT device with P-GaN/i-GaN composite gate[26]

图9 引入SiNx栅介质的MIS栅P-GaN栅结构HEMT器件示意[26]Fig.9 Schematic of MIS gate P-GaN gate structure HEMT device with SiNx dielectric[26]

2020年,乔杰等[27]将P-GaN栅技术结合槽栅技术,同时利用AlGaN/GaN/AlGaN HEMT双异质结结构,设计了P-GaN栅结合槽栅的双异质结HEMT器件,如图10所示。采用Sentaurus TCAD软件对器件仿真模拟,当P-GaN厚100 nm、槽栅深度13 nm时器件获得了3.4 V的阈值电压,比传统结构器件提升近7倍。改变槽栅刻蚀深度,观察到器件最低导通电阻率11.3 Ω·mm,最大饱和电流密度1.85×105mA/mm,击穿电压最高达734 V。针对这一新型结构,后续可改变槽栅的形状、面积、刻蚀深度,并优化刻蚀条件,进一步探究这些因素对器件电学特性的作用效果和作用机制,力求获得阈值电压、导通电阻和器件耐压间的最优折中。

图10 P-GaN栅结合槽栅的双异质结HEMT器件结构示意[27]Fig.10 Schematic of P-GaN gate double heterojunction HEMT device combined with recessed-gate[27]

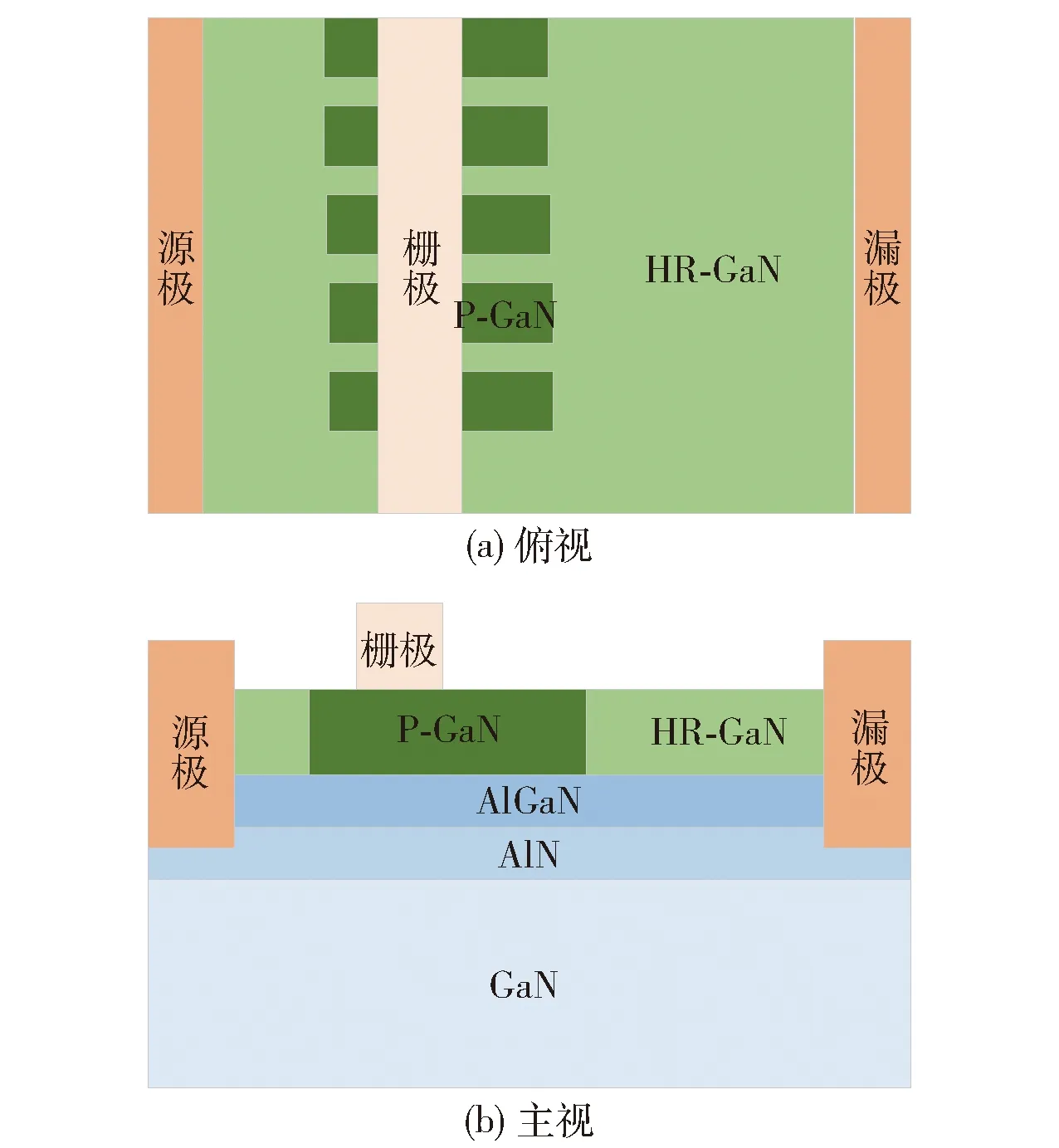

2021年,Wei等[28]提出横向耦合P-GaN栅(lateral couple P-GaN gate,LCPG)结构,该结构包括多个平行排列的P-GaN柱,它们由经氢等离子体处理的P-GaN(hydrogenated GaN,HR-GaN)间隔开,LCPG长度大于栅金属长度且与两侧源漏电极无接触,宽度与HR-GaN相同,如图11所示。此器件具备正的阈值电压(0.6 V),当P-GaN与漏极间距 10 μm时,漏极电流密度增至156 mA/mm,比传统P-GaN结构提升了87.9%,栅泄漏电流密度降低了89%,仅为1.4 nA/mm,同时,导通电阻降低,击穿电压提升,显示出优异的器件性能。

图11 横向耦合P-GaN栅结构HEMT器件结构示意[28]Fig.11 Schematic of the LCPG structure HEMT device[28]

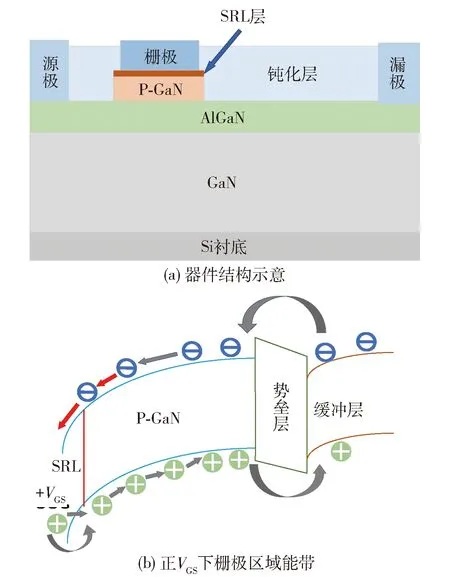

图12 具有SRL层的P-GaN栅结构HEMT器件结构及栅区域能带[29]Fig.12 Structure and energy band of gate region of P-GaN gate structure HEMT device with SRL layer[29]

2021年,Zhang等[29]为进一步提高栅极稳定性,在P-GaN栅表面增设一层氮氧化镓(GaON)作为表面强化层(surface reinforcement layer,SRL)。在正的栅偏压下,沟道中的2DEG会从AlGaN势垒层中溢出到耗尽区,并在电场中加速成为具有高动能的热电子,而GaON为纤锌矿结构且具有4.1 eV的宽带隙,展现出更大的共价键强度,可有效保护GaN层表面,防止这些热电子可能引起的共价键断裂。与无SRL层的器件相比,SRL结构P-GaN栅结构HEMT器件保持了正的阈值电压(1.4 V)和11 Ω·mm左右的导通电阻率,同时,在25 ℃和150 ℃时均将栅击穿电压从11 V提升至 13 V,使用寿命达10 a,故障率仅1%,最大适用VGS提升至 7.8 V,大幅提升了栅极可靠性与器件性能。

基于上述器件结构方面的优化措施,本文对优化过程中的目标优化参数及各自的优缺点进行了归纳总结和对比,如表2所示。

3 P-GaN栅结构HEMT器件制备工艺优化

器件的制备过程是否规范、制备条件是否合理都会影响最终所得器件的性能。对于P-GaN栅结构HEMT器件而言,帽层的刻蚀是最重要,也是最需要优化的工艺步骤。一直以来,刻蚀过程造成的材料损伤和表面缺陷都严重制约着P-GaN技术的发展。因此,目前制备工艺的优化主要针对P-GaN刻蚀工艺的刻蚀条件(刻蚀气体、掩膜等)以及刻蚀后的表面处理。

3.1 刻蚀气体及刻蚀掩膜优化

2013年,Takashi等[30]使用SiH4、N2O和NH3混合气体,在800 ℃条件下于P-GaN栅结构HEMT器件上气相淀积了100 nm厚的高温氧化物(high temperature oxide,HTO)钝化层,并对ICP刻蚀后的器件表面进行了10 min的NH3处理,所得器件获得了0.7 V左右的正阈值电压。NH3处理可以有效去除0.6 eV能量处的表面陷阱,SiO2钝化层处理可以有效去除0.4 eV能量处的表面态密度,从而使得电流崩塌得到抑制,ICP刻蚀带来的损伤也得以改善,如图13所示。图中Ev为价带顶对应的能级。

图13 有无NH3和SiO2钝化层处理的P-GaN栅结构HEMT器件能带[30]Fig.13 Band of P-GaN gate stucture HEMT device with/without NH3 treament and SiO2 passivation layer[30]

2018年,钱茹等[31]采用Cl2/N2/O2作为刻蚀气体(Cl2为刻蚀反应气体,N2为载气,O2用于实现自停止)对P-GaN进行ICP干法刻蚀,当气体流量分别为18、10、2 cm3/min时,获得了8 nm/min的刻蚀速率,刻蚀选择比达30,远大于SF6/BCl3作为刻蚀气体时的结果。同时,该气体能实现在AlGaN层的刻蚀自终止,因为O2与Al原子反应生成的Al2O3会对AlGaN形成保护层,该层氧化物作为绝缘栅介质不仅能抑制漏电,还避免了过刻蚀。

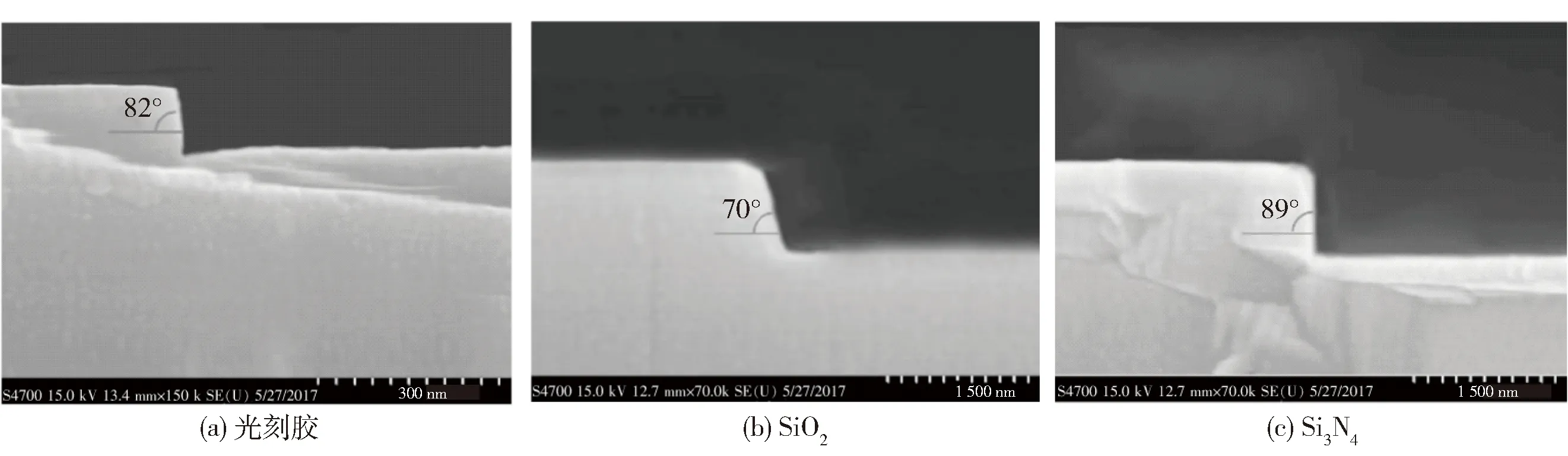

钱茹等[31]还在同一刻蚀气体下设置了不同刻蚀掩膜(光刻胶、SiO2、Si3N4),如图14中的扫描电子显微镜(scanning electron microscope,SEM)图像所示。由图可知,Si3N4掩膜的刻蚀效果最佳,所得P-GaN沟槽近乎垂直于水平面且光滑,无微沟槽产生,基于此条件制备的P-GaN栅结构HEMT器件栅极反偏电流降低了3个数量级,漏电极端关态电流降低了2个数量级,获得正阈值电压0.6 V,峰值跨导率36 mS/mm。

图14 采用不同刻蚀掩膜刻蚀后GaN沟道横截面的SEM图像[31]Fig.14 SEM images of GaN trenches cross-sections after etching with different etch masks[31]

3.2 刻蚀后表面处理

合理的表面处理能够修复势垒层中的界面态与浅能级N空位缺陷[2]。2008年,吕玲等[32]采用煮沸的NaOH溶液对刻蚀表面进行处理,并在样品表面生长电极,获得了较好的欧姆接触特性。2020年,西安电子科技大学的黄泽阳[33]对刻蚀后的P-GaN栅结构HEMT器件进行N2气氛下300 ℃、10 min的退火处理,发现器件IDmax增幅达到66%,方块电阻和欧姆接触电阻分别降低82%和73%,充分体现了退火处理对器件表面缺陷、损伤的修复及对直流特性的提升。2021年,为解决采用Cl2/N2/O2作刻蚀气体时Cl离子可能进入外延片并影响器件性能的问题,Niu等[34]在P-GaN刻蚀后先采用缓冲氧化物刻蚀剂处理2 min,然后在500 ℃条件下退火3 min,如此处理之后,样品中2DEG浓度和载流子迁移率的乘积能达到刻蚀前的93%,实现了较好的恢复。在此基础上制备的HEMT器件实现了正向的阈值电压(1.6 V),开关电流比达107,最大输出电流密度达153 mA/mm,整体性能较为优越。

针对上述器件制备工艺的优化方法,本文进行了归纳总结,如表3所示。

表3 器件制备工艺优化方法对比

4 挑战与展望

虽然P-GaN栅结构GaN基HEMT器件是目前最具前景的增强型GaN基功率器件,但其在结构和制备工艺优化方面仍存在一些局限。

4.1 挑战

通过对P-GaN栅结构GaN基HEMT器件结构和制备工艺的改进,器件性能已经取得了一定提升,但仍存在如下局限:

1) 针对器件材料层的优化虽具有相对高的工艺可行性,未来研究前景广阔,但此类方法难以在保持器件阈值电压的同时兼顾输出特性,所得器件普遍存在输出电流低的问题,不利于在高频高功率领域的应用。对此,应当进一步研究结构参数对器件性能的影响机制,慎重选取各层材料参数,比如:势垒层厚度、元素组分和帽层空穴浓度均不宜选取过大或过小的数值,设置大小适中的参数可在一定程度上缓和阈值电压稳定性与输出特性间的矛盾。

2) 与材料优化相比,针对器件结构的优化设计虽能调和器件阈值电压与输出特性间的矛盾,获得更优良的器件性能,但此类方法实施起来工艺难度较大,相应的器件设计工作也更复杂。针对这一问题,可通过科学选择制备工艺来降低制备难度,精简器件制造过程,比如使用ALD沉积法相较于PECVD法更易获得高质量钝化层,因此,在实际生产中选择ALD沉积法,可大大减少工艺失误率,降低工艺难度。

3) 针对制备工艺的优化在实际生产中容易实施,能明显改善P-GaN刻蚀造成的损伤,但却会导致器件的制备过程复杂化,不利于简化制备流程和控制制备成本。对此,可以尝试新的帽层处理方法,比如氢等离子体处理法,H原子注入P-GaN层后形成的Mg-H化合物可使栅极下方以外区域的P-GaN层高阻化,从而省去ICP刻蚀步骤[35]。

4.2 展望

本文对P-GaN栅技术未来的研究方向进行了展望,具体归纳为以下几点:

1) 探寻新的势垒层材料。通过在传统势垒层中引入Ⅲ族氮化物半导体材料来形成复合势垒层可实现器件电学特性的极大突破,因此,未来应着眼于Ⅲ族氮化物半导体的相关研究,从中探寻更加高效、易获取、低成本的半导体材料,最大程度利用此类材料的强极化效应,进一步提升器件击穿特性和输出特性。

2) 探究肖特基栅极结构。从总体和长远来看,肖特基栅器件在略微牺牲输出特性的情况下,能保持较高的阈值电压和栅极可靠性,这些特性有利于其在高频、高压领域的应用。因此,未来应以肖特基栅器件为研究重点,继续探究栅与帽层间接触机制的具体作用机理,进一步优化栅金属材料的选择,力求平衡输出特性、阈值电压和可靠性三者之间的关系,以获得器件性能的更大突破。

3) 优化钝化层质量。引入钝化层对器件电流崩塌能起到显著改善作用,保障器件在实际应用中的安全运行与优良特性,但钝化层淀积过程会增加器件的制备难度。因此,未来有必要继续探索钝化层的最佳淀积条件,简化淀积工艺,降低器件制造成本。同时,应扩大钝化层材料的选择范围,探寻性能更佳、成本更低廉的钝化材料,以获得高质量钝化层,保障器件电学特性。

4) 采用新型场板结构。对于传统结构GaN基HEMT器件中已有报道的台阶场板、多层场板等结构,应尝试将其引入P-GaN栅结构HEMT器件中,并通过进一步优化场板尺寸、场板材料和场板形态细化研究该结构作用机理,解决器件电学特性和微波特性无法兼顾的问题。

5) 探寻新型P-GaN掺杂剂。目前,对于P-GaN帽层的掺杂浓度仍缺乏有效的提高手段,在未来的研究中,除了继续优化Mg激活温度和帽层生长温度,还需要寻找一种在GaN材料中容易溶解且电离能较低的新型掺杂剂以代替二戊镁(Cp2Mg)。