采用射频直采技术的超宽带软件无线电平台*

2022-12-30孙友礼

丁 晟,孙友礼

(1.江苏信息职业技术学院 微电子学院,江苏 无锡 214153;2.江苏省专用集成电路设计重点实验室(无锡),江苏 无锡214153;3.无锡天宸嘉航科技有限公司,江苏 无锡214000)

0 引 言

1992年,Mitola博士[1]首次提出了软件无线电(Software Defined Radio,SDR)概念。软件无线电具备充分可编程能力,对信息可进行有效控制,同时覆盖多个频段,支持大量波形和应用软件,完美地契合了无线电技术的发展方向,被称为第三代通信技术。随着无线通信、雷达电子战、遥感测绘等军民用技术的发展,人们所应用的射频频谱越来越宽,一个设备所需要兼顾的功能越来越多,无线电设备对超宽带、可重构、多功能等需求日益增长[2]。

目前实现软件无线电主要是三条技术路线。一是基于传统超外差结构,利用分立器件,构建软件无线电系统[3]。这一方法可以获得优越的指标,但是大规模使用分立器件导致系统结构复杂,一致性较差,成本较高,体积重量较大,通用性较差。二是基于超外差结构,使用基于系统级封装(System in a Package,SIP)技术的射频集成电路SoC(System on Chip)芯片(例如ADI公司的AD9361)开发软件无线电系统[4]。这一方法集成度高,结构简单,技术实现难度低,易于实现小型化,但是支持的频段、带宽等指标受限于SoC芯片,灵活性和通用性不够,瞬时带宽较小。三是采用射频直接采样技术[5-6]。这一技术直接摒弃了传统超外差结构,采用高采样带宽的模数转换(AD)/数模转换(DA)芯片,对射频信号进行直接数字化,从而使AD/DA无限接近天线,真正意义上实现了软件无线电的核心思想。基于射频直采的软件无线电技术不再受超外差结构下的频段覆盖限制,可以满足日益增长的跨频段、超宽带需求,是软件无线电技术的终极发展形态。但是,受限于AD/DA芯片采样能力,射频直接采样技术还未能大规模应用于软件无线系统。

目前,AD/DA采样技术不断进步,GHz水平的采样器件正逐步成熟,例如ADI公司推出的12GSPS DA芯片AD9173、TI公司推出的3GSPS AD芯片ADC083000等。同时FPGA实时信号处理技术飞速发展,Xilinx公司推出的20 nm UltraScale系列FPGA能够高效完成各类并行化数字信号处理工作。射频直接采样技术的两大瓶颈正在被突破,其在软件无线电系统中的应用也受到了业界的普遍关注。

本文描述了一种基于射频直接采样技术的超宽带软件无线电平台的设计。该平台按照PXI(PCI extensions for Instrumentation)标准设计,能够适配PXI平台,驱动部分以LabviewCVI开发,具有较强的通用性。平台以DA芯片AD9173和AD芯片ADC083000为核心,直接采样率高达3 Gsample/s,在保证高质量信号的同时最大限度地提升了信号瞬时带宽。

1 硬件平台整体设计

本文所构建的软件无线电平台是以射频直接采样技术为核心的,包括PXI信号直接产生模块(PXI-DA)和PXI信号直接采样模块(PXI-AD)。两个模块的物理结构、硬件接口、通信协议、软件驱动等均满足通用PXI标准,能够兼容各种PXI系统,以实现较好的通用化。其中,PXI-DA模块基于宽带12 Gsample/s DA芯片AD9173设计,能 够 产生0.1~1.4 GHz射频信号;PXI-AD模块基于宽带3 Gsample/s AD芯 片ADC083000设 计,能 够 对0.1~1.4 GHz的射频信号进行采样和数字信号处理。整个硬件系统包括一个发射通道和一个接收通道(1T1R),收发系统瞬时带宽高达1.3 GHz,能够产生和处理0.1~1.4 GHz的射频信号。

1.1 PXI信号直接产生模块(PXI-DA)

PXI-DA模块按照3U PXI单槽模块标准设计。PXI-DA模块利用高性能FPGA产生宽带数字信号,通过JESD204b总线将宽带数字信号输入至高分辨率的DA芯片中,DA芯片直接产生射频信号,通过巴伦输出,完成射频信号产生的功能。PXI-DA模块具体原理框图如图1所示。

图1 PXI-DA模块硬件原理图

PXI-DA采用ADI公司的AD9173,作为直接信号产生的核心芯片。该芯片具有两个DA通道,本模块使用其中一条通道。每个DA通道对应4x JESD204b数字通道(lane)。AD9173的lane速率和采样率之间的换算关系如下:

式中:Ns为采样位宽;L为JESD204b传输lane的数量;M为DA通道数量;fs为基带采样率。

根据配置不同,AD9173总共可以工作在17种JESD204b模式下,每种模式都存在带宽、传输速率、通道数等的折中。在本设计中,最关键的指标是信号瞬时带宽,因此为了最大限度地提升信号瞬时带宽,PXI-DA采用了Mode-13模式,并将基带采样率fs设定为1.5 Gsample/s,同时在AD9173内部进行2倍插值,最终采样率达3 Gsample/s,模块的信号瞬时带宽确保大于等于1.3 GHz。在Mode-13模式下,Ns=16,L=4,M=2,fs=1.5 Gsample/s。根据公式(1),JESD204b总线速率(lane_rate)将达到15 Gb/s。

为了满足JESD204b总线速率的指标要求,在设计上必须考虑两个方面:在处理器件选型上必须优先考虑该处理器件是否具备15 Gb/s串行链路收发器;使用Rogers高速板材,并通过仿真确认PCB设计能够满足15 Gb/s的总线速率。

在处理器件选型上,PXI-DA模块选用Xilinx公司的XCKU060-2FFVA1156(后文简称KU060)。该器件具备28x GTH串行链路收发器,总线速率最高可达16.3 Gb/s。同时,该FPGA采用20 nm工艺制程,是成本、性能、功耗比最佳的FPGA之一。

在PCB板材方面,在JESD204b总线布线的表层和底层选用Rogers4350板材,中间层选用高速FR4板材。在完成PCB设计后,采用HFSS 15.0进行时域频域仿真(结果可用微信扫描本文OSID码查看),在15 Gb/s速率条件下,插入损耗最大为1.7 dB;输出眼高大于等于400 mV,满足AD9173设计手册要求。

JESD204b要求收发端的工作时钟保证严格的相位同步,因此,采用一颗多通道、低相噪的锁相环芯片HMC7044为PXI-DA模块提供相参时钟。HMC7044外挂一个超低相噪的压控振荡(Voltage Controlled Oscillator,VCO)芯片CVHD-950X。通过比较100 MHz输入时钟与VCO输出时钟之间的相位差,调节VCO输入电压,最终实现100 MHz输入时钟与VCO输出时钟相位完全一致,即同步相参。然后,使用VCO输出时钟,通过分频器和倍频器,产生所需要的各种时钟信号。

PXI-DA模块采用3颗电源管理芯片LTM4644,用以产生板卡各器件所需电源。3颗LTM4644输入均来自PXI接口的5.0 V:其中一颗LTM4644为KU060核心供电,0.95 V;一颗LTM4644为DDR4等外围器件供电,包括1.2 V/1.8 V/2.5 V/3.8 V;一颗LTM4644为AD9173和KU060的高速GTH串行器供电,包括1.2 V/1.0 V。

另外,PXI-DA模块采用Xilinx Aritex-7 50T低功耗FPGA(XC7A50T-2CPG236I)作为PXI接口处理芯片,采用4颗4 Gb DDR4作为KU060的外存空间,采用2颗BALUN芯片(TCM1-83X+)将单端射频信号转换为差分信号,采用一个缓冲器芯片(SN74LVC1T45)输出同步脉冲信号,采用Molex公司的87833-1420连接器作为JTAG调试接口。

微信扫描本文OSID码可查看PXI-DA模块实物照片。

1.2 PXI信号直接采样模块(PXI-AD)

为了保持设计的复用性,PXI-AD在主FPGA、PXI接口器件、时钟器件、DDR器件和电源管理芯片等方面与PXI-DA保持一致。PXI-AD的主FPGA为XCKU060-2FFVA1156,PXI接口芯片为XC7A50T-2CPG236I,主锁相环时钟芯片为HMC7044,DDR器件为4 Gb DDR4。电源管理芯片为LTM4644,两颗BALUN芯片为TCM1-83X+,buffer芯片为SN74LVC1T45,JTAG连接器为87833-1420。PXI-AD模块具体原理框图如图2所示。

图2 PXI-AD模块硬件原理图

PXI-AD采用TI公司的ADC083000作为射频直接采样芯片。根据奈奎斯特采样定律,最优的不折叠采样区间为0.1~1.4 GHz,瞬时带宽可达1.3 GHz。

采样时钟进入ADC083000后,一路进行同相缓冲送入AD coreA,另一路进行反相缓冲送入AD coreB。两个AD core的采样时钟保持严格的180°相位差,由此实现了两个AD core的交织采样。

同时,采样时钟经过二分频后,作为SDR(Single Data Rate)模式下的输出接口时钟;再经过一次二分频后,作为DDR(Double Data Rate)模式下的输出接口时钟。

当AD工作在3 Gsample/s采样率下时,其输入采样时钟为fclk=fs÷2=1.5 GHz。本设计AD输出接口采用DDR模式,因此DCLK频率为fDCLK=fclk÷4=375 MHz。AD LVDS输出接口(共32对)的总线频率为375 MHz,高速FR4板材完全可以满足要求。在layout布线上,需要确保AD LVDS输出接口和DCLK差分对保持严格等长。

为了尽可能复用设计,PXI-AD采用HMC7044作为1.5 GHz采样时钟的输入源。同时HMC7044再输出一路时钟至FPGA,以实现FPGA系统时钟与采样时钟相参,从而确保整个系统的同步性。

PXI-AD模块采用3颗电源管理芯片LTM4644,用以产生板卡各器件所需电源。LTM4644的输入电压为PXI接口的5.0 V。前两颗LTM4644的功能与PXI-DA模块一致,最后一颗LTM4644为ADC08300等供电,包括3.3 V/1.0 V。

微信扫描本文OSID码可查看PXI-AD模块实物照片。

2 FPGA固件平台设计

2.1 信号产生固件设计

信号产生固件部署在PXI-DA的主FPGA即KU060上,其整体逻辑框图设计如图3所示。

图3 信号产生固件总体逻辑框图

为了便于对AD9173、HMC7044进行控制,以及与PXI接口芯片进行UART通信,固件采用了Xilinx公司提供的MCU软核MicroBlaze。MicroBlaze的软件开发工作在Xilinx SDK平台中进行,称为PS部分;在Vivado平台下进行的开发,称为PL部分。

信号产生固件的核心是PL部分。本设计旨在开发通用化的软件无线电系统,因此,PXI-DA的主要功能是产生可由用户定义的各类矢量射频信号。射频信号可以由功率值A、中心频点fc、脉宽tPW、周期tperiod和基带矢量确定,其中,A、fc、tPW、tperiod这四个变量可以通过上位机配置确定,而基带矢量由用户定义的算法确定。另一方面,AD9173内部包含数字上变频算法电路,因此中心频点fc的调整可以通过配置AD9173来实现。综上所述,信号产生固件PL部分的核心功能是对基带信号进行功率调整和时域调制;实现JESD204b接口通信;实现与PXI接口芯片的UART接口通信;实现与AD9173和HMC7044的SPI接口通信;实现基带IP(Intellectual Property)容器电路,使用户可以在容器电路接口规范下任意开发专用的基带矢量算法。

为了完成上述功能,信号产生固件包括触发波形、功率调制、JESD204b、SPI和UART等IP模块。触发波形模块内部设计有一个计数器,将计数器的计数值与设定的脉宽/周期等信息做比较,从而调整输出信号的高低电平,由此产生了脉宽/周期可控的脉冲信号。该脉冲信号可作为时域调制信号输入至基带IP容器电路中。

所谓基带IP容器电路是一个外围接口固定并完全开放的IP核,其内部逻辑可由用户开发。本文采用Xilinx公司提供的System Generator工具设计了一个基带IP容器电路的开发模板。用户可直接在该模板下进行二次逻辑开发,从而使用户开发工作量大幅度简化,同时也实现了较好的灵活性。

本文在信号产生固件的基带IP内部开发了DDS(Direct Digital Synthesis)逻辑电路,可以产生点频信号、线性调频信号和相位编码信号。基带IP将输出I/Q复信号至功率调制模块中。功率调制模块内部包含一系列乘法器和截位单元,将设定的幅度值与I/Q复数信号直接相乘,然后进行截位,即可调整数字信号的输出功率。功率调制模块输出I/Q复信号进入JESD204b IP中。JESD204b IP是Xilinx的官方IP,可以将并行128位信号按照JESD204b协议通过GTH高速串行链路输出,最终送至AD9173芯片中。进入到AD9173的是基带I/Q复信号,通过SPI对AD9173进行配置后,可以将I/Q复信号与AD9173的内部数字本振进行混频并进行2倍内插,得到数字射频信号,再经过DA转换后可得到射频信号。该射频信号的中心频率可通过调整AD9173内部的数字本振信号频率设定。

HMC7044和AD9173的SPI配置都使用自主开发的SPI IP核实现。PXI接口芯片的UART通信使用Xilinx官方的UART IP实现,JESD204b则通过Xilinx官方提供的JESD204B IP实现。

PS与PL部分的交互是使用AXI(Advanced eXtensible Interface)总线完成。Xilinx提供了一套通用化的AXI总线接口代码模板,用户能够直接使用该模板完成基于AXI总线接口的各类IP开发,从而大大减少了工作量。本设计中的所有IP均采用该模板开发。

信号产生固件的PS部分主要实现五大功能:HMC7044的SPI配置;AD9173的SPI配置;与PXI接口芯片的UART通信;JESD204B的配置;算法模块的配置。

最终设计结果如图4所示。

图4 最终设计结果信号产生固件

2.2 信号采样固件设计

信号采样固件部署在PXI-AD的主FPGA即XKU060上,其整体逻辑框图设计如图5所示。

图5 信号采样固件总体逻辑框图

与信号产生固件一样,信号采样固件采用MCU软核MicroBlaze作为控制核心。因此,整个设计也分为PL部分和PS部分。

对于通用软件无线电平台而言,信号采样后,需要进行解调。其中,通用化的部分即通过数字下变频将载波信号解调,得到基带I/Q复信号,进入基带IP容器电路。本文在信号采样固件的基带IP容器电路中设计了一个信号脉冲描述字(Pulse Deion Word,PDW)测试逻辑电路。

当基带IP完成处理后,将处理完的信号或结果通过MIG模块缓存入DDR4 SDRAM中。当上位机需要读取时,通过PXI总线对PXI接口芯片发送指令,接口芯片将该指令通过UART串口发送至MicroBlaze。MicroBlaze进行指令转换后,通过AXI总线从MIG中将处理完的信号或结果读取出来,然后再通过UART串口返回至PXI接口芯片,PXI接口芯片再通过PXI总线返回至上位机。

MicroBlaze通 过 控 制SPI对HMC7044和ADC083000进 行 配 置,使ADC083000工 作 在3 Gsample/s采样率下,并且数字输出接口是DDR模式。当32组LVDS差分对和一组DCLK差分时钟送入FPGA后,采用Xilinx的iddr模块将DDR总线转换为单时钟沿的并行总线。考虑到实际PCB板上LVDS差分总线可能存在不等长的问题,设计中还采用了idelay模块对LVDS差分输入进行延迟控制。最终AD IP输出16相并口总线,每相表示一个采样时钟的采样值(8 b),时钟频率是187.5 MHz。

数字下变频是对AD采样信号进行两次混频滤波抽取的处理过程。一次混频频点是1/4采样率,滤波按照半带宽进行,然后进行二倍抽取。由于混频频点是1/4采样率,因此混频信号可简化为0,1,-1的序列组合,从而节省了乘法器和DDS资源。凡是被乘以0的信号采样点实际为后续二倍抽取时被抽取点,因此可以不用进入后续计算流程,从而节省一倍的逻辑资源。一次混频完成后,信号由实信号转换为I/Q复信号,且采样率降低一倍。然后进行二次混频,二次混频频点是“信号中心频率-1/4采样率”。上位机将中心频率下发至FPGA中,然后FPGA根据该中心频率产生数字本振,与I/Q复信号进行复乘,即完成了二次混频。二次混频结束后,信号转换为去载波的基带I/Q信号,可送入基带IP容器电路中进行用户自定义的信号处理工作。

本文中基带IP容器电路实现的功能是检测信号的PDW,即测试信号的中心频率、带宽、脉宽、周期、功率等5个值。由于信号的中心频率未知,因此将数字下变频模块中的二次混频部分屏蔽,即完成二倍抽取后直接将I/Q复信号送入基带IP中。对送入基带IP容器电路的信号进行I部和Q部的平方和操作,求得信号的实时功率。将实时功率与一个阈值进行比较,如果高于阈值则输出高电平,低于阈值则输出低电平,即数字检波。然后对检波后信号进行周期计数检测,完成脉宽和周期的测试。用检波后信号对实时功率进行提取,得到峰值功率,完成信号的功率测试。另一方面,利用检波信号,提取输入信号的有效样本,然后对样本信号进行快速傅里叶变换(Fast Fourier Transform,FFT),再对FFT结果进行周期计数检测,可完成中心频率和带宽的测试。

信号采样固件的PS部分主要实现四大功能HMC7044的SPI配置;AD083000的SPI配置;与PXI接口芯片的UART通信;算法模块的配置。

最终设计结果如图6所示。

图6 信号采样固件设计结果

3 上位机软件设计

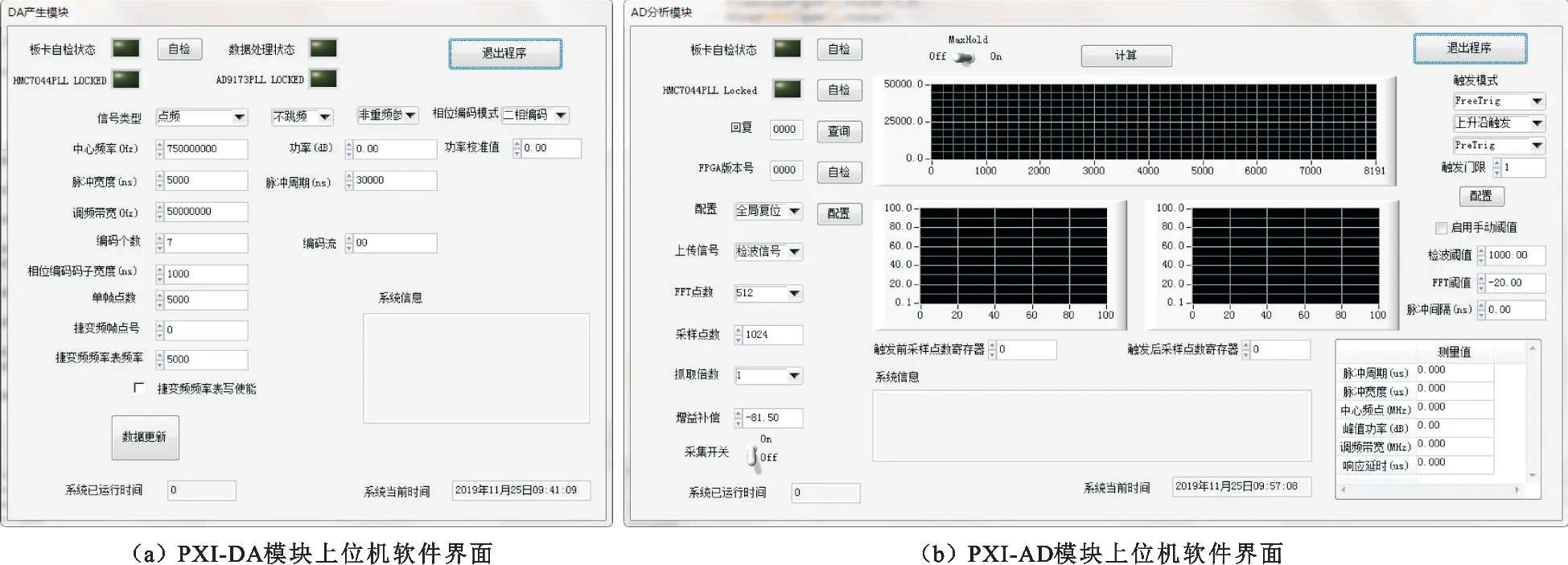

平台上位机软件是基于Labwindows/CVI开发平台来进行的,通过NI-VISA开发并建立与PXI通信接口,通过在模块驱动程序中配置PXI模块的信息参数,完成对PXI模块的指令设定。PXI-DA/PXI-AD模块内部的PXI接口芯片将PXI指令发送至KU060中。KU060控制内部各IP工作,完成系统功能。软件界面如图7所示。

图7 软件界面

4 系统验证与测试

为了验证本系统,采用自回环方式进行测试。首先PXI-DA模块产生脉冲点频、脉冲线性调频等信号,并使用频谱仪、示波器等进行测试,验证PXIDA的性能;然后将PXI-DA产生的射频信号送入PXI-AD模块,使用PXI-AD模块检测该信号的PDW,并将PDW结果与频谱仪、示波器等通用仪器测试结果比较,以验证系统性能。

4.1 PXI-DA射频信号产生测试

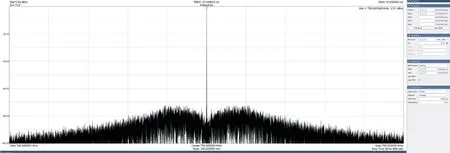

通过控制上位机软件,使PXI-DA产生0.1~1.4 GHz的各类信号,主要包括点频连续波信号、大带宽脉冲线性调频信号、相位编码信号。点频连续波信号主要用于测试PXI-DA的信号产生质量,如图8所示。

图8 PXI-DA产生750 MHz窄带频谱

在SPAN设定为100 kHz、RBW设定为10 Hz的情况下,可以看到信号功率为-2 dBm,近端杂散点最高为-70 dBm。频谱仪测得信号频率为750.000 045 MHz,频率精度优于10-6×中心频率。

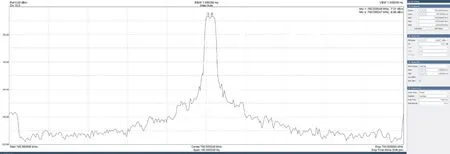

使用频谱仪MAX HOLD功能,通过控制上位机,先后设定频率为750 MHz和751 MHz,所得结果如图9所示。

图9 频率步进测试

图9出现两个明显峰值点,且峰值点频率相差1 Hz,因此表明PXI-DA频率步进可以达到1 Hz。

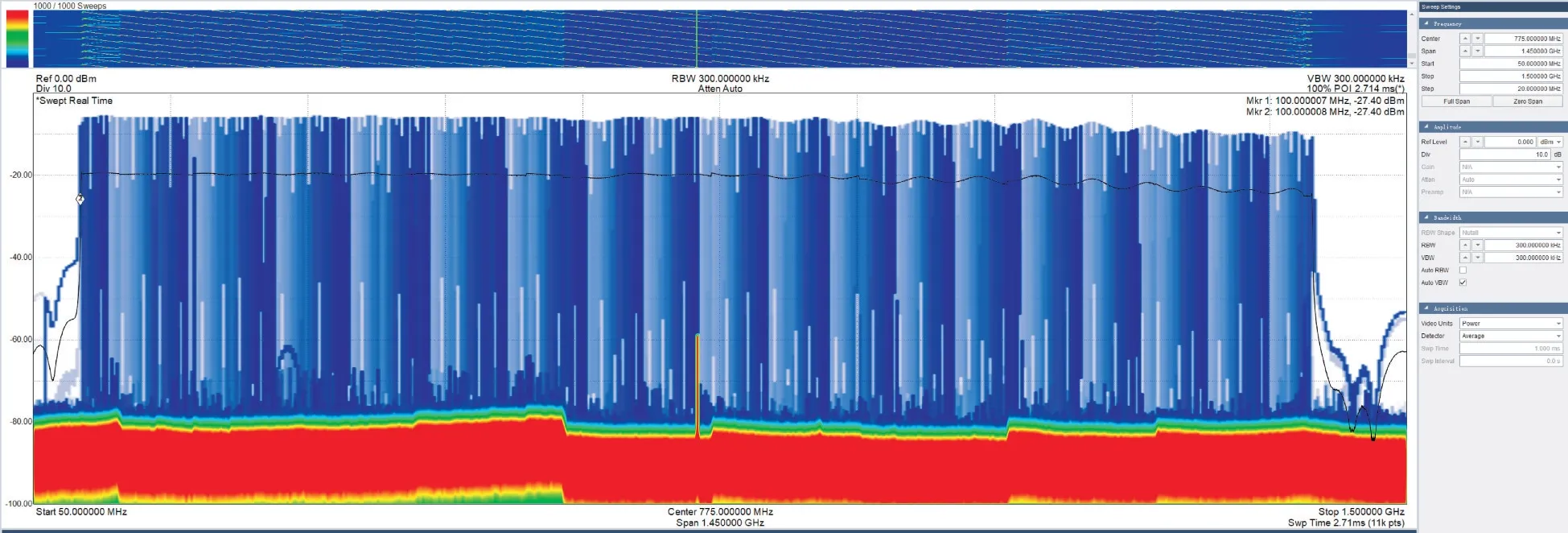

控制上位机,使PXI-DA产生1.3 GHz带宽的脉冲线性调频信号,以验证其最大瞬时带宽能力,所得结果如图10所示。

图10 PXI-DA信号瞬时带宽测试

通过频谱仪实时频谱分析可知,PXI-DA产生1.3 GHz线性调频信号,证明该模块瞬时带宽达到1.3 GHz。

控制上位机,使PXI-DA产生相位编码信号,以验证其脉内信号调制功能,所得结果如图11所示。

图11 PXI-DA相位编码测试(红色框内为相位翻转处)

通过示波器,可观察到PXI-DA产生四相编码信号,根据设定的编码形式,信号的相位按周期翻转。

4.2 PXI-AD射频信号采样测试

将PXI-DA产生的信号送入PXI-AD模块中,利用PXI-AD的PDW测试功能进行检测。

控制上位机使PXI-DA产生脉冲点频信号,频率为750 MHz,脉宽为500 ns,周期为2 μs,峰值功率为2 dBm,PXI-AD对其进行测试,结果如图12所示。

图12 针对脉冲点频的PDW测试

由图12可知,PXI-AD所测结果与PXI-DA设定结果一致。

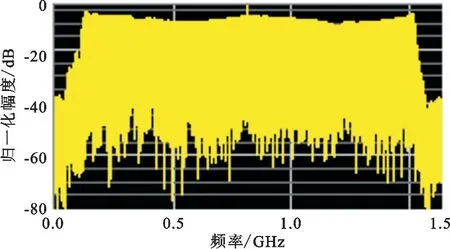

控制上位机使PXI-DA产生1.3 GHz脉冲线性调频信号,利用PXI-AD对其进行采样,并完成FFT,以验证PXI-AD瞬时采样带宽能力,所得结果如图13所示。

图13 PXI-AD满带宽采样能力测试

由图13可知,PXI-AD具备1.3 GHz的瞬时带宽采样能力。

5 结 论

本文利用射频直接采样技术构建了超宽带软件无线电通用化平台。该平台按照PXI标准设计,能够适配PXI平台,驱动部分以Labwindows/CVI开发,具有较强的通用性。平台以DA芯片AD9173和AD芯片ADC083000为核心,直接采样率高达3 Gsample/s。在保证高质量信号的同时,最大限度地提升了信号瞬时带宽。经过测试,平台瞬时工作带宽达到1.3 GHz,信号频率精度优于10-6×中心频率。平台使用FPGA IP化开发理念,将FPGA内部开发接口通过IP容器电路的方式开放给用户,使用户可以在不关心底层硬件设计的基础上完成软件无线电专用功能的开发。本文的工作进一步验证了射频直接采样技术对于软件无线电的重要意义。随着AD/DA采样带宽的提升,射频直接采样可进一步推动软件无线电技术的发展。