5G低轨卫星两步随机接入方案及其FPGA实现*

2022-12-30崔高峰王卫东

梁 震,崔高峰,王卫东

(北京邮电大学 电子工程学院,北京 100876)

0 引 言

卫星通信作为地面通信系统的补充,以其覆盖范围广、通信距离远、抗灾害损毁性强等特点得到广泛应用。低轨(Low Earth Orbit,LEO)通信卫星由于运行在低轨道,相对于高轨(Geostationary Earth Orbit,GEO)通信卫星具有传输损耗小、通信时延短等优点。地面5G与卫星通信的融合发展,将极大地促进空天地一体的网络体系建立,为网络边缘用户提供更优质的广播服务。与地面移动通信系统相比,低轨卫星系统受限于星地传输往返时延大、星上处理能力差的问题,随机接入、多址接入、频偏估计等地面5G关键技术在5G低轨卫星系统还需做出适应性改变。

用户设备进行上行传输前,需要实现上行传输时间同步,这样才能调度上行正交同步资源。随机接入信道作为非同步用户设备和5G上行无线接入的正交传输方案的接口扮演了关键角色。目前卫星通信中采用的随机接入机制仍然是LTE中传统的四步随机接入方案,在用户和基站之间发送四次消息才能建立连接。然而由于星地链路之间的距离较长,对于LEO通信卫星,距地面高度最大为1 500 km,完成一次双向通信需10 ms。如果在LEO卫星通信系统中继续使用传统的随机接入体制,会造成较大的接入时延,增大星地之间的链路开销。

为了实现星地之间低时延、高效率的用户接入,目前已有文献对卫星通信系统下的上行传输进行了研究。文献[1]对基于5G的低轨卫星随机接入技术进行了研究,提出了卫星场景下的前导设计方案,在满足较大时延的条件下对抗多普勒频移也有优异的性能。对于低轨卫星通信系统发送信号时延大检测难度高的问题,文献[2]中提出了一种基于MRLS的前导检测系统,减少随机接入流程实现快速检测。文献[3]提出了一种基于随机交错多路复用的随机访问结构,提高了卫星物联网的吞吐量。文献[4]研究了多个用户同时发起随机接入并发生碰撞下的检测算法,保证多用户的有效接入。对于卫星系统中的多普勒频移,文献[5]提出了一种基于离散傅里叶变换(Discrete Fourier Transform,DFT)频谱分析方法,在卫星系统中频偏较大的情况下也可以较好地得到TA估计。3GPP目前正在积极推进两步随机接入方案[6],将LTE传统的四步接入方案简化为两步,用户和基站仅需两次消息传递即可完成接入,极大降低接入时延,但是尚未考虑将两步随机接入过程应用在卫星通信系统中。

本文对低轨卫星系统下的两步随机接入技术进行研究,对信道结构、前导序列设计、数据映射关系进行了设计。对于多用户同时接入数据碰撞的情况,采用稀疏码分多址接入(Sparse Code Multiple Access,SCMA)。在两步随机接入FPGA实现中,针对传统MPA算法乘法运算多、迭代过程处理时延长的问题,提出了基于FPGA的节点并行快速迭代更新的MAX-Log-MPA接收机,牺牲一定芯片内存来换取低处理时延。

1 两步随机接入信道结构设计

1.1 随机接入过程

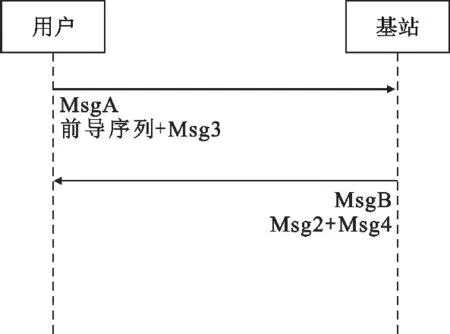

如图1所示,在两步随机接入过程中,前导序列传输与Msg3消息被定义为MsgA消息,由用户侧发送到基站侧,Msg2与Msg4定义为MsgB消息,由基站侧发送给用户。与四步随机接入相比,两步随机接入可以有效降低延迟以及信令开销。

图1 两步RACH示意图

用户发给基站的MsgA消息包括前导序列以及数据两部分,前导序列和数据通过时分复用发送,MsgA的信道格式如图2所示。物理随机接入信道(Physical Random Access Channel,PRACH)中循环前缀(Cyclic Prefix,CP)的作用是对抗实际环境中的多径干扰,保护间隔的作用是调整往返传播时延。在前导序列和数据部分预留一定时间间隔有利于接收机检测发送的前导序列,并进一步解调发送的数据。

图2 两步随机接入MsgA信道结构

1.2 msgA PRACH设计

有关卫星通信系统前导序列的设计,目前地面5G前导序列多由0.8 ms的ZC(Zadoff-chu)序列以及其多段级联构成。考虑低轨卫星星地最大往返时延、高速运动产生的多普勒频偏以及与地面5G的融合,采用如图3所示的级联前导序列,前导序列由5段长度为0.8 ms的ZC序列级联而成。PRACH信道在时域上占用传输无线帧的前5个子帧。

图3 PRACH前导序列结构

1.3 MsgA PUSCH设计与映射关系

MsgA PUSCH设计包括时频结构、导频位置、映射图样等[7-8]。对MsgA的设计既要考虑减小不同用户数据碰撞的概率还需要考虑提高频谱利用率。occasion的定义为可用于发送前导序列或者用户数据的时频资源。划分少的occasion虽然有着较高的频率利用率,但是用户碰撞概率变大,解码效果降低;划分多的occasion可以有效降低用户碰撞概率,保证接入成功率。对于多用户数据发送碰撞,对用户分配不同的稀疏码字实现SCMA[9]调制。因此,将MsgA PUSCH资源划分为6个PUSCH occasion,每个occasion频域上占用1个PRB,如图4所示。

图4 MsgA PRACH与PUSCH资源映射示意图

为了避免数据的盲解码,本文将随机接入过程中所有可能的64个前导码与其对应MsgA PUSCH资源的映射关系进行设计,occasion 0~4对应12 个前导码,occasion 5对应4个前导码。同一occasion中的前导码对应数据映射到4个不同的DMRS index,每个index有4个或1个前导码对应的PUSCH数据进行复用。

2 系统模型与检测算法

在卫星场景下的上行随机接入过程包括一个LEO卫星N与个用户,N≥1。N个用户采用两步随机接入向低轨卫星发出上行,不同用户间的MsgA PUSCH分配不同的稀疏码字。本文设计的两步随机接入系统模型如图5所示。

图5 两步随机接入系统模型

在上行接入随机过程中,用户根据索引值与循环移位值生成ZC序列,经过DFT变换、子载波映射、快 速 傅 里 叶 逆 变 换(Inverse Fast Fourier Transform,IFFT)变换等生成前导码,用户MsgA PUSCH数据经过信道编码、加扰、SCMA调制、资源映射以及OFDM调制生成MsgA数据,完成两步随机接入过程中的MsgA信号发送。在接收侧,先对前导码进行检测,在前导码成功被检测到时,根据检测到的索引对MsgA数据进行检测,接收框图如图6所示。对于SCMA调制,需要用到MPA检测算法。

3 FPGA设计与实现

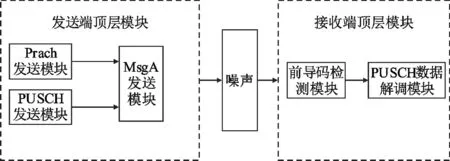

在两步随机接入FPGA实现中,低复杂度、低处理时延是研究的重点。FPGA收发模块框图如图7 所示。

图7 两步随机接入FPGA收发框图

发送端顶层模块包括MsgA PRACH发送模块与MsgA PUSCH发送模块,接收端顶层模块包括前导码检测模块与MsgA PUSCH数据解调模块。在两步随机接入过程中,PUSCH数据解调中SCMA接收机是设计的重点。MPA解调算法需要在用户节点与资源节点之间将消息概率迭代更新,在FPGA实现中运算复杂度高、处理时延长,因此本文提出了节点并行快速迭代更新的低时延SCMA接收机。

3.1 节点快速收敛的并行处理SCMA接收机

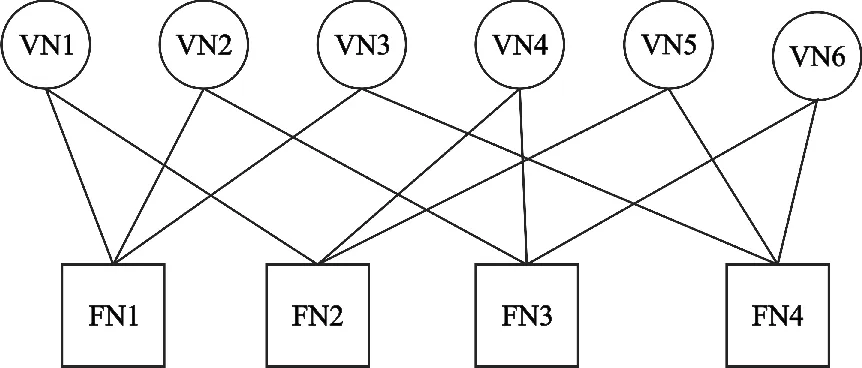

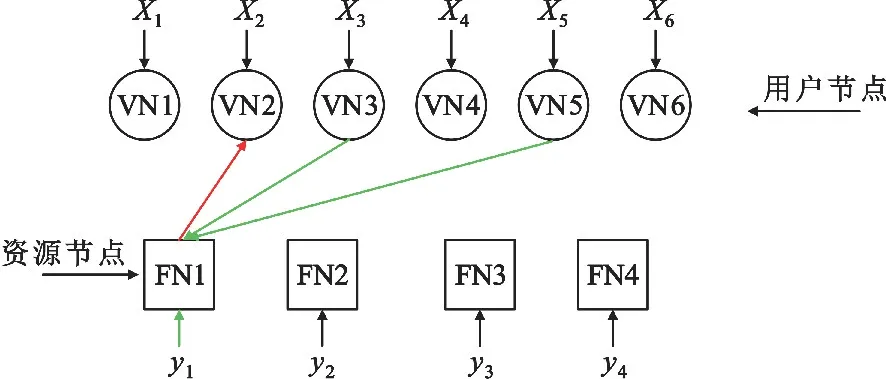

典型SCMA调制系统的因子图如图8所示,图中VN代表接入用户,FN表示频域资源。

图8 SCMA调制因子图

MPA算法利用了码本的稀疏性,极大降低了重叠数据检测的复杂度。MPA算法的具体流程如下:

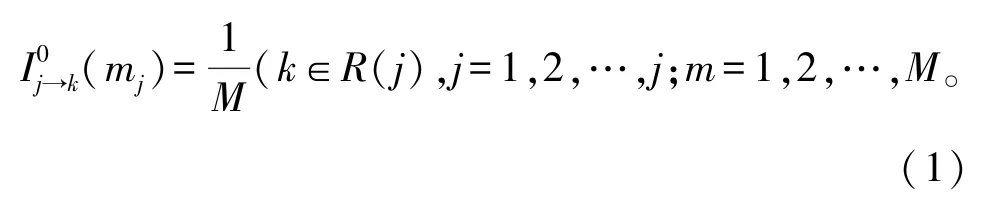

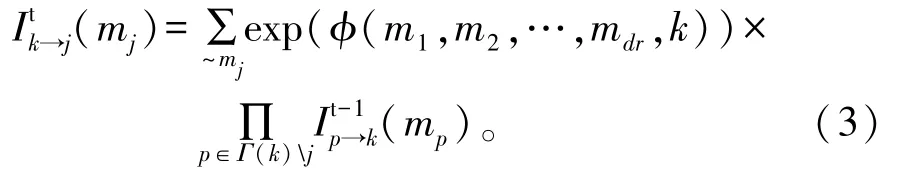

首先,根据因子图V(k)定义为连接到第K个RN的所有VN的集合,R(j)代表连接到第j个VN的所有RN的集合,代表第t次迭代过程中数据块节点j到频域资源节点K的消息。MPA检测的具体译码过程如下:

Step1初始化所需要的信息。

在解码模块开始迭代式,需要输入码字的先验概率并计算出接收信号和叠加码字之间的差,称其为残差概率。MPA将各个用户发送的所有码字设置为相同的概率:

式中:mj表示用户j的第m个码字。

残差概率用Φ(m1,m2,…,mdr,k)来表示,具体公式如下:

式中:yk表示频域资源节点k的接收信号;C(k,j)(mj)表示数据j使用第m个码本在频域资源节点k上的复数符号。

Step2更新FN和VN的消息直到达到最大迭代次数。

FN的迭代更新过程如图9所示,FN1传递给VN2的消息,需要得到资源节点FN1所有连接的其他用户节点VN3与VN5的信息。同样,资源节点FN1传递给VN3与VN5的过程与VN2类似,具体公式如下:

图9 FN到VN的迭代更新过程

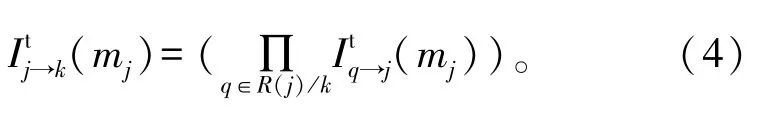

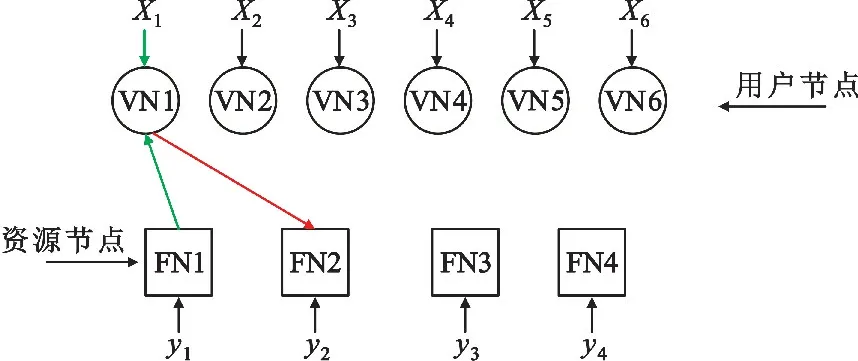

所有FN节点更新结束后,将进行VN节点的更新过程,具体迭代更新如图10所示。用户节点VN1传递到FN2的消息,只需要传递外部消息,具体公式如下:

图10 VN到FN的节点更新

接着进行归一化操作。经过反复迭代,使得信息收敛或直到最大迭代次数,最后的值就是MPA对该码字的概率估计。

Step3迭代完成后,将计算各个数据块的码字概率,将该用户块节点所连的频域资源节点的信息相乘即可得到最终的码字概率,具体公式为

Step 4计算待解码字中每个比特的对数似然比。

定义为

这就是SCMA系统中MPA算法的检测过程,之后将LLR值作为信道译码输入进行译码。

FPGA 实现中,低时延与低复杂度是研究的重点,虽然使用对数域的算法Max-Log-MPA[10]可以将乘法域的运算转化到加法域且避免了e指数运算,运算复杂度大大降低,但是仍然存在节点信息传递时延较大的问题。为此,本文提出了一种节点快速收敛的并行处理SCMA接收机。

在运行Max-Log-MPA对SCMA调解进行解调时,可以观察点一些底层资源节点在进行几次更新之后,概率信息就基本保持不变实现收敛,另一些资源节点则需要更多的迭代次数才可以实现收敛。在FPGA中,已经收敛的资源节点继续进行迭代更新只会无意义地占用有限的芯片内存资源。因此对于已经收敛的资源节点,在后续的迭代中将不再更新释放掉内存,节省芯片资源。

收敛性是迭代算法的一个重要性质,然而在Max-Log-MPA算法中对收敛性的证明是及其困难的。在仿真中发现资源节点概率信息的变化量小于10-3后就趋于不变。基于此,对于判断节点是否收敛,将两次连续迭代输出过程中资源节点概率信息的差作为判断收敛的标准,当连续迭代之间的差值小于接收机定义的阈值α(10-3),此资源节点将不在更新。

如图11所示,在FN到VN的传递过程中,以FN1节点向VN3节点、FN2节点向VN3节点进行消息传递更新进行分析。FN1向VN2节点传递消息,需要来自节点VN2、VN5的概率消息P1与P2,FN2向VN3节点传递消息,需要来自节点VN1、VN6的概率消息P3和P4。虽然资源节点FN1与FN2都与数据节点VN3进行消息传递,但是在计算过程中各自需要计算的消息概率是独立的,互不影响。同理,在FN向VN的传递过程中,不同的资源节点在与其相连的数据节点进行消息更新传递中,只与其相连接用户节点传递来的消息有关,与其他资源节点无关,相互独立,因此在FN到VN的消息传递过程中,所有资源节点可以并行进行消息传递计算。同理,VN向FN的更新也可进行并行计算。

图11 FN到VN的迭代更新过程

在并行计算过程的初始时刻,所有节点并行计算与其所连接的第一个用户节点传递的消息,在经过64个时钟周期计算完毕后,再依此计算与其所连接的第二个与第三个用户点传递的消息,这样经过192的时钟周期即可完成所有FN到VN的更新传递。并行计算需要将每个节点向其所连接用户节点传递的消息概率存储在一个RAM中,即以FPGA内存空间换取低处理时延。

3.2 低时延SCMA接收机FPGA实现

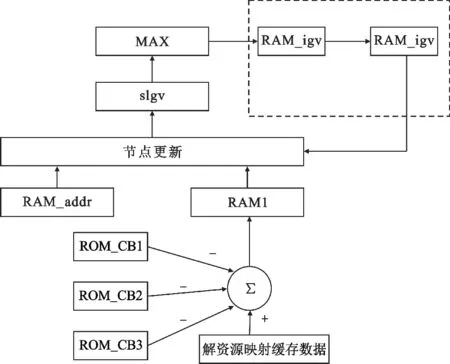

SCMA接收机使用的消息传递算法就是计算每个比特的后验概率,在迭代过程中消息概率在用户节点与资源节点之间迭代更新。SCMA接收机设计框图如图12所示。

图12 SCMA接收机设计框图

对于公式中(2)中的码字,在计算前需要定义一组ROM,将码字存储起来。根据公式(2),对于每组复数数据的实部与虚部,在计算完毕后需要求距离的平方之和,再进行取相反数操作。

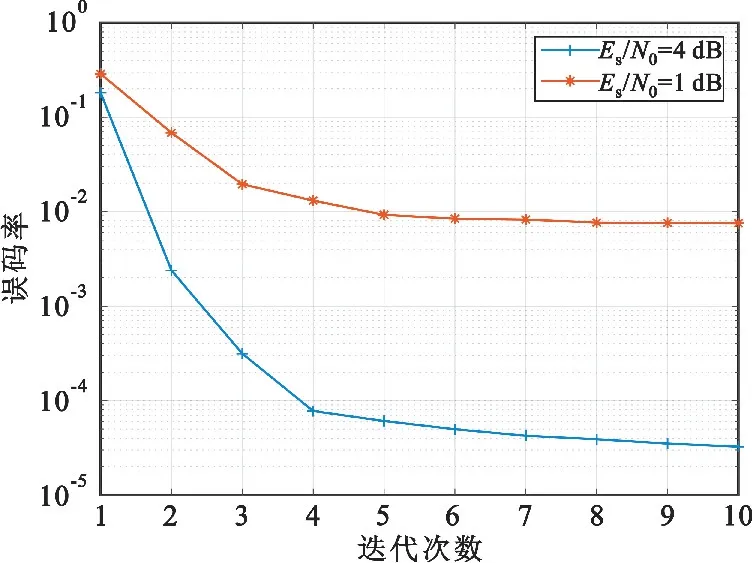

MPA迭代次数对SCMA接收机性能有着重要的影响,迭代次数小SCMA接收机无法正确解码数据,迭代次数多FPGA资源消耗较多,因此需要实现迭代次数、解码性能与系统资源的平衡。图13为Es/N0=4 dB与Es/N0=1 dB时迭代次数对误码率影响的仿真图。

图13 迭代次数对SCMA解码的影响

从图13可以看出各个信噪比下的误码率曲线走势相同,在迭代次数大于7以后,误码率不会明显下降,综合考虑误码率与FPGA资源,令迭代次数为7。

定义两组存储器组RAM_Igv与RAM_Ivg来存储用户块节点与频率资源节点在某次迭代过程中的概率信息。对于节点的初始化,在MAX-Log-MPA中,码字先验概率为ln(1/4),将未开始迭代前的RAM_Igv节点概率初始化为ln(1/4),RAM-Igv节点初始化为0。

对于残差概率传输模块的数据,在节点更新前定义一组RAM1用来存储残差数据。在Igv的更新过程中,在Max-Log-MPA算法中,Igv的每次迭代,需要将从RAM1中读出相应地址的数据,再从RAM-Igv中读出相应数据做相加运算得到中间变量slgv,然后经过Max计算得到Igv。对于Igv,需要在16个可能的结果中取出最大值得到,所以系统需要16个时钟才能输出一个计算结果。各个节点采用并行计算,可以大幅度降低处理时延。Igv迭代过程中,为了便于读取RAM1中的数据,将需要读取的地址提前写入一组存储器RAM2,在计算过程中,由RAM2读出所需的地址,Igv即可在对应的时钟下捕捉到RAM1中的数据进行计算。在Igv更新完毕后对Ivg进行更新。用户节点与资源节点的迭代更新FPGA设计如图14所示。

图14 节点迭代更新的FPGA设计

4 仿真结果

本文采用虚警和漏检概率对5G低轨卫星两步随机接入中的MsgA PRACH的检测性能进行评估,采用误码率对MsgA PUSCH的解调性能进行评估。在接收端,当前导码成功被检测到才会进行误码率的计算统计。仿真参数配置如表1所示。

表1 仿真配置表

图15是在AWGN信道与卫星信道无频偏的情况下,漏检概率与虚警概率和信噪比的关系图。

图15 MsgA PRACH参数仿真图

从图15中可以看出,在AWGN信道与卫星信道下,都可以在Es/N0=-16.5 dB时满足最低1%的漏检率要求,并且在漏检概率满足1%要求的情况下虚警概率也可以达到最低0.1%的要求[11]。仿真结果表明,所设计的5G低轨卫星MsgA PRACH参数可以满足3GPP协议规定的PRACH信道最低1%漏检和0.1%虚警概率的要求。

图16仿真分析了单用户发起接入与多用户同时接入的误码率,同时接入的用户数量为6,6个用户的数据在4个PRAHC occasion中复用。5G中数据传输均采用LDPC码,本文5G低轨卫星两步随机接入数据传输也采用LDPC码,当单用户发起两步随机接入,AWGN信道下传统的OFDM方案在Es/N0=0.2 dB时误码率达到10-4,卫星信道下在Es/N0=0.8 dB附近时误码率达到10-4。多用户同时发起随机接入,AWGN信道下可在Es/N0=3.9 dB时误码率达到10-4,卫星信道下可在Es/N0=4.6 dB时误码率达到10-4。与单用户接入相比,多用户接入在Es/N0=4 dB以后即可拥有优异的误码率性能。

图16 MsgA PUSCH误码率

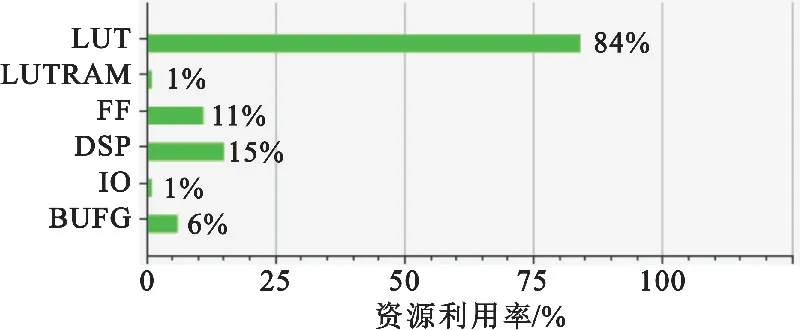

对于两步随机接入的FPGA实现仿真结果,本文从资源利用率情况、SCMA译码运算量以及FPGA处理时延来评估。

按照第3节的FPGA收发模块设计,使用Verilog语言编写RTL代码,选用artix-7 系列的xc7a100tcsg324-1 器件进行综合,两步随机接入资源使用情况如表2和图17所示。

表2 FPGA资源利用情况

图17 FPGA资源利用率

表3为SCMA接收机一次迭代中(输出所有用户节点的12 b消息)的计算复杂度,N代表迭代次数。在使用Log-Max-MPA算法的接收端,迭代过程中的乘法都被转化为加法运算,大大减少了计算复杂度,同时采用并行计算,有效降低了处理时延。接收端从接收到前导码到MsgA PUSCH数据解调成功,在系统时钟为50 MHz的情况下,解调总时延为677.43 μs。

综上所述,本文研究的5G低轨卫星两步随机接入方案在发送前导检测成功率和数据误码率性能方面均有良好的性能,从而保证了接入成功率。FPGA接收机设计与传统接收机相比,同时可供接入的用户数量更多;节点并行迭代更新的SCMA接收机,在解调中只存在加法和求最大值运算,在不增加运算复杂度的基础上,采用节点并行处理,将迭代处理时延大大降低。

5 结束语

本文提出了低轨卫星系统下的两步随机接入信道设计方案,对前导序列格式以及与数据映射关系进行了设计,在FPGA上对两步随机接入进行了实现,并提出了节点并行处理的低时延SCMA接收机。仿真结果表明,本文提出的设计方案能够实现用户发起的两步随机接入过程,不仅可以降低用户数据碰撞概率提高频谱利用率,而且数据部分有较好的误码率性能,FPGA接收端芯片资源利用率、处理时延都有优异的表现。仿真结果验证了所设计两步随机接入方案在低轨卫星系统场景下应用的可行性。未来将对低复杂度低时延的非正交多址接入FPGA实现做进一步研究。